一、項目背景與核心目標

PULP(Parallel Ultra Low Power)是由瑞士蘇黎世聯邦理工學院(ETH Zurich)和意大利博洛尼亞大學(University of Bologna)于2013年聯合發起的開源多核計算平臺。其核心目標是為物聯網(IoT)終端節點和邊緣計算設備提供低功耗、高性能的嵌入式解決方案。通過硬件與軟件的協同優化,PULP在毫瓦級功耗下實現高效并行計算,滿足傳感器數據流處理、實時信號處理等需求。

*附件:pulp-master.zip

二、技術架構解析

1. 硬件設計

2. 內存與總線

3. 低功耗設計

- 動態電壓頻率調節(DVFS) :根據負載調整電壓和頻率。

- 電源門控 :關閉閑置模塊以節省功耗。

- 事件驅動中斷 :減少輪詢開銷,典型功耗低于10mW。

三、軟件生態與開發工具

1. 操作系統支持

- FreeRTOS :輕量級實時系統,適用于資源受限設備。

- Nuttx :支持文件系統、網絡協議棧,適合復雜嵌入式應用。

2. 工具鏈

- RISC-V GCC工具鏈 :支持RV32IMC擴展指令編譯。

- Pulp-SDK :提供硬件抽象層(HAL)、驅動庫及調試工具。

- 仿真與驗證 :基于Verilator和ModelSim的RTL仿真環境,支持FPGA部署。

3. 應用開發

- 機器學習 :通過HWPEs加速CNN推理,支持TensorFlow Lite模型部署。

- 信號處理 :優化FFT、濾波器算法,適用于生物傳感和音頻處理。

四、典型應用場景

- 物聯網終端 :處理多傳感器數據流(如加速度計、麥克風陣列),適用于智能農業、工業監測。

- 邊緣AI :GAP8處理器搭載神經處理器(NPU),實現本地化圖像識別與語音處理。

- 醫療設備 :低功耗ECG監測、可穿戴健康設備,支持長時間運行。

- 自動駕駛感知 :實時處理激光雷達點云數據,優化路徑規劃。

五、開源生態與合作模式

- 管理架構 :由lowRISC基金會主導標準化,聯合西部數據、新唐科技等企業推動商業化。

- 社區貢獻 :

- 衍生項目 :

六、挑戰與未來展望

- 技術挑戰 :

- 制造依賴 :部分工藝依賴臺積電55nm/28nm制程,尚未完全實現開源流片。

- 生態碎片化 :需與Arm TrustZone、Intel SGX等閉源方案競爭,推動RISC-V軟件工具鏈統一。

- 未來方向 :

- 異構計算 :整合CPU、GPU、NPU,支持更復雜的AI推理任務。

- 車規級應用 :拓展至車載ECU和自動駕駛芯片,滿足功能安全標準(ISO 26262)。

- 量子安全 :研究抗量子攻擊的硬件加密模塊。

七、總結

PULP通過開源硬件設計和 模塊化架構 ,成為物聯網與邊緣計算領域的標桿平臺。其多核并行、低功耗特性在AIoT場景中展現出顯著優勢,未來有望通過生態擴展和技術迭代,推動RISC-V在工業與消費電子中的普及。

參考GitHub

https://github.com/pulp-platform/pulp

PULP平臺

PULP (Parallel Ultra-Low-Power) 是一個開源多核計算平臺,是蘇黎世聯邦理工學院和博洛尼亞大學之間持續合作的一部分 - 始于 2013 年。

PULP 架構針對需要靈活處理多個傳感器生成的數據流的物聯網終端節點應用,例如加速度計、低分辨率攝像頭、麥克風陣列、生命體征監測器。

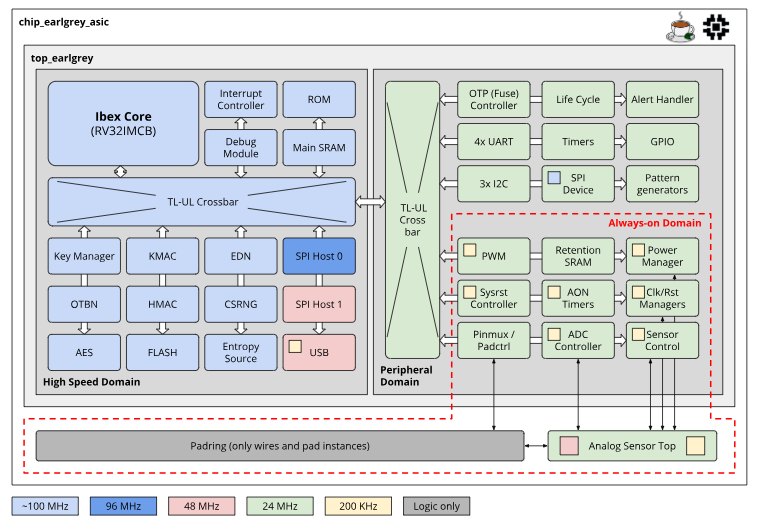

PULP 由先進的微控制器架構組成,在完整性和復雜性方面比 PULPino 領先了一大步,負責自主 I/O、高級數據預處理、外部中斷,并包括一個緊密耦合的處理器集群,計算密集型內核掃描從主處理器卸載到該集群。PULP 架構包括:

- RI5CY 內核或零 riscy 內核作為主內核

- 自主輸入/輸出子系統 (uDMA)

- 新的內存子系統

- 支持硬件處理引擎 (HWPE)

- 新的簡單中斷控制器

- 新外設

- 新的并行計算集群

- 新系統 DMA

- 新建事件單元

- 新 SDK

RISCY 是一個有序的單發射內核,具有 4 個流水線級,它具有接近 1 的 IPC,完全支持基本整數指令集 (RV32I)、壓縮指令 (RV32C) 和乘法指令集擴展 (RV32M)。它可以配置為具有單精度浮點指令集擴展 (RV32F)。它實現了多個 ISA 擴展,例如:硬件循環、后遞增加載和存儲指令、位作指令、MAC作、支持定點作、打包 SIMD 指令和點積。它旨在提高超低功耗信號處理應用的能效。RISCY 實現了 1.9 特權規范的子集。有關內核的更多信息,請參見http://ieeexplore.ieee.org/abstract/document/7864441/ 和 IP 文檔。

Zero-Riscy 是一個有序、單發射內核,具有 2 個流水線級,它完全支持基本整數指令集 (RV32I) 和壓縮指令 (RV32C)。它可以配置為具有乘法指令集擴展 (RV32M) 和減少的寄存器數擴展 (RV32E)。它旨在針對超低功耗和超低面積限制。zero-riscy 實現 1.9 特權規范的子集。有關內核的更多信息,請參見http://ieeexplore.ieee.org/document/8106976/ 和 IP 文檔。

PULP 包括一個新的高效 I/O 子系統,通過 uDMA (micro-DMA) 與外設自主通信。內核只需要對 uDMA 進行編程并等待它處理傳輸。有關內核的更多信息,請參見http://ieeexplore.ieee.org/document/8106971/ 和 IP 文檔。

PULP 支持接口上的 I/O,例如:

- SPI (作為主設備)

- I2S 系列

- 攝像頭接口 (CPI)

- I2C 接口

- 串口

- JTAG

PULP 還支持集成硬件加速器 (HardwareProcessing Engines),這些加速器與 RI5CY 內核共享內存,并在內存映射上編程。可以在 hwpe-mac-engine 中找到一個示例加速器,該加速器在定點值的向量上執行乘法累加(更新 IP 后:請參閱下面的“入門”部分)。hwpe-stream 和 hwpe-ctrl 文件夾包含將流加速器插入數據和控制平面上的 PULP 系統所需的 IP。有關如何設計和集成此類加速器的更多信息,請參閱 hwpe-stream/doc 和 https://arxiv.org/abs/1612.05974。

開始

[](https://github.com/pulp-platform/pulp#getting-started)

先決條件

[](https://github.com/pulp-platform/pulp#prerequisites)

為了能夠使用 PULP 平臺,您需要 PULP 工具鏈。獲取說明可在此處找到:https://github.com/pulp-platform/pulp-riscv-gnu-toolchain。

構建 RTL 仿真平臺

[](https://github.com/pulp-platform/pulp#building-the-rtl-simulation-platform)

要構建 RTL 仿真平臺,首先要獲取構成 PULP 系統的最新版本的 IP:

source setup/vsim.sh

make checkout

make scripts

make build

注意:運行腳本時可能會出現錯誤(無法生成子進程。打開的文件太多(os 錯誤 24)。雖然修復是 WIP,但解決方法是通過設置(例如 ulimit)4096 (ulimit -n 4096) 來增加計算機可用的進程數。

此命令構建一個不依賴于外圍設備的外部模型的仿真平臺版本。有關如何插入某些型號的真實 SPI、I2C、I2S 外設的詳細信息,請參見下文(專有驗證 IP)。

默認的依賴管理是使用 bender 來收集 IP 來完成的。如果您想使用舊版 IPApproX 工具,請設置 IPAPPROX 環境變量,例如通過運行 export IPAPPROX=1,并繼續作,風險自負。

在 IP 上工作

[](https://github.com/pulp-platform/pulp#working-on-ips)

處理單個 IP 的最簡單方法是使用 bender 和以下命令克隆它:

./bender clone $IP

這會將 IP 檢出到 working_dir 目錄,在那里可以修改 IP 并提交和推送更改。正確的鏈接將通過 Bender.local 文件中的覆蓋來設置,從而強制 bender 工具使用此版本的依賴項。要構建平臺,請確保在調用 ./bender clone 后從上面的 make scripts 步驟開始。

更改完成后,請確保使用新版本相應地更新調用 IP 依賴項的軟件包中的 Bender.yml 文件。bender parents 命令可以幫助確定哪些依賴項的 Bender.yml 文件需要更新。請注意,在修改依賴項版本時,需要調用 ./bender update 命令以重新解析正確的版本。更新完成后,可以刪除 Bender.local 中的相應行以恢復正常的依賴項解析,不再使用 working_dir 中的版本(請務必調用 ./bender update)。有關更多信息,請查看 bender 文檔。

下載并運行簡單的 C 回歸測試

[](https://github.com/pulp-platform/pulp#downloading-and-running-simple-c-regression-tests)

最后,您可以下載并運行測試;為此,您可以查看以下存儲庫:

- 運行時測試:https://github.com/pulp-platform/regression_tests

- 紙漿運行時間:https://github.com/pulp-platform/pulp-runtime

現在你可以將目錄更改為你喜歡的測試,例如:對于 hello worldtest,運行

git clone https://github.com/pulp-platform/regression_tests.git

git clone https://github.com/pulp-platform/pulp-runtime.git

source pulp-runtime/configs/pulp.sh

export PATH=*path to riscv gcc toolchain*/bin:$PATH

export PULP_RISCV_GCC_TOOLCHAIN= *path to riscv gcc toolchain*

cd regression_tests/hello

mae clean all run gui=1

開源仿真平臺依靠 JTAG 來模擬 PULP L2 內存的預加載。如果您想模擬更真實的場景(例如訪問外部 SPI Flash),請查看以下部分。

如果您想查看 Modelsim GUI,只需鍵入

make conf gui=1

在開始模擬之前。

如果要保存(壓縮的)VCD 以供進一步檢查,請鍵入

make conf vsim/script=export_run.tcl

在開始模擬之前。您將在build//pulp/export.vcd.gz 中找到 VCD,其中 是測試的 C 源代碼的名稱。

專有驗證 IP

[](https://github.com/pulp-platform/pulp#proprietary-verification-ips)

完整的仿真平臺可以利用一些商用 SPI、I2C、I2S 外設模型連接到開源 PULP 仿真平臺。在 rtl/vip/spi_flash、rtl/vip/i2c_eeprom、rtl/vip/i2s 中,您可以找到安裝 SPI、I2C 和 I2S 型號的說明。

安裝 SPI flash 模型后,可以切換到更真實的引導模擬,其中 PULP 的內部 ROM 用于執行初始引導并開始從 SPI flash 中自主獲取程序。為此,測試臺的 LOAD_L2 參數必須從JTAG 切換到 STANDALONE。

PULP-SDK 開發工具包

[](https://github.com/pulp-platform/pulp#pulp-sdk)

如果您是軟件開發人員,您可以在此處找到 PULP-SDK:https://github.com/pulp-platform/pulp-sdk。

PULP 平臺結構

[](https://github.com/pulp-platform/pulp#pulp-platform-structure)

按照 入門 部分所述進行完全設置后,此根存儲庫的結構如下:

- rtl/tb 包含主平臺 TestBench 和相關文件。

- rtl/vip 包含用于模擬外部外設的驗證 IP,例如 SPI 閃光燈和相機。

- rtl 還可以包含其他材料(例如,全局包含、頂級文件)

- sim 包含 ModelSim/QuestaSim 仿真平臺。

- pulp-sdk 包含 PULP 軟件開發包;pulp-sdk/tests包含隨 SDK 一起發布的所有測試。

- Bender.yml 包含 bender 工具的所有依存關系和源文件信息。

要求

[](https://github.com/pulp-platform/pulp#requirements)

RTL 平臺有以下要求:

- 相對較新的基于 Linux 的作系統;我們測試了 Ubuntu 16.04 和CentOS 7。

- ModelSim 的最新版本(我們使用 10.6b 版本對其進行了測試)。

- Python 3.4,安裝了 pyyaml 模塊(您可以通過pip3 install pyyaml 獲取它)。

- SDK 有自己的依賴項,如https://github.com/pulp-platform/pulp-sdk/blob/master/README.md

倉庫組織

[](https://github.com/pulp-platform/pulp#repository-organization)

PULP 平臺是高度分層的,各種 IP 的 Git 存儲庫遵循層次結構,以保持最大的靈活性。IP 更新系統的大部分復雜性都隱藏在 bender 工具后面;但是,需要了解一些詳細信息:

- 不要假設任意 IP 的 master 分支是穩定的;許多內部 IP 可能包含其歷史記錄的某個時間點的不穩定更改。相反,在頂級平臺(pulpissimo、pulp)中,我們總是使用穩定版本的 IP。因此,您應該能夠安全地使用 pulpissimo 的master 分支。

- 默認情況下,將使用 HTTPS 從 GitHub 收集 IP。這使得每個人都可以在不先將 SSH 密鑰上傳到 GitHub 的情況下克隆它們。但是,對于開發來說,使用 SSH 通常更容易,特別是如果您想將更改推回去。

用于收集 IP 和創建仿真腳本的工具具有許多功能,這些功能不一定適用于最終用戶,但對開發人員可能很有用;如果您想了解更多信息,例如將 ownrepository 集成到流程中,您可以在https://github.com/pulp-platform/bender/blob/master/README.md 中找到文檔

-

RISC

+關注

關注

6文章

478瀏覽量

84607

發布評論請先 登錄

大象機器人攜手進迭時空推出 RISC-V 全棧開源六軸機械臂產品

RISC V 開源芯片項目:OpenTitan 詳細解讀

芯來科技攜手芯芒科技發布RISC-V CPU系統仿真平臺

關于RISC-V芯片的應用學習總結

深度數智DC-ROMA RISC-V Laptop II入選IEEE Spectrum“Top Tech 2025”

直播預約 |開源芯片系列講座第25期:RISC-V架構在高性能領域的進展與挑戰

《RISC-V能否復制Linux 的成功?》

RISC-V擁有巨大市場潛力的原因

迅龍軟件加入甲辰計劃“開源實習生聯合招聘培養”項目,共建RISC-V?開源生態

JH-7110 RISC-V開發套件正式開源

RISC V 開源芯片項目:PULP(Parallel Ultra Low Power)平臺深度解讀

RISC V 開源芯片項目:PULP(Parallel Ultra Low Power)平臺深度解讀

評論