文章來(lái)源:老虎說(shuō)芯

原文作者:老虎說(shuō)芯

本文詳細(xì)介紹了集成電路設(shè)計(jì)中的版圖設(shè)計(jì)。

在集成電路設(shè)計(jì)中,版圖(Layout)是芯片設(shè)計(jì)的核心之一,通常是指芯片電路的物理實(shí)現(xiàn)圖。它描述了電路中所有元器件(如晶體管、電阻、電容等)及其連接方式在硅片上的具體布局。版圖是將電路設(shè)計(jì)轉(zhuǎn)化為實(shí)際可以制造的物理形態(tài)的重要步驟。可以類比為建筑設(shè)計(jì)中的平面圖,建筑師設(shè)計(jì)的平面圖需要轉(zhuǎn)化為實(shí)際的建筑結(jié)構(gòu),電路設(shè)計(jì)師的版圖就類似于將電路設(shè)計(jì)圖紙轉(zhuǎn)化為可制造的硅片布局。

1. 版圖設(shè)計(jì)的基本概念:

版圖設(shè)計(jì)是芯片設(shè)計(jì)的后端環(huán)節(jié),主要涉及將設(shè)計(jì)中的邏輯電路和功能模塊轉(zhuǎn)化為可以在物理層面實(shí)現(xiàn)的實(shí)際布局。這個(gè)過(guò)程不僅包括元器件的位置安排,還包括它們之間的連線、金屬層的布局等。

2. 版圖的組成:

版圖設(shè)計(jì)的核心內(nèi)容包括以下幾個(gè)方面:

元器件布局:設(shè)計(jì)中使用的各種標(biāo)準(zhǔn)元器件(如邏輯門、存儲(chǔ)單元、處理器核心等)需要根據(jù)設(shè)計(jì)需求在版圖上布置合理的位置。布局不僅要考慮功能的實(shí)現(xiàn),還要考慮信號(hào)的傳輸速度、電源的供給等因素。

金屬互連:版圖中的元器件之間通過(guò)金屬層連接,確保信號(hào)能夠在芯片內(nèi)部傳遞。設(shè)計(jì)師需要選擇合適的金屬層,考慮線寬、間距等因素,以確保信號(hào)的可靠性和時(shí)序的準(zhǔn)確性。

電源與地線的布局:版圖還需要合理安排電源線(VDD)和地線(GND),確保整個(gè)芯片的電力供應(yīng)穩(wěn)定,避免電源噪聲對(duì)電路功能的干擾。

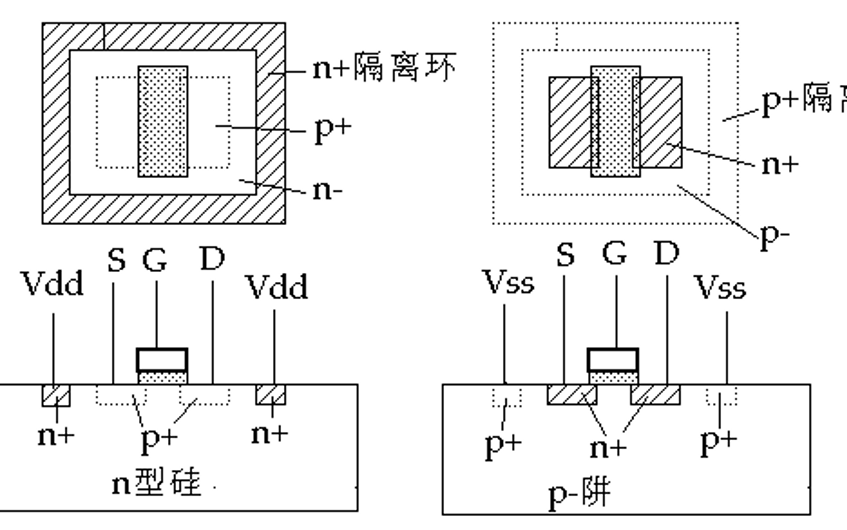

隔離與保護(hù):在版圖設(shè)計(jì)中,還需要設(shè)計(jì)適當(dāng)?shù)母綦x措施,避免信號(hào)干擾和熱問(wèn)題,特別是高功率的電路部分需要有效的散熱設(shè)計(jì)。

3. 版圖設(shè)計(jì)的關(guān)鍵步驟:

綜合(Synthesis):在設(shè)計(jì)階段,通過(guò)綜合工具將高級(jí)描述語(yǔ)言(如Verilog、VHDL)轉(zhuǎn)化為基本的標(biāo)準(zhǔn)單元(Standard Cells)。這些標(biāo)準(zhǔn)單元在版圖設(shè)計(jì)中將成為實(shí)際的物理組件。綜合階段主要是從功能電路轉(zhuǎn)化為邏輯門、觸發(fā)器等基本電路單元的集合。

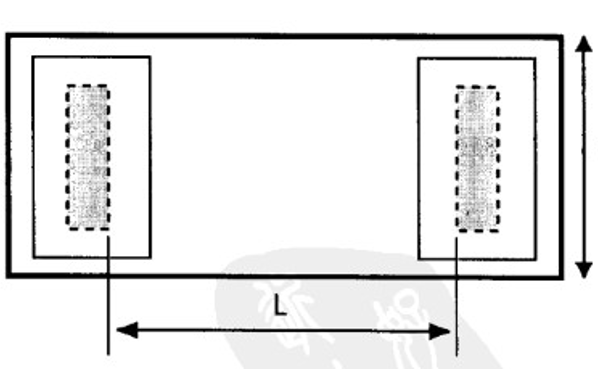

布局(Place):在布局階段,設(shè)計(jì)人員確定每個(gè)標(biāo)準(zhǔn)單元在芯片上的具體位置。這個(gè)過(guò)程需要綜合考慮芯片的面積限制、信號(hào)傳輸距離、電源分布等多個(gè)因素。布局的目標(biāo)是將元器件合理地分布在芯片上,以提高性能和降低功耗。

布線(Route):布線階段負(fù)責(zé)在布局完成后,進(jìn)行元器件之間的連線。通過(guò)布線,設(shè)計(jì)人員將標(biāo)準(zhǔn)單元之間的連接關(guān)系轉(zhuǎn)化為物理的金屬走線。布線設(shè)計(jì)需要確保信號(hào)的傳輸延遲最小,并避免信號(hào)干擾和時(shí)序問(wèn)題。

4. 版圖設(shè)計(jì)中的常見(jiàn)問(wèn)題:

時(shí)序問(wèn)題:如果版圖中的元器件布局不當(dāng),信號(hào)的傳播延遲可能會(huì)影響芯片的時(shí)序,導(dǎo)致功能不正常。因此,版圖設(shè)計(jì)需要進(jìn)行時(shí)序分析,確保信號(hào)在正確的時(shí)間到達(dá)目標(biāo)元器件。

電源完整性問(wèn)題:電源線布局不合理可能導(dǎo)致電壓降落或者噪聲問(wèn)題,從而影響芯片的穩(wěn)定性。因此,版圖設(shè)計(jì)需要對(duì)電源線進(jìn)行優(yōu)化,以確保每個(gè)模塊都能穩(wěn)定供電。

熱管理問(wèn)題:芯片中一些高功率區(qū)域如果沒(méi)有合理布局,會(huì)導(dǎo)致局部過(guò)熱,影響芯片的工作壽命。因此,版圖設(shè)計(jì)還需要考慮芯片的熱分布,采用合適的散熱方案。

5. 版圖設(shè)計(jì)的驗(yàn)證:

在版圖設(shè)計(jì)完成后,設(shè)計(jì)人員需要通過(guò)一系列驗(yàn)證工具進(jìn)行檢查,確保設(shè)計(jì)符合制造工藝的要求。常見(jiàn)的驗(yàn)證步驟包括:

靜態(tài)時(shí)序分析(STA):檢查芯片中所有信號(hào)的傳播延遲,確保不會(huì)發(fā)生時(shí)序違例。

設(shè)計(jì)規(guī)則檢查(DRC):檢查版圖是否符合制造工藝的物理設(shè)計(jì)規(guī)則,比如線寬、線間距、金屬層重疊等。

版圖與原理圖一致性檢查(LVS):確保版圖設(shè)計(jì)中的電路與原理圖一致,即功能上沒(méi)有差錯(cuò)。

6. 版圖設(shè)計(jì)的重要性:

版圖設(shè)計(jì)在芯片設(shè)計(jì)中占據(jù)著非常重要的地位。一個(gè)優(yōu)秀的版圖設(shè)計(jì)不僅能提高芯片的性能,降低功耗,還能有效縮短生產(chǎn)周期,減少設(shè)計(jì)缺陷。因此,版圖設(shè)計(jì)需要具備高度的專業(yè)性和精確性,需要設(shè)計(jì)人員熟悉各類設(shè)計(jì)工具、工藝規(guī)則以及優(yōu)化技巧。

總結(jié)來(lái)說(shuō),版圖是芯片設(shè)計(jì)從邏輯到物理實(shí)現(xiàn)的關(guān)鍵環(huán)節(jié),它將抽象的電路設(shè)計(jì)轉(zhuǎn)化為能夠在硅片上實(shí)際生產(chǎn)的具體布局。版圖設(shè)計(jì)不僅僅是簡(jiǎn)單的元器件布局,它需要綜合考慮時(shí)序、電源、熱量等多種因素,確保芯片能夠在最終應(yīng)用中高效穩(wěn)定地運(yùn)行。

-

集成電路

+關(guān)注

關(guān)注

5420文章

11954瀏覽量

367174 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1067瀏覽量

55468 -

版圖設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

14瀏覽量

8827

原文標(biāo)題:版圖設(shè)計(jì)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

集成電路(IC)常用基本概念

淺談“集成電路版圖CAD”課程建設(shè)

布線測(cè)試中的幾個(gè)關(guān)鍵步驟

集成電路版圖layout設(shè)計(jì)方法與實(shí)例

數(shù)字集成電路版圖提取

集成電路版圖設(shè)計(jì)_IC mask design

集成電路設(shè)計(jì)教程之集成電路版圖設(shè)計(jì)基礎(chǔ)的詳細(xì)資料說(shuō)明

集成電路版圖設(shè)計(jì)基礎(chǔ)教程之電阻版圖設(shè)計(jì)的資料說(shuō)明

集成電路版圖設(shè)計(jì)教程--Cacence軟件

集成電路版圖設(shè)計(jì)的基本概念和關(guān)鍵步驟

集成電路版圖設(shè)計(jì)的基本概念和關(guān)鍵步驟

評(píng)論