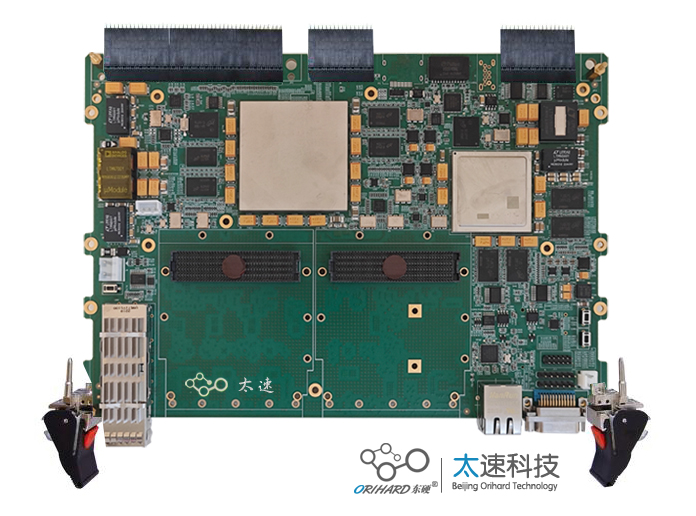

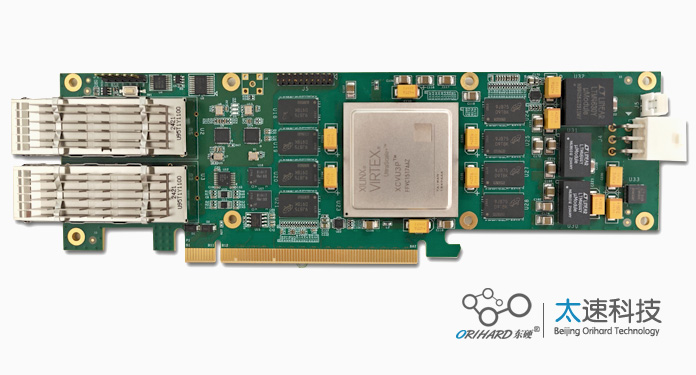

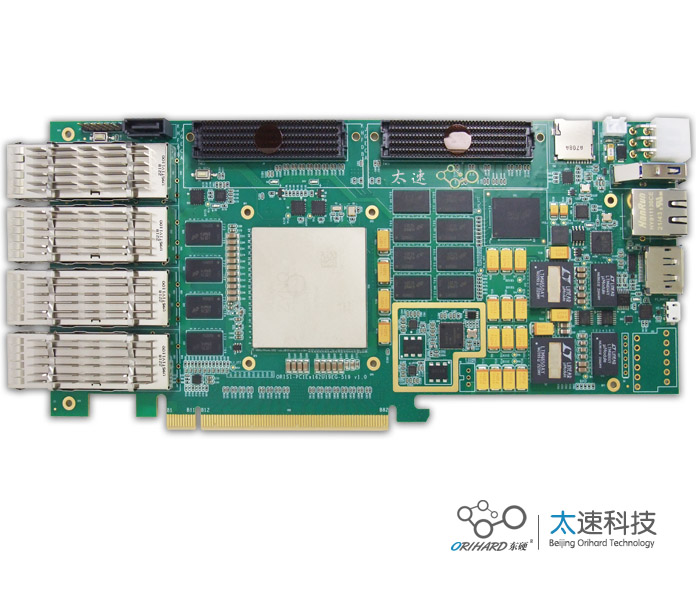

基于TSI721的 PCIe轉RapidIO高速數據傳輸卡

一、板卡概述

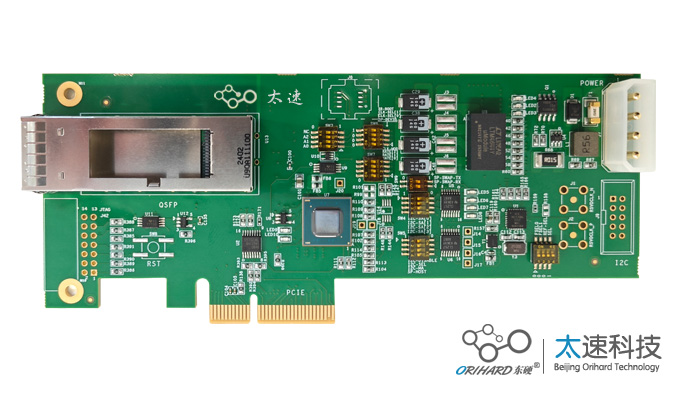

本卡是基于IDTTSI721橋芯片,用于實現SerialRapidIO(S-RIO)Gen2.1到PCIExpress(PCIE)Gen2.1協議轉換,將基于RapidIO的對等網絡多重處理器集群拓展至x86處理器環境,能夠實現基于RapidIO的對等網絡多重處理器集群和基于x86處理器環境之間的高速數據互傳。

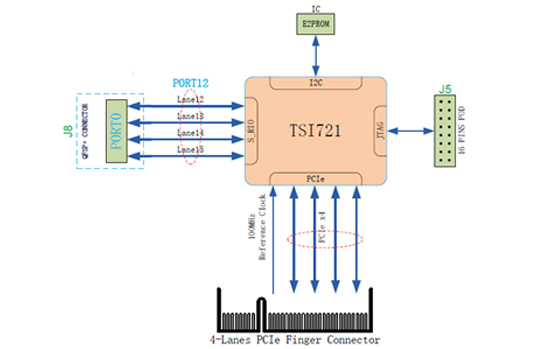

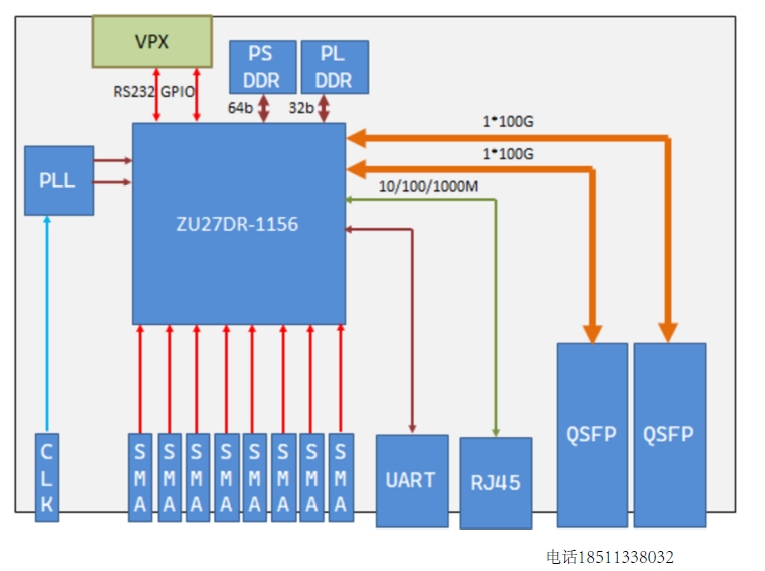

系統框圖

二、功能和技術指標

PCIe端的特征:

支持PCIe2.1協議標準

通道的速率可配置,通道的速率:5/2.5GbaudLinkspeed

傳輸通道數:4xLanes

S-RIO端的特征:

支持協議S-RIO2.1標準

通道的速度率可配置,通道的速率:5/3.125/2.5/1.25GbaudLinkspeed

靈活的物理傳輸接口:1通道4xLinkWidth的QFSP+的光纖收發器接口

支持LanesReversal功能

板卡的特征:

支持IEEE1149.1/1149.6標準的JTAG調試接口

支持I2C標準的調試接口

靈活的配置:DIP開關配置TSI721工作模式

電源供電:PCIE供電或標準ATX12V電源接口供電

1個復位按鈕,可用于系統復位

提供Window驅動程序

提供Window下的Demo程序

所有的器件件支持商業級、工業級

三、應用領域

聲納信號處理平臺

軟件無線電處理平臺

圖像信號處理平臺

審核編輯 黃宇

-

光纖

+關注

關注

19文章

4105瀏覽量

74710 -

圖像信號處理

+關注

關注

0文章

18瀏覽量

7573

發布評論請先 登錄

設計原理圖:U200E 基于VU9P的4路QSFP28光纖PCIeX16收發卡

高速圖像處理卡設計原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

XCVU13P板卡設計原理圖:509-基于XCVU13P的4路QSFP28光纖PCIeX16收發卡

調試一塊使用lmk04228作為光纖通訊的參考時鐘的板卡,遇到的疑問求解答

基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡

XCVU9P 板卡設計原理圖:616-基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡 高性能數字計算卡

圖形圖像硬件加速器卡設計原理圖:270-VC709E 基于FMC接口的Virtex7 XC7VX690T PCIeX8 接口卡

圖像信號處理平臺設計原理圖:721-基于VU9P的32+8路光纖交換板卡硬件設計

圖像信號處理平臺設計原理圖:721-基于VU9P的32+8路光纖交換板卡硬件設計

評論