過去幾十年來,單片芯片一直是推動技術進步的主力。但就像工業革命期間,役畜被更高效強大的機器所取代一樣,半導體行業如今也處于類似變革的階段。

Multi-Die和基于小芯片的設計,即將多個專用芯片集成在單個封裝中或將集成電路垂直堆疊,有望帶來比單片芯片更高的性能和靈活性,能夠滿足高性能計算(HPC)以及AI驅動的工作負載對處理能力永無止境的需求。但是,要開發這些先進的芯片設計,需要極其雄厚的資金和前沿的研發能力。

但如今情況不同了。

Multi-Die技術、工具、流程和IP都在迅速成熟。工程專業知識也在不斷發展。同時,晶圓代工廠的產能持續擴張。基于這些考慮,我們預測,到2025年,50%的新型高性能計算芯片設計將采用Multi-Die技術。

晶圓代工廠積極布局,準備迎接Multi-Die設計浪潮

要將Multi-Die設計推向市場,僅靠研發是不夠的。它還需要高帶寬、低延遲的互連、具備充足產能的先進制造工藝,以及精密的設計工具和IP。

通用芯粒互連技術(UCIe)等開放行業標準不斷成熟,有助于簡化和加強異構小芯片之間的連接,同時降低風險并縮短設計周期。UCIe在高性能計算、人工智能、數據中心以及邊緣應用領域的運用日益廣泛,正推動市場對Multi-Die設計產生巨大需求。

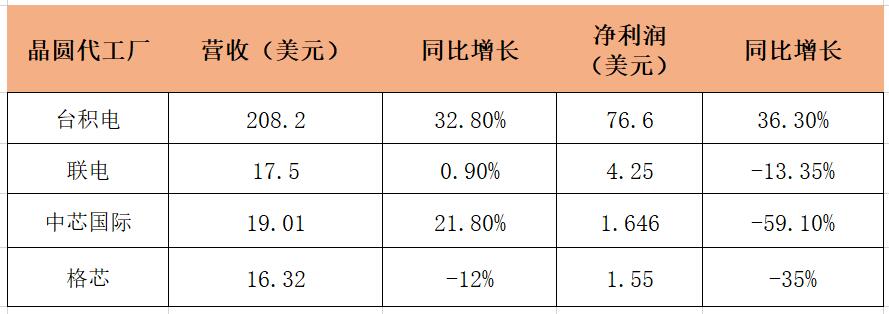

除了先進互連技術的成熟與普及,晶圓代工廠也在為即將到來的Multi-Die設計浪潮做準備。這包括采用能實現更密集凸點和更高性能的新型制造工藝。額外的封裝、中介層和集成選項帶來了成本和架構上的靈活性。而擴大的產能意味著更多的設計和原型能夠推向市場。

先進的Multi-Die設計工具和IP

開發這些尖端芯片離不開最先進的設計解決方案,而新思科技始終處于Multi-Die創新的前沿。我們全面且可擴展的Multi-Die解決方案包括設計自動化工具和IP,能夠助力實現:

早期架構探索

快速軟件開發和系統驗證

高效的裸片/封裝協同設計

魯棒的裸片間和芯片間連接

增強的制造能力和可靠性

我們還提供超高性能、超低延遲、超低功耗和超小面積的Die-to-Die IP解決方案,其中包括UCIe和專用控制器、物理層器件(PHY)以及驗證IP。基于UCIe的IP符合最新的UCIe規范,而專用的Die-to-Die IP可提供40Gbps的性能、優化芯片邊緣利用率和能效,同時具備低延遲,并支持標準和先進的封裝技術。

我們的Multi-Die解決方案已助力多個基于不同代工工藝的項目成功實現芯片量產。客戶采用率和晶圓代工廠產能都在持續提升,同時高帶寬低延遲的互連標準也在不斷成熟。

基于以上原因,我們認為,到2025年,至少有一半的新型高性能計算芯片設計將采用Multi-Die技術。

-

芯片

+關注

關注

459文章

52145瀏覽量

435764 -

晶圓

+關注

關注

52文章

5113瀏覽量

129139 -

新思科技

+關注

關注

5文章

851瀏覽量

51174 -

HPC

+關注

關注

0文章

332瀏覽量

24187

原文標題:2025年,Multi-Die技術將被50%新型 HPC芯片所采用

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

利用新思科技Multi-Die解決方案加快創新速度

新思科技全新40G UCIe IP解決方案助力Multi-Die設計

6.4級地震沖擊嘉義,臺南晶圓代工廠與面板廠受影響情況概覽

利用Multi-Die設計的AI數據中心芯片對40G UCIe IP的需求

韓國政府考慮成立政府資助晶圓代工廠

新思科技Multi-Die系統如何滿足現代計算需求

使用0.5英寸晶圓的代工廠

IBM、富士通或投資Rapidus晶圓代工廠

買家現身!這家氮化鎵晶圓代工廠收到10億元競標

晶圓出貨量增長!臺積電Q2營收飆漲,四大芯片代工廠財報有何亮點?

新思科技助力晶圓代工廠迎接Multi-Die設計浪潮

新思科技助力晶圓代工廠迎接Multi-Die設計浪潮

評論