本文引入基于光學(xué)PCB的波導(dǎo)嵌入式系統(tǒng)(WES),用于AI/HPC數(shù)據(jù)中心,以克服CPO集成挑戰(zhàn)。WES通過集成光學(xué)引擎與精確耦合結(jié)構(gòu),實(shí)現(xiàn)高密度、低損耗、無光纖的設(shè)備間光互連。

引入基于光學(xué)PCB的波導(dǎo)嵌入式系統(tǒng)(Waveguide Embedded System,WES),用于AI/HPC數(shù)據(jù)中心,能夠克服CPO集成的挑戰(zhàn)。WES通過集成的光學(xué)引擎和精確的耦合結(jié)構(gòu)實(shí)現(xiàn)了高密度、低損耗、無光纖的設(shè)備到設(shè)備光學(xué)互連。

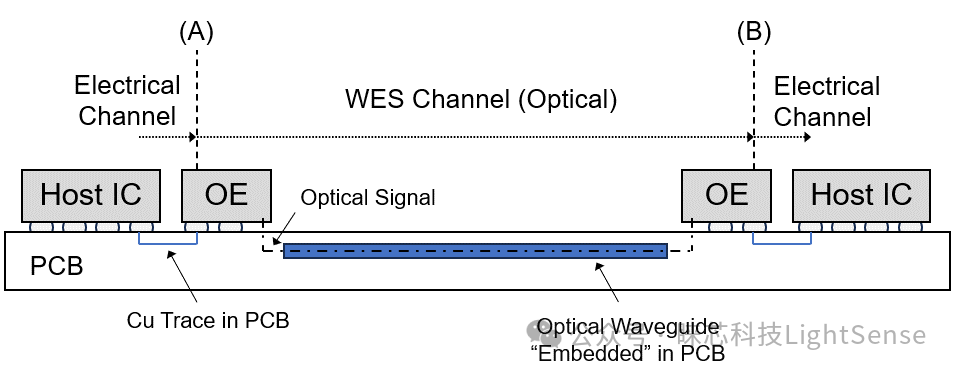

WES由三個關(guān)鍵組件組成,如圖1所示:光學(xué)PCB、光學(xué)引擎和耦合結(jié)構(gòu)。WES信道通過轉(zhuǎn)換到光域并返回,使高速電信號能夠從點(diǎn)(A)傳遞到點(diǎn)(B)。光信道通過半導(dǎo)體封裝和PCB嵌入式波導(dǎo)形式的高度集成的光學(xué)引擎提供無縫的數(shù)據(jù)傳輸。

圖1。波導(dǎo)嵌入式系統(tǒng)(Waveguide Embedded System,WES)的系統(tǒng)圖。WES信道可以提供從PCB內(nèi)的點(diǎn)(A)到(B)的高性能設(shè)備到設(shè)備的光鏈路。

A.光學(xué)引擎

WES信道的終端包括一個光學(xué)引擎(OE),它將電數(shù)據(jù)轉(zhuǎn)換為光學(xué)數(shù)據(jù),反之亦然。OE由Tx側(cè)的VCSEL和驅(qū)動器IC以及Rx側(cè)的PD和TIA組成,它們之間有一個短長度多模波導(dǎo)。

為了在PCB生態(tài)系統(tǒng)中實(shí)現(xiàn)無縫集成,OE必須具有與其他電氣元件相似的外形尺寸。扇出晶圓級封裝(FOWLP)是一種先進(jìn)的半導(dǎo)體封裝方法,是將VCSEL和PD與電子IC集成的最有前景的技術(shù)。LIPAC首次引入了光學(xué)系統(tǒng)級封裝(O-SiP)技術(shù),并為該項(xiàng)目提供了光學(xué)引擎。

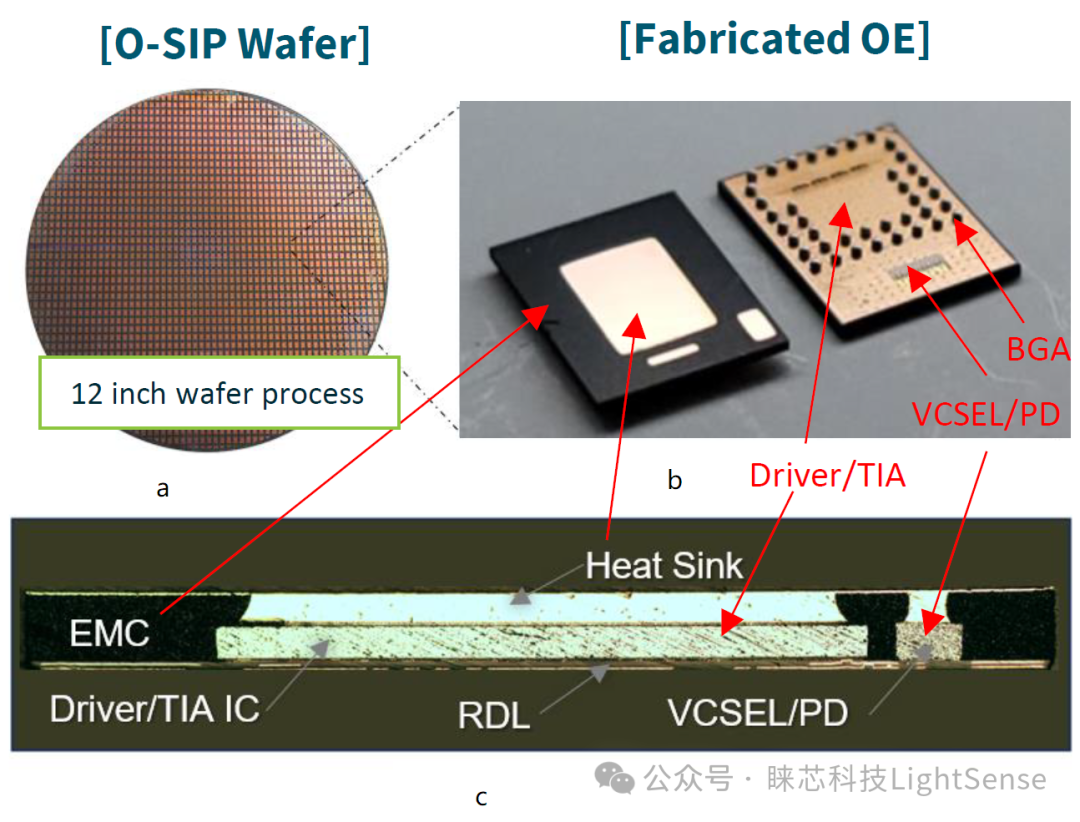

圖2顯示了基于FOLWP的OE,這是一種標(biāo)準(zhǔn)的BGA封裝,但沒有基板。OE既薄又小,可能適合未來物理信道密度的增加。光學(xué)窗口放置在封裝的BGA側(cè),組裝時面朝下,而封裝的頂側(cè)可用于散熱。

圖2。采用FOWLP方法制造的光學(xué)引擎。(a) 它可以以12英寸晶圓尺寸的格式生產(chǎn)。(b) WES光學(xué)引擎的前后兩側(cè)。在OE的背面可以看到球柵陣列和VCSEL/PD開口。(c) OE的橫截面圖。IC與VCSEL/PD在EMC材料內(nèi)共同封裝。OE中形成了作為RDL的精細(xì)電層。

B.光學(xué)PCB

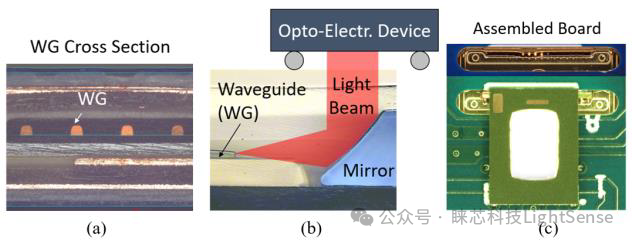

WES包括嵌入PCB中的多模波導(dǎo),作為光學(xué)數(shù)據(jù)傳輸通道。與PCB中的銅跡線類似,光波導(dǎo)層可以布置為互連跡線,并且可以用聚合物基材料制造。波導(dǎo)的核心可以通過接觸掩模光刻工藝或激光直接成像(LDI)制成,這兩種工藝都與傳統(tǒng)的PCB制造工藝兼容。10-40μm的包覆層用于夾持40-50μm的芯層,如圖3(a)所示。

圖3。(a) 帶波導(dǎo)(WG)的O-PCB的橫截面圖。(b) O-PCB中OE和WG之間的光耦合結(jié)構(gòu)。(c) O-PCB上帶有OE和耦合鏡的組裝板圖片。

最小彎曲半徑通常約為15mm,而標(biāo)準(zhǔn)波導(dǎo)間距約為250μm。與電信道相比,這允許更高密度、更低損耗和更低串?dāng)_的光信道。

C.耦合結(jié)構(gòu)

凹面鏡分別用于從OE嵌入式VCSEL到Tx側(cè)的波導(dǎo)和從波導(dǎo)到Rx側(cè)的OE嵌入式PD的光耦合。如圖3(b)所示,光束被聚焦到波導(dǎo)和PD中。耦合器在X-Y方向上的對準(zhǔn)公差約為±15μm,Z方向?yàn)椤?0μm。反射鏡組件具有與波導(dǎo)層中的基準(zhǔn)配合的引導(dǎo)結(jié)構(gòu),允許反射鏡組裝到PCB上并與波導(dǎo)精確對齊。圖3(c)顯示了組裝到PCB上的組裝好的反射鏡組件,該組件具有由各種光學(xué)元件制造的集成波導(dǎo)結(jié)構(gòu)。其他形式的耦合器也是可能的。例如,microGlass提出了一種雙芯片耦合結(jié)構(gòu)(一個用于OE側(cè),另一個用于PCB側(cè))來提高對準(zhǔn)精度。

演示器的組裝

在PCB上組裝OE需要比電氣元件組裝更高的精度。對準(zhǔn)公差由耦合結(jié)構(gòu)的光學(xué)設(shè)計決定。因此,應(yīng)謹(jǐn)慎選擇裝配方法。在PoC演示器中,使用倒裝芯片鍵合機(jī)將OE放置在PCB上,對準(zhǔn)公差為±5μm。為了使用傳統(tǒng)的IR回流方法,在放置OE之前,在PCB和OE之間涂上環(huán)氧樹脂。環(huán)氧樹脂固定了倒裝芯片鍵合機(jī)提供的位置精度,并防止了紅外回流過程中OE的移動。

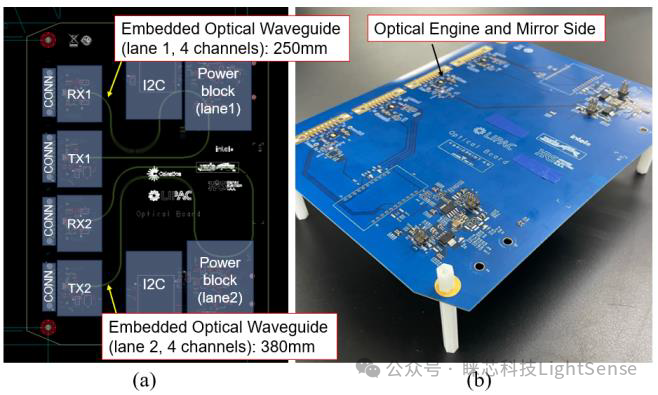

圖4顯示了PCIe演示器的OE和OPCB的設(shè)計和組裝。它包括OE和高速同軸電纜連接器的操作電路,以測試射頻性能。我們驗(yàn)證了VCSEL可以在這個系統(tǒng)中通電。波導(dǎo)損耗和耦合損耗加起來約為-6.5dB(最佳情況)。

圖4。(a) 演示器的PCB設(shè)計,包括電源塊、I2C電路、RF連接器。(b) 所有電氣和光學(xué)部件均采用O-PCB制造。

-

pcb

+關(guān)注

關(guān)注

4349文章

23403瀏覽量

406383 -

嵌入式系統(tǒng)

+關(guān)注

關(guān)注

41文章

3664瀏覽量

130847

原文標(biāo)題:基于光學(xué)PCB的波導(dǎo)嵌入式系統(tǒng)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

嵌入式系統(tǒng)原理、設(shè)計與應(yīng)用

基于嵌入式軟件的JNI技術(shù)應(yīng)用解析

嵌入式系統(tǒng)是什么專業(yè)_嵌入式系統(tǒng)主要學(xué)什么

嵌入式系統(tǒng)的全面解析

解析嵌入式系統(tǒng)的定義、應(yīng)用及趨勢

嵌入式系統(tǒng)定義

嵌入式系統(tǒng)

什么是嵌入式系統(tǒng)

嵌入式系統(tǒng)設(shè)計的問答

嵌入式系統(tǒng)設(shè)計(一)

光學(xué)PCB基波導(dǎo)嵌入式系統(tǒng)解析

光學(xué)PCB基波導(dǎo)嵌入式系統(tǒng)解析

評論