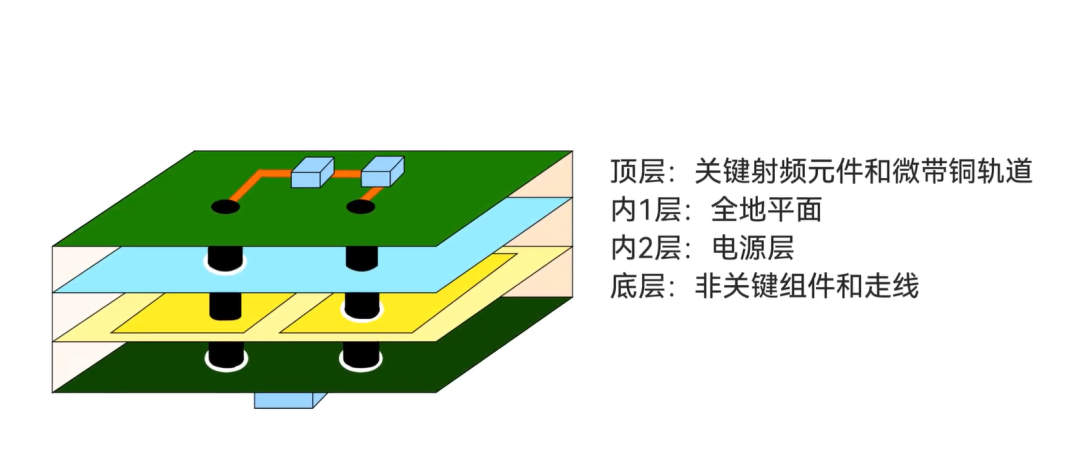

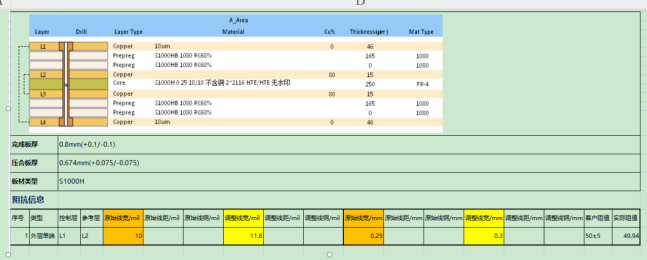

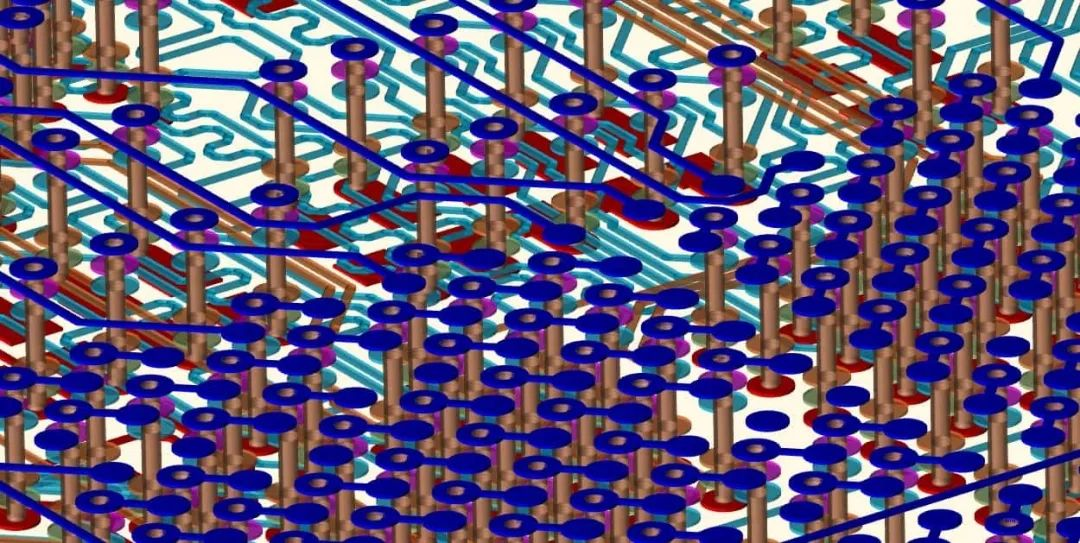

PCB的布局和走線在射頻電路中占據(jù)舉足輕重的作用,影響整個PCB的設(shè)計性能,甚至是整個產(chǎn)品的性能。在繪制完成原理圖后,開始繪制PCB前,首先要確認(rèn)繪制的PCB是幾層板子,射頻一般建議是4層,第二層保持完整的GND,其次再確定整體布局,再開始走線,確認(rèn)線寬。

PCB布局一般原則

1、元器件布局時盡量單面放置,可以降低產(chǎn)品生產(chǎn)時的加工成本。

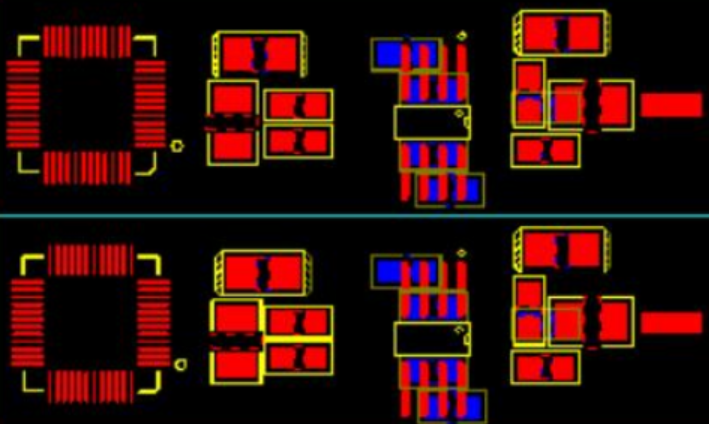

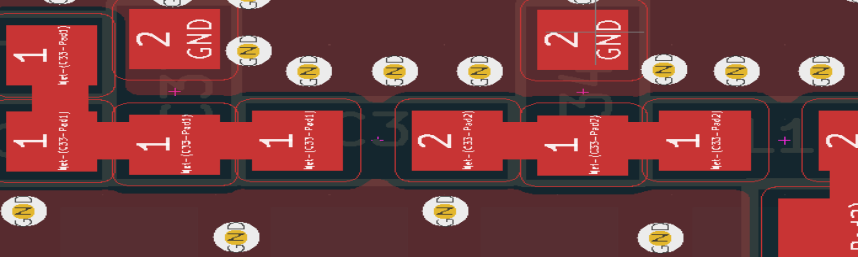

2、封裝、結(jié)構(gòu)相類似的電路,采用對稱結(jié)構(gòu)布局,有電氣關(guān)系的器件盡量放在一起,器件要做到模塊化。

對稱結(jié)果布局

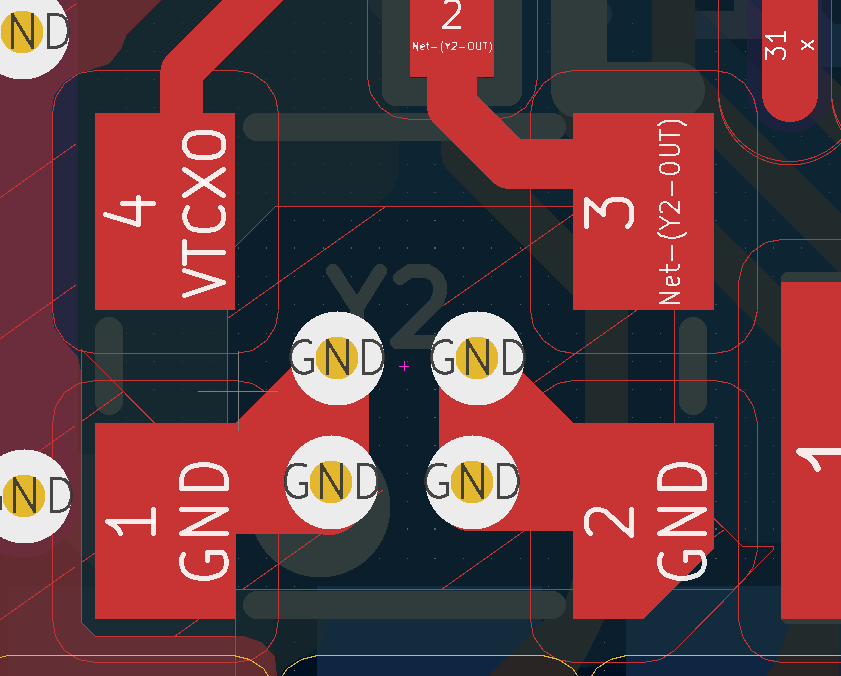

3、在高頻率的數(shù)字電路中,晶振(有源)和晶體(無源)需要盡可能的靠近芯片,如果離芯片太遠(yuǎn),芯片接收到信號后產(chǎn)生的方波會受到一定干擾,可能會導(dǎo)致數(shù)字電路工作異常。

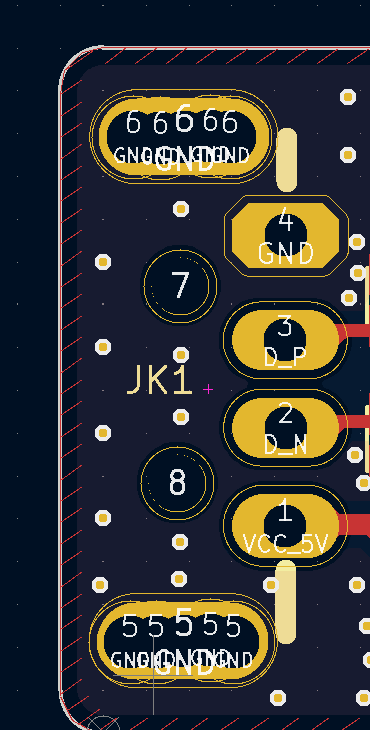

4、接口器件的布局要合理化,元器件放置要考慮到板邊的距離是否合理,例如直插的USB端子,如果布局時離板邊過遠(yuǎn)會出現(xiàn)直插器件插不進板子的情況,見下圖,放置到板子中心,直插的USB根本無法插入。

5、對于一些接口器件要標(biāo)明”+”、”-”,做出絲印說明,防止因為接線錯誤導(dǎo)致電路板子燒毀。

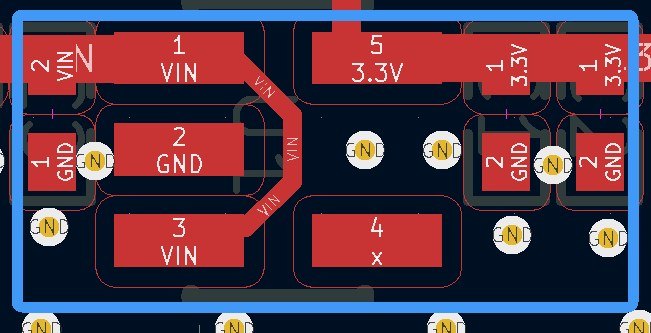

6、對于射頻模組,優(yōu)先布局射頻電路,對于Π形網(wǎng)絡(luò),盡量呈現(xiàn)“一字形“,而且兩邊要鋪GND處理,見下圖。

7、高壓器件和低壓器件要保持安全距離,一般壓差100V,相隔開1毫米。高壓和低壓之間也可以通過隔開地處理。這樣的目的是電器絕緣。

8、濾波電容和去耦電容要放置在芯片的入口處和芯片出口。放置去耦電容和濾波電容是為了改善電源的質(zhì)量,提高抗干擾的一種手段。放置電容時緊靠芯片。

9、布局時對于對熱量敏感的元器件要遠(yuǎn)離發(fā)熱量大的器件,發(fā)熱量大的器件背面要做到開窗散熱,或者安裝散熱片。

10、布局時,還需要考慮是否方便焊接,大器件旁邊避免放置小器件,需要調(diào)試的器件因為需要經(jīng)常焊接,要預(yù)留夠足夠的空間,避免拆去器件困難。

PCB走線一般原則

1、走線3W原則,3W原則指的是:線的中心間距不小于3倍線寬,從而降低走線之間的干擾,走線避免直角。

2、走線時,電源線和地線要盡量粗。減小壓降,以及走線過細(xì)可能會導(dǎo)致PCB的走線被燒斷。3、晶振走線要短,盡量避免打過孔換層,包地處理。晶振下面盡量避免走電源線、信號線,PCB同層挖空打過地過孔到第二層,如下圖:

4、射頻走線要做阻抗設(shè)計,可以通過軟件SI9000,在板厚和到地的間距確認(rèn)下計算線寬,見下圖:

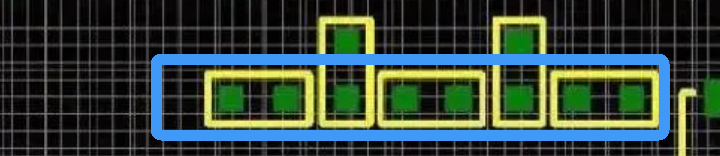

5、差分走線

差分走線相對于單端走線,抗干擾能力強,抑制EMI,差分線走線要做到等寬等間距。

*部分資料和圖片來源于網(wǎng)絡(luò),侵刪

-

PCB板

+關(guān)注

關(guān)注

27文章

1473瀏覽量

53281 -

射頻電路

+關(guān)注

關(guān)注

35文章

438瀏覽量

43908 -

Layout設(shè)計

+關(guān)注

關(guān)注

1文章

14瀏覽量

1687

發(fā)布評論請先 登錄

PCB Layout的設(shè)計要點

PCB Layout設(shè)計要點與技巧

PCB layout結(jié)合生產(chǎn)的設(shè)計要點分析

DCDC芯片中PCB Layout的設(shè)計要點

干貨分享:PCB Layout的設(shè)計要點

干貨分享:PCB Layout 的設(shè)計要點

PCB電路板設(shè)計中的12要點

PCB Layout的設(shè)計要點及技巧

PCB Layout 的 9 個套路

推薦必看!PCB板Layout設(shè)計要點

推薦必看!PCB板Layout設(shè)計要點

評論