總線系統(tǒng)是計(jì)算機(jī)和其他電子設(shè)備中用于傳輸數(shù)據(jù)的關(guān)鍵組件。性能優(yōu)化可以提高數(shù)據(jù)傳輸速率、降低延遲,并增強(qiáng)系統(tǒng)的可靠性和擴(kuò)展性。

1. 理解總線系統(tǒng)

2. 硬件優(yōu)化

- 總線寬度 :增加數(shù)據(jù)總線寬度可以提高數(shù)據(jù)傳輸速率。

- 總線速度 :提高總線的工作頻率可以減少傳輸延遲。

- 信號(hào)完整性 :優(yōu)化PCB布局和信號(hào)完整性,減少噪聲和干擾。

- 電源管理 :優(yōu)化電源分配,確保穩(wěn)定的電源供應(yīng),減少電壓降。

3. 軟件優(yōu)化

- 驅(qū)動(dòng)程序優(yōu)化 :更新和優(yōu)化驅(qū)動(dòng)程序以提高兼容性和性能。

- 中斷處理 :優(yōu)化中斷服務(wù)例程,減少中斷延遲。

- DMA(直接內(nèi)存訪問) :利用DMA減少CPU負(fù)載,提高數(shù)據(jù)傳輸效率。

- 緩存管理 :合理配置緩存,減少總線訪問次數(shù)。

4. 系統(tǒng)架構(gòu)優(yōu)化

- 模塊化設(shè)計(jì) :采用模塊化設(shè)計(jì),便于升級(jí)和維護(hù)。

- 負(fù)載均衡 :通過負(fù)載均衡技術(shù)分散總線負(fù)載,避免瓶頸。

- 冗余設(shè)計(jì) :引入冗余總線或設(shè)備,提高系統(tǒng)的容錯(cuò)能力。

5. 性能測(cè)試與監(jiān)控

- 性能基準(zhǔn)測(cè)試 :定期進(jìn)行性能基準(zhǔn)測(cè)試,識(shí)別性能瓶頸。

- 實(shí)時(shí)監(jiān)控 :實(shí)施實(shí)時(shí)監(jiān)控系統(tǒng),及時(shí)發(fā)現(xiàn)并解決問題。

6. 故障排除與維護(hù)

- 日志分析 :分析系統(tǒng)日志,識(shí)別和解決性能問題。

- 硬件診斷 :定期進(jìn)行硬件診斷,確保設(shè)備正常工作。

7. 未來趨勢(shì)

- 新技術(shù)應(yīng)用 :探討新技術(shù)如雷電接口、下一代PCIe等對(duì)性能的潛在影響。

- 人工智能優(yōu)化 :利用AI進(jìn)行性能預(yù)測(cè)和自動(dòng)調(diào)優(yōu)。

結(jié)論

總線系統(tǒng)性能優(yōu)化是一個(gè)持續(xù)的過程,需要硬件、軟件和系統(tǒng)架構(gòu)的綜合考慮。通過上述方法,可以顯著提高總線系統(tǒng)的性能,從而提升整個(gè)系統(tǒng)的效率和響應(yīng)速度。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

電子設(shè)備

+關(guān)注

關(guān)注

2文章

2869瀏覽量

54507 -

傳輸數(shù)據(jù)

+關(guān)注

關(guān)注

1文章

127瀏覽量

16292 -

總線系統(tǒng)

+關(guān)注

關(guān)注

0文章

30瀏覽量

10178

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

HarmonyOS優(yōu)化應(yīng)用內(nèi)存占用問題性能優(yōu)化四

,不同系統(tǒng)的閾值不同)時(shí),系統(tǒng)可能會(huì)認(rèn)為應(yīng)用存在嚴(yán)重的內(nèi)存問題,并可能會(huì)強(qiáng)制殺死該應(yīng)用進(jìn)程,以保證設(shè)備系統(tǒng)的穩(wěn)定性和性能。為了避免應(yīng)用被系統(tǒng)

發(fā)表于 05-24 17:20

HarmonyOS優(yōu)化應(yīng)用內(nèi)存占用問題性能優(yōu)化一

一、 概述

用戶功能的不斷增強(qiáng),應(yīng)用越來越復(fù)雜,占用的內(nèi)存也在不斷膨脹,而內(nèi)存作為系統(tǒng)的稀缺資源比較有限,當(dāng)應(yīng)用程序占用過多內(nèi)存時(shí),系統(tǒng)可能會(huì)頻繁進(jìn)行內(nèi)存回收和重新分配,導(dǎo)致應(yīng)用程序的性能下降,甚至

發(fā)表于 05-21 11:27

HarmonyOS NEXT 原生應(yīng)用/元服務(wù)-DevEco Profiler性能優(yōu)化過程

流程概覽

在開發(fā)應(yīng)用時(shí),開發(fā)者會(huì)對(duì)應(yīng)用的運(yùn)行情況有一個(gè)預(yù)期的指標(biāo),當(dāng)應(yīng)用在某些方面不能滿足預(yù)期的指標(biāo)或者表現(xiàn)不佳時(shí),意味著您的應(yīng)用可能存在性能問題,需要對(duì)應(yīng)用進(jìn)行性能優(yōu)化以達(dá)到您的預(yù)期。應(yīng)用的

發(fā)表于 02-19 15:28

MPLS網(wǎng)絡(luò)性能優(yōu)化技巧

MPLS(多協(xié)議標(biāo)簽交換)網(wǎng)絡(luò)性能優(yōu)化是一個(gè)復(fù)雜的過程,涉及多個(gè)方面的技術(shù)和策略。以下是一些關(guān)鍵的MPLS網(wǎng)絡(luò)性能優(yōu)化技巧: 一、確保網(wǎng)絡(luò)設(shè)備支持 設(shè)備兼容性 :確保所有網(wǎng)絡(luò)設(shè)備(如路

如何優(yōu)化TCP協(xié)議的性能

優(yōu)化TCP協(xié)議的性能可以從多個(gè)方面入手,以下是一些關(guān)鍵的策略和方法: 一、調(diào)整TCP參數(shù) TCP窗口大小 : 重要性 :TCP窗口大小是衡量TCP協(xié)議性能的一個(gè)關(guān)鍵參數(shù),決定了無需等待確認(rèn)應(yīng)答即可

增強(qiáng)的RS-485性能:針對(duì)長(zhǎng)距離現(xiàn)場(chǎng)總線優(yōu)化的接收器故障安全、遲滯、共模范圍和增益帶寬

電子發(fā)燒友網(wǎng)站提供《增強(qiáng)的RS-485性能:針對(duì)長(zhǎng)距離現(xiàn)場(chǎng)總線優(yōu)化的接收器故障安全、遲滯、共模范圍和增益帶寬.pdf》資料免費(fèi)下載

發(fā)表于 01-15 16:42

?0次下載

總線布局對(duì)設(shè)備性能的影響

在計(jì)算機(jī)和其他電子設(shè)備中,總線布局是連接各個(gè)組件的關(guān)鍵架構(gòu)。它不僅影響數(shù)據(jù)傳輸?shù)乃俣群托剩€關(guān)系到整個(gè)系統(tǒng)的穩(wěn)定性和擴(kuò)展性。 一、數(shù)據(jù)傳輸速率 總線寬度:總線寬度決定了一次可以傳輸?shù)?/div>

RAID 5 性能優(yōu)化技巧

RAID 5是一種廣泛使用的磁盤陣列配置,它通過在多個(gè)硬盤之間分散數(shù)據(jù)和奇偶校驗(yàn)信息來提供數(shù)據(jù)冗余和性能提升。然而,RAID 5的性能受到多種因素的影響,包括硬件選擇、配置、操作系統(tǒng)優(yōu)化

仿真系統(tǒng)的性能優(yōu)化技巧

在現(xiàn)代工業(yè)和科學(xué)研究中,仿真系統(tǒng)扮演著越來越重要的角色。它們不僅能夠幫助我們預(yù)測(cè)復(fù)雜系統(tǒng)的行為,還能在沒有實(shí)際物理原型的情況下進(jìn)行實(shí)驗(yàn)和測(cè)試。然而,隨著仿真模型的復(fù)雜度增加,性能優(yōu)化成

如何優(yōu)化MEMS設(shè)計(jì)以提高性能

優(yōu)化MEMS(微機(jī)電系統(tǒng))設(shè)計(jì)以提高性能是一個(gè)復(fù)雜且多維的任務(wù),涉及多個(gè)學(xué)科和技術(shù)的綜合應(yīng)用。以下是一些關(guān)鍵的優(yōu)化策略和方法: 一、系統(tǒng)級(jí)設(shè)

如何優(yōu)化DCS系統(tǒng)的性能

優(yōu)化DCS(分布式控制系統(tǒng))系統(tǒng)的性能是確保工業(yè)自動(dòng)化過程高效、穩(wěn)定運(yùn)行的關(guān)鍵。以下是一些具體的優(yōu)化措施: 一、硬件

如何優(yōu)化emc存儲(chǔ)性能

在當(dāng)今的數(shù)據(jù)中心環(huán)境中,存儲(chǔ)性能對(duì)于業(yè)務(wù)連續(xù)性和數(shù)據(jù)訪問速度至關(guān)重要。EMC作為領(lǐng)先的存儲(chǔ)解決方案提供商,其產(chǎn)品線涵蓋了從入門級(jí)到企業(yè)級(jí)的存儲(chǔ)系統(tǒng)。然而,即使是最好的存儲(chǔ)系統(tǒng)也需要定期優(yōu)化

如何優(yōu)化SOC芯片性能

優(yōu)化SOC(System on Chip,系統(tǒng)級(jí)芯片)芯片性能是一個(gè)復(fù)雜而多維的任務(wù),涉及多個(gè)方面的優(yōu)化策略。以下是一些關(guān)鍵的優(yōu)化措施: 一

如何優(yōu)化FPGA設(shè)計(jì)的性能

、延遲、吞吐量等。這些指標(biāo)應(yīng)根據(jù)系統(tǒng)的性能需求和資源限制來確定。 分析約束 :了解并考慮所有相關(guān)的設(shè)計(jì)約束,如功耗、成本、可制造性等,以確保優(yōu)化方案的實(shí)際可行性。 二、邏輯設(shè)計(jì)優(yōu)化 減

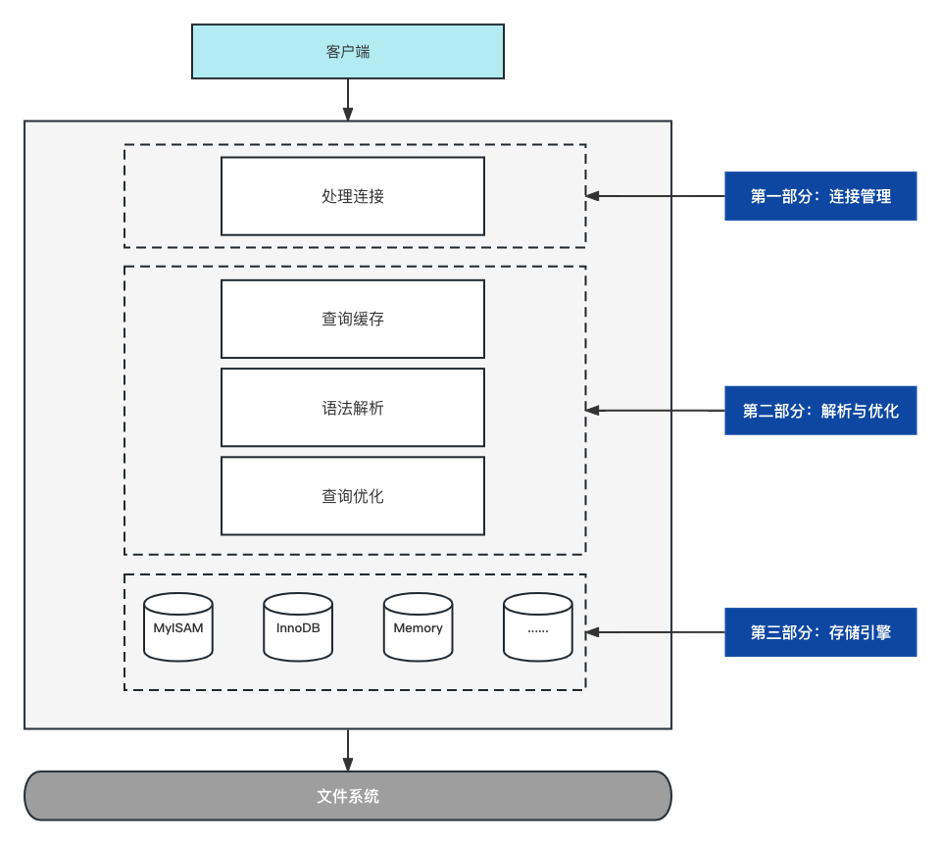

MySQL性能優(yōu)化淺析及線上案例

作者:京東健康 孟飛 1、 數(shù)據(jù)庫(kù)性能優(yōu)化的意義 業(yè)務(wù)發(fā)展初期,數(shù)據(jù)庫(kù)中量一般都不高,也不太容易出一些性能問題或者出的問題也不大,但是當(dāng)數(shù)據(jù)庫(kù)的量級(jí)達(dá)到一定規(guī)模之后,如果缺失有效的預(yù)警、監(jiān)控、處理等

如何優(yōu)化總線系統(tǒng)的性能

如何優(yōu)化總線系統(tǒng)的性能

評(píng)論