芯片行業(yè)正在努力在未來(lái)幾年內(nèi)將3D NAND閃存的堆棧高度提高四倍,從 200 層增加到 800 層或更多,利用額外的容量將有助于滿足對(duì)各種類型內(nèi)存的無(wú)休止需求。

這些額外的層將帶來(lái)新的可靠性問(wèn)題和一系列增量可靠性挑戰(zhàn),但近十年來(lái),NAND 閃存行業(yè)一直在穩(wěn)步增加堆棧高度。2015 年,東芝宣布推出首個(gè)使用硅通孔的 16 芯片堆棧。這實(shí)現(xiàn)了更高的帶寬、更低的延遲和更快的 I/O,同時(shí)也為堆疊其他類型的內(nèi)存和邏輯芯片鋪平了道路。

“最初,NAND 是水平擴(kuò)展的,”Lam Research蝕刻生產(chǎn)力和設(shè)備情報(bào)副總裁 Tae Won Kim 表示。“但十多年前,制造商意識(shí)到橫向擴(kuò)展本身并不具有成本效益,因此他們轉(zhuǎn)向了垂直擴(kuò)展。”

堆疊芯片為顯著提高密度和加快數(shù)據(jù)訪問(wèn)速度打開(kāi)了大門(mén)。ACM Research 總經(jīng)理 Mohan Bhan 表示:“3D NAND 的發(fā)展方向是 500 到 1,000 層。但實(shí)現(xiàn)這么多層并非僅僅靠做更多我們一直在做的事情就能實(shí)現(xiàn)。”

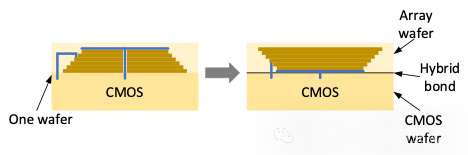

主要的傳統(tǒng)處理問(wèn)題與高縱橫比 (HAR) 蝕刻和沉積有關(guān),以確保所有這些層中的字符串一致且無(wú)空隙。由于多晶硅通道的總電阻增加,通道高度也對(duì)讀取電流構(gòu)成挑戰(zhàn)。因此,一些開(kāi)發(fā)人員正在轉(zhuǎn)向使用混合鍵合的雙晶圓解決方案,但這些改進(jìn)只能到此為止。

Brewer Science業(yè)務(wù)發(fā)展經(jīng)理 Daniel Soden 表示:“盡管尖端制造商始終致力于增加層數(shù),但層的額外擴(kuò)展/堆疊受到蝕刻預(yù)算和圖案化挑戰(zhàn)等因素的限制。”

但最快的方法(或許是唯一的方法)是串堆疊。

更多的比特

業(yè)界確實(shí)有辦法在不增加更多層的情況下增加內(nèi)存容量。“NAND 制造商不僅可以垂直擴(kuò)展,還可以橫向和邏輯擴(kuò)展,”Lam 的 Kim 說(shuō)。

邏輯縮放會(huì)增加單個(gè)閃存單元中存儲(chǔ)的位數(shù),而橫向縮放會(huì)減小單元之間的間距。此外,研究人員正在嘗試將列一分為二,使單元總數(shù)增加一倍。各種想法都在發(fā)揮作用,但效果將是降低間距并在相同區(qū)域存儲(chǔ)更多數(shù)據(jù)。“縮放這種電荷陷阱架構(gòu)的間距是提高設(shè)備上的電容器密度的好方法,而無(wú)需進(jìn)一步增加層數(shù),”Brewer 的 Soden 說(shuō)。

另一個(gè)容量提升涉及將更多數(shù)據(jù)打包到單個(gè)單元中。在一個(gè)單元中存儲(chǔ)多個(gè)位并不是一個(gè)新想法。各公司正在推出每單元兩位的多層單元 (MLC)、三層單元 (TLC) 和四層單元 (QLC)。開(kāi)發(fā)人員現(xiàn)在正在接近每單元五層(五層單元或 PLC)。管理如此微小的電荷狀態(tài)差異(31 個(gè)級(jí)別加上空)的算法可能會(huì)更復(fù)雜,糾錯(cuò)也是如此,因此性能可能會(huì)受到影響。

目前,PLC 的實(shí)現(xiàn)方式以及陷阱氧化物的成分尚不明確,一些研究表明,浮柵可能成為更好的 PLC 單元。甚至有人在研究六級(jí)單元 (HLC),每個(gè)單元存儲(chǔ)六位。然而,這仍在研究中。

SK 海力士有一種方法可以將存儲(chǔ)單元分成兩個(gè)三比特單元,總共六比特。七比特存儲(chǔ)單元已經(jīng)在低溫下進(jìn)行測(cè)試,以降低噪音并提高讀取保真度。

保持層均勻

堆疊 3D NAND 的基本優(yōu)勢(shì)在于,只需一個(gè)光刻步驟即可獲得數(shù)百層,從而對(duì)所有層進(jìn)行圖案化。缺點(diǎn)是鉆孔變得更加困難,尤其是當(dāng)高縱橫比接近 100:1 時(shí)。

讓每層變薄似乎有利于增加層數(shù),而不會(huì)使堆棧太高。“層厚度在 150 到 100 埃的范圍內(nèi),”Bhan 說(shuō)。但字線層的變薄會(huì)使它們的電阻更大,從而損害性能。一些研究人員正在探索用電阻更低的釕或鉬代替鎢金屬。但對(duì)于產(chǎn)品開(kāi)發(fā)來(lái)說(shuō),層厚度目前保持不變。

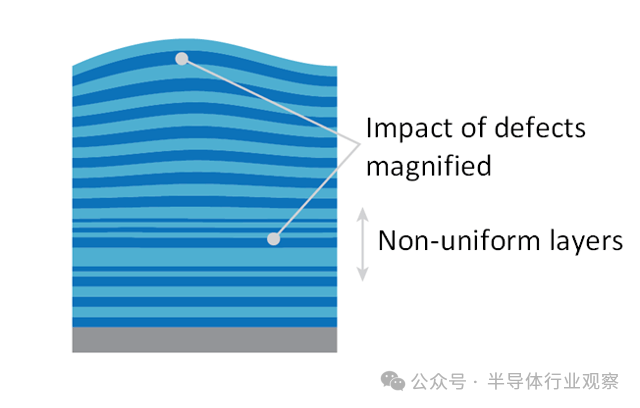

挑戰(zhàn)不僅僅在于蝕刻。在保持良好平面度的同時(shí)添加額外的層也更加困難。以前可以原諒的小錯(cuò)誤現(xiàn)在會(huì)累積起來(lái),在更高的堆棧頂部變得太大而無(wú)法忽略。

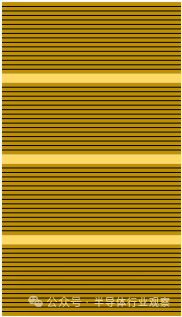

堆棧最初由交替的 SiO 2和 S 3 iN 4層組成,但氮化物最終將被移除并由柵極金屬代替。在每一代中,隨著堆棧的增長(zhǎng),重點(diǎn)仍然是保持各層盡可能均勻。可以容忍輕微的錯(cuò)誤,但隨著堆棧的增長(zhǎng),這些錯(cuò)誤往往會(huì)成倍增加,這意味著每一代都必須更加努力地提高平面度。

圖 1:3D NAND 堆棧的平面性和均勻性較差。

資料來(lái)源:ACM Research

在沉積過(guò)程中旋轉(zhuǎn)晶圓是 ACM Research 用來(lái)提高平面度的一項(xiàng)技術(shù)。隨著沉積的進(jìn)行,該公司的設(shè)備會(huì)定期抬起晶圓并將其旋轉(zhuǎn) 180°,就像足球隊(duì)每節(jié)改變方向一樣。“沉積過(guò)程中對(duì)晶圓旋轉(zhuǎn)的要求以及整個(gè)過(guò)程的均勻性將非常重要,”Bhan 說(shuō)。

為此,旋轉(zhuǎn)卡盤(pán)將晶圓從壓板上抬起,將其轉(zhuǎn)動(dòng)并放回原位。壓板被加熱,因此必須快速旋轉(zhuǎn)以保持晶圓溫度。但由于壓板是固定的,因此晶圓在沉積過(guò)程中無(wú)法連續(xù)(緩慢)轉(zhuǎn)動(dòng)。“我們 [定期] 旋轉(zhuǎn)晶圓以確保沉積更均勻,”Bhan 解釋說(shuō)。“我們已經(jīng)取得了相當(dāng)大的進(jìn)展,將均勻度控制在 1% 以內(nèi)。”

該公司還控制沉積壓力,以補(bǔ)償 Si 3 N 4中的拉應(yīng)力和 SiO 2中的壓應(yīng)力。

堆疊問(wèn)題

隨著堆疊層數(shù)的增加,潛在問(wèn)題也隨之增加。“堆疊高度越高,物理和熱應(yīng)力就越大,這會(huì)給光刻和其他下游工藝帶來(lái)更多挑戰(zhàn),”Brewer 公司的 Soden 指出。

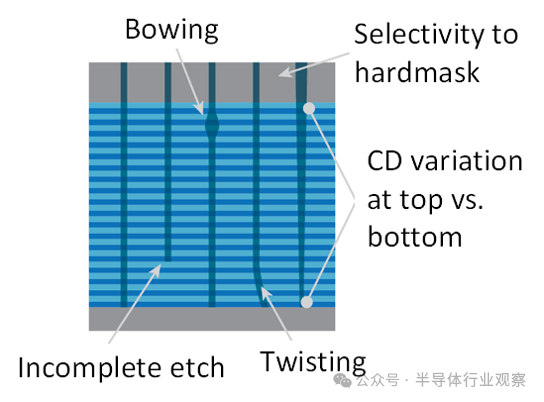

這在蝕刻過(guò)程中尤為明顯。原本應(yīng)該是筆直、均勻的柱狀物,卻可能因不同層上的橫向蝕刻速率不同、頂部和底部之間的臨界尺寸不同、蝕刻不完全,甚至柱狀物偏離中心而變形。

圖 2:隨著堆棧越來(lái)越高,蝕刻通道孔也會(huì)遇到越來(lái)越多的挑戰(zhàn)。資料來(lái)源:ACM Research

蝕刻工藝必須極其均勻,并且必須權(quán)衡利弊,以確保生產(chǎn)率不受影響。“如果我們真的想同時(shí)實(shí)現(xiàn)縱向和橫向微縮,我們不僅要提高蝕刻速率,還要改善輪廓控制,”Lam 的 Kim 說(shuō)。

有效的蝕刻要求定義堆疊頂部圖案的硬掩模保持良好的保真度。“正在研究更強(qiáng)大的圖案轉(zhuǎn)移解決方案,例如更厚的硬掩模和更內(nèi)在抗性的材料,”Soden 說(shuō)。目前使用的主要材料稱為α碳(一種無(wú)定形碳),它非常堅(jiān)硬。它通過(guò)化學(xué)氣相沉積 (CVD) 沉積而成。” Brewer Science 推出了一種它認(rèn)為同樣有效的材料,但它可以旋轉(zhuǎn),從而簡(jiǎn)化了流程。

“這種 [α-碳] 的密度和硬度是其強(qiáng)項(xiàng),可與鉆石媲美,并且非常適合蝕刻工藝,”Soden 說(shuō)道。“用旋涂材料取代這種材料和工藝可以帶來(lái)額外的靈活性、更高的產(chǎn)量、更好的間隙填充和其他特性,這些特性可以惠及我們行業(yè)的各種設(shè)備和領(lǐng)域。”

一旦蝕刻了柱子,就必須對(duì)其進(jìn)行清潔和干燥,這也變得更加困難。“一旦你完成了 HAR 蝕刻,讓柱子落到底部,就會(huì)有殘留物,”ACM Research 首席技術(shù)專家 Sally-Ann Henry 說(shuō)道。“問(wèn)題是,柱子的縱橫比非常深。我們的 [超聲波解決方案] 可以幫助將液體注入柱子,但如何將液體排出呢?你可能可以將水注入和排出,但干燥是一個(gè)大問(wèn)題。”

改進(jìn)這些步驟的技術(shù)包括使用超聲波攪拌將清潔材料推入柱的每個(gè)角落,以及使用超臨界 CO 2在清潔后將其干燥。CO 2的超臨界階段發(fā)生在高溫和高壓下,使材料具有氣體和液體的性質(zhì)。為了輔助,異丙醇既可以幫助在清潔前穩(wěn)定圖案,又可以幫助在清潔完成后沖洗腔室。

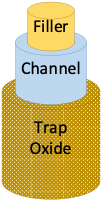

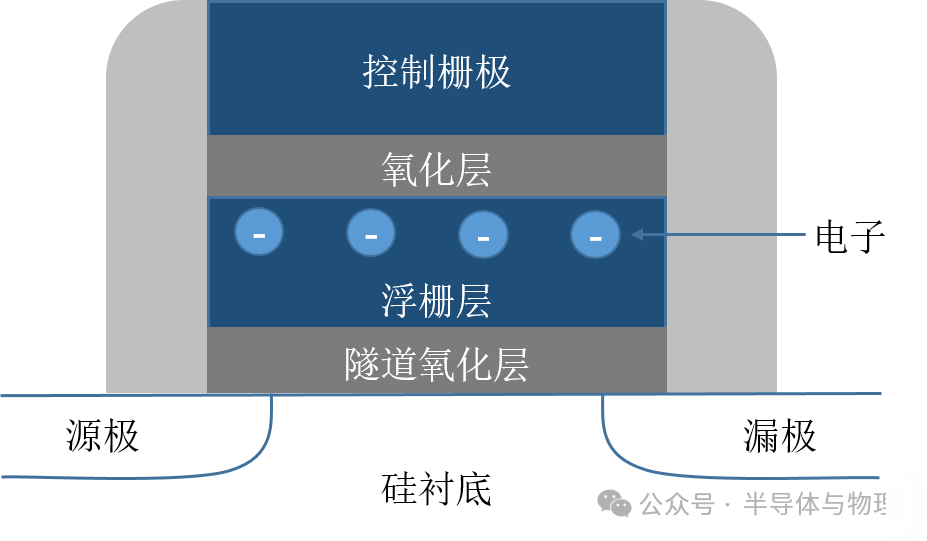

單晶通道

完全構(gòu)建并填充后,每個(gè)陣列柱形成所謂的 Macaroni 結(jié)構(gòu):同心排列,外部由陷阱氧化物組成,然后是通道材料,中間是惰性填充氧化物。陷阱氧化物是每個(gè)單元的電荷存儲(chǔ)位置。通道成為位線或串,將電流一直傳送到位線觸點(diǎn)。填充部分的目的只是使通道變窄,從而改善柵極控制。

圖 3:3D NAND 的 Macaroni 結(jié)構(gòu)。電荷存儲(chǔ)在陷阱氧化物中,通道形成位線。填充物的作用只是縮小通道以改善柵極控制。來(lái)源:Bryon Moyer/Semiconductor Engineering

通道本身通常是多晶硅,由于沿柱狀結(jié)構(gòu)存在許多晶粒邊界,因此具有一定的電阻性。盡管對(duì)于當(dāng)前幾代閃存來(lái)說(shuō),這種方法效果很好,但隨著堆棧越來(lái)越高,維持讀取電流直至接觸點(diǎn)變得越來(lái)越困難。出于這個(gè)原因,一些公司想出了生成單晶通道的方法。一種方法是從底部向上生長(zhǎng)硅。另一種方法是從頂部結(jié)晶多晶硅。

應(yīng)用材料公司指出,之前曾嘗試使用選擇性外延生長(zhǎng)來(lái)創(chuàng)建單晶通道。但為了在加工過(guò)程中保護(hù) CMOS 熱預(yù)算,生長(zhǎng)溫度為 810°C,導(dǎo)致生長(zhǎng)速度太慢,無(wú)法進(jìn)行批量生產(chǎn)。該公司可以在 900 至 1,100°C 的溫度下實(shí)現(xiàn)超過(guò) 400nm/min 的生長(zhǎng)速度。雖然這可能會(huì)給傳統(tǒng)的 3D NAND 加工帶來(lái)問(wèn)題,但一項(xiàng)新提出的技術(shù)可以實(shí)現(xiàn)這一點(diǎn)——在不同的晶圓上構(gòu)建存儲(chǔ)單元和邏輯并將它們混合鍵合在一起。

一種稱為 CMOS 下方(或下方)陣列(或 CBA/CUA)的配置將單元陣列放置在一個(gè)晶圓上,將其余的 CMOS 電路放置在另一個(gè)晶圓上。兩者使用混合鍵合結(jié)合在一起。由于鍵合的面對(duì)面性質(zhì),陣列和階梯現(xiàn)在顛倒過(guò)來(lái),并且接觸可以短得多,這本身就是一個(gè)好處。

圖 4:CMOS 陣列配置。單元結(jié)構(gòu)構(gòu)建在一個(gè)晶圓上,倒置,然后混合鍵合到包含 CMOS 電路的晶圓上,縮短連接并允許陣列晶圓采用更高溫度的工藝步驟。來(lái)源:Bryon Moyer/Semiconductor Engineering

但就外延生長(zhǎng)而言,這允許陣列晶圓在高于 CMOS 所能承受的溫度下生長(zhǎng)外延,從而提供一種制造單晶通道的方法。然而,由此產(chǎn)生的一個(gè)變化是,由于通道占據(jù)了圓柱體的整個(gè)中部,填充氧化物消失了。這導(dǎo)致柵極控制減少,這是一個(gè)代價(jià)。改進(jìn)的單晶通道性能需要產(chǎn)生更大的積極影響,才能使這種權(quán)衡值得。

雙晶圓技術(shù)的成本也高得多。但它是獨(dú)立于外延生長(zhǎng)技術(shù)開(kāi)發(fā)的,以便騰出陣列用于任何其他不利于 CMOS 的工藝。同樣數(shù)量的閃存芯片也需要兩倍的晶圓。這涉及到成本、晶圓需求和環(huán)境問(wèn)題。

對(duì)于此應(yīng)用,陣列載體晶圓中的硅不會(huì)被消耗。所有有用的層都沉積在該晶圓的頂部。將兩個(gè)晶圓粘合后,典型的方法是研磨或蝕刻掉載體晶圓,這會(huì)浪費(fèi)硅并增加成本。目前正在努力研究哪種技術(shù)可以修復(fù)回收晶圓的表面,使其與新晶圓一樣有效。

自上而下的方法

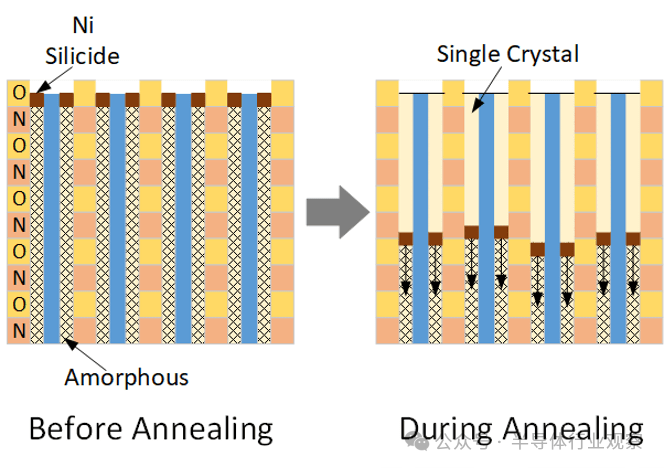

創(chuàng)建這種通道的另一種方法不需要兩個(gè)晶圓。相反,通道中填充多晶硅,就像傳統(tǒng)做法一樣。然而,在退火之前,鎳硅化物會(huì)沉積在通道上。在退火過(guò)程中,該硅化物會(huì)從頂部向下浮動(dòng),沿途催化結(jié)晶。當(dāng)它到達(dá)底部時(shí),其上方的所有東西都是單晶。硅化物仍位于底部,但位線觸點(diǎn)位于頂部,因此不會(huì)造成問(wèn)題(假設(shè)它保持在原位)。

圖 5:使用鎳硅化物結(jié)晶通道。退火過(guò)程中,材料沿通道向下遷移,沿途結(jié)晶多晶硅。來(lái)源:Bryon Moyer/半導(dǎo)體工程

堆疊并重復(fù)

最后增加層數(shù)可以在一定程度上扭轉(zhuǎn)處理越來(lái)越深的孔洞所取得的緩慢進(jìn)展,無(wú)論是從物理上還是從地緣政治上。上面討論的改進(jìn)有助于提高容量,但只能提高到一定程度。

“隨著層數(shù)達(dá)到 250 以上,這些解決方案可能已接近極限,”Soden 指出。“正在實(shí)施分步方法,將圖案和蝕刻處理分解為不同的模塊,以減少極端 HAR 蝕刻,在層之間引入裸硅并通過(guò)通孔方法進(jìn)行連接。”

有時(shí)也被稱為串堆疊,其理念是構(gòu)建一組可管理的層,而不是試圖使該堆疊更高,只需將堆疊彼此復(fù)制,并在每層堆疊之間添加一層硅即可。結(jié)果可以組合更多層,而不會(huì)出現(xiàn)所有擴(kuò)展的 HAR 問(wèn)題。“這種解決方案是推動(dòng)許多公司長(zhǎng)期推進(jìn)多達(dá) 1,000 層的原因,”Soden 說(shuō)。

圖 6:串堆疊。每組層都獨(dú)立地經(jīng)過(guò)正常過(guò)程。堆疊獨(dú)立的串可以實(shí)現(xiàn)更多層,而無(wú)需在一個(gè)步驟中處理整個(gè)堆棧。代價(jià)是需要多個(gè)步驟。來(lái)源:Bryon Moyer/Semiconductor Engineering

工程解決方案是,人們可以得到 1,000 層,而不必將它們一起處理。相反,人們可以處理 250 層,然后堆疊四個(gè)模塊,中間插入硅層。代價(jià)是需要四個(gè)光刻步驟,而不是一個(gè),但這可能是一個(gè)合適的權(quán)衡。似乎沒(méi)有人討論嘗試以老式的方式處理 1,000 層。

這并不像聽(tīng)起來(lái)那么簡(jiǎn)單,因?yàn)榈诙訉⒎旁诘谝粚又希皇欠旁谝粔K平坦的晶圓上。第三層必須在第二層上積累的任何不規(guī)則之處上工作。很可能每一層都需要單獨(dú)的開(kāi)發(fā)工作來(lái)確保足夠的平面度。

另一個(gè)挑戰(zhàn)是,每層中的串必須以某種方式連接起來(lái)才能形成一個(gè)長(zhǎng)串。簡(jiǎn)單的答案是在硅隔離層中放置一個(gè)通孔,但將每一層與前一層精確對(duì)齊并不明顯——尤其是因?yàn)楣鑼訒?huì)阻擋下面的列的可見(jiàn)性。

從地緣政治角度來(lái)看,出口規(guī)則限制堆疊層數(shù)超過(guò) 128 層。因此,受這些限制的國(guó)家只需堆疊 128 層模塊即可繞過(guò)這一限制。例如,如果長(zhǎng)江存儲(chǔ)(該公司是首家推出串式堆疊產(chǎn)品的公司)要實(shí)現(xiàn) 1,000 層,它很可能會(huì)使用 10 個(gè) 100 層的堆疊來(lái)實(shí)現(xiàn)這一目標(biāo)。

解決這一問(wèn)題需要幾年時(shí)間

NAND 閃存改進(jìn)涉及許多活動(dòng)部件。改進(jìn) HAR 處理的努力將繼續(xù),但這并不是最大的收獲。理論上,PLC 技術(shù)可立即提高 25% 的容量。單元架構(gòu)的改變和間距的減小可以帶來(lái)更多幫助。

最大的變化是轉(zhuǎn)向雙晶圓解決方案和堆疊串的重大架構(gòu)轉(zhuǎn)變。它們可以與其他容量提升一起出現(xiàn)。采用這兩種技術(shù)的產(chǎn)品目前都有,盡管不是 1,000 層。降低 CBA 成本是實(shí)現(xiàn)普及的必要條件,而且需要努力擴(kuò)展堆疊層的數(shù)量。

目前主流配置究竟是什么樣子還不清楚,但無(wú)論如何,更大容量的 NAND 閃存芯片將滿足業(yè)界對(duì)于存儲(chǔ)的無(wú)盡需求。

-

NAND

+關(guān)注

關(guān)注

16文章

1719瀏覽量

137821 -

3D

+關(guān)注

關(guān)注

9文章

2952瀏覽量

109475 -

堆疊

+關(guān)注

關(guān)注

0文章

37瀏覽量

16813

原文標(biāo)題:NAND的新目標(biāo),1000層

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

預(yù)期提前,鎧俠再次加速,3D NAND準(zhǔn)備沖擊1000層

英倫科技在光場(chǎng)裸眼3D顯示技術(shù)領(lǐng)域取得的成就和未來(lái)發(fā)展方向

TechWiz LCD 3D應(yīng)用:局部液晶配向

技術(shù)前沿:半導(dǎo)體先進(jìn)封裝從2D到3D的關(guān)鍵

TechWiz LCD 3D應(yīng)用:局部液晶配向

MLOps平臺(tái)的發(fā)展方向

uvled光固化3d打印技術(shù)

【半導(dǎo)體存儲(chǔ)】關(guān)于NAND Flash的一些小知識(shí)

3D-NAND浮柵晶體管的結(jié)構(gòu)解析

智能駕駛的未來(lái)發(fā)展方向

AGV的發(fā)展方向

3D NAND的發(fā)展方向是500到1000層

3D NAND的發(fā)展方向是500到1000層

評(píng)論