ESD 是指處于不同電位的兩個物體之間,由于直接接觸或靜電場感應導致的電荷傳輸現(xiàn)象。在電子設備中,ESD 可能會對敏感的電子元件造成損害,因此提高ESD抗擾度對于保證電子設備的正常運行至關重要。預防措施能夠將 ESD 抗擾度提高到約 15kV,這表明通過合理的設計和防護,可以有效降低 ESD 對電子模塊的影響

二、ESD問題應對措施

ESD 測試只能在成品部件上進行,這是因為只有在整個部件完成開發(fā)和生產(chǎn)后,才能準確地評估其在實際工作環(huán)境中的ESD抗擾度。這也意味著在產(chǎn)品開發(fā)過程中,需要提前規(guī)劃和考慮ESD防護措施,以避免在測試階段出現(xiàn)問題而導致成本增加和時間延誤.

1、改進IC設計:IC 制造商可以通過改進 IC 的設計來提高其ESD抗擾度。例如,采用更先進的ESD保護技術、優(yōu)化電路布局和增加ESD保護器件等。這可以在一定程度上降低 ESD故障的發(fā)生概率,但需要在 IC 設計和制造過程中進行大量的研究和投入.

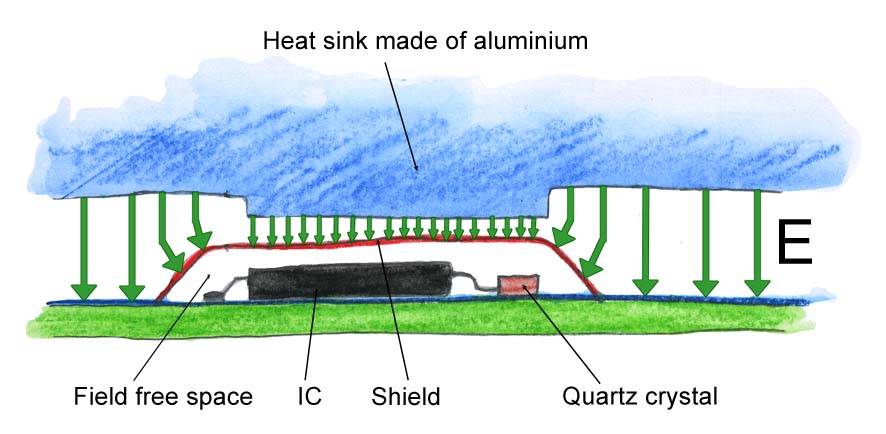

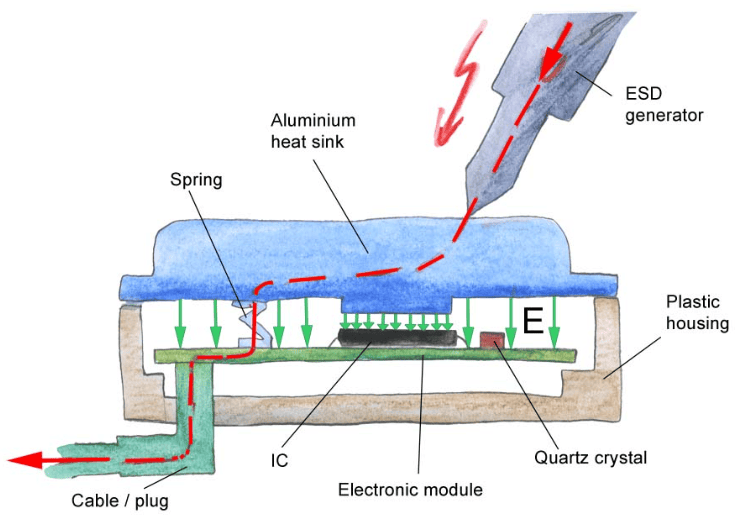

2、優(yōu)化機械結構設計:在機械結構設計中采取適當?shù)?a href="http://www.asorrir.com/tags/emc/" target="_blank">EMC預防措施也可以減少ESD對集成電路的影響。當 ESD干擾源自散熱器并直接作用于IC外殼時,改變機械設計是解決問題的有效方法。這可能包括重新設計散熱器的結構、位置或材料,以減少其對 IC 的干擾。然而,這種方法需要更改機械結構部件和生產(chǎn)工具,成本較高。因此,在產(chǎn)品設計的早期階段,了解 IC 的電磁兼容性特性,并采取相應的預防措施,可以避免在后期出現(xiàn)此類問題,從而降低成本和縮短開發(fā)周期.

3、增加屏蔽:集成電路(IC)周圍增加屏蔽罩、濾波電路等,以減少電磁干擾的耦合和傳播。這需要在設計階段就充分考慮 EMC 問題,并與電子設計人員進行密切合作。

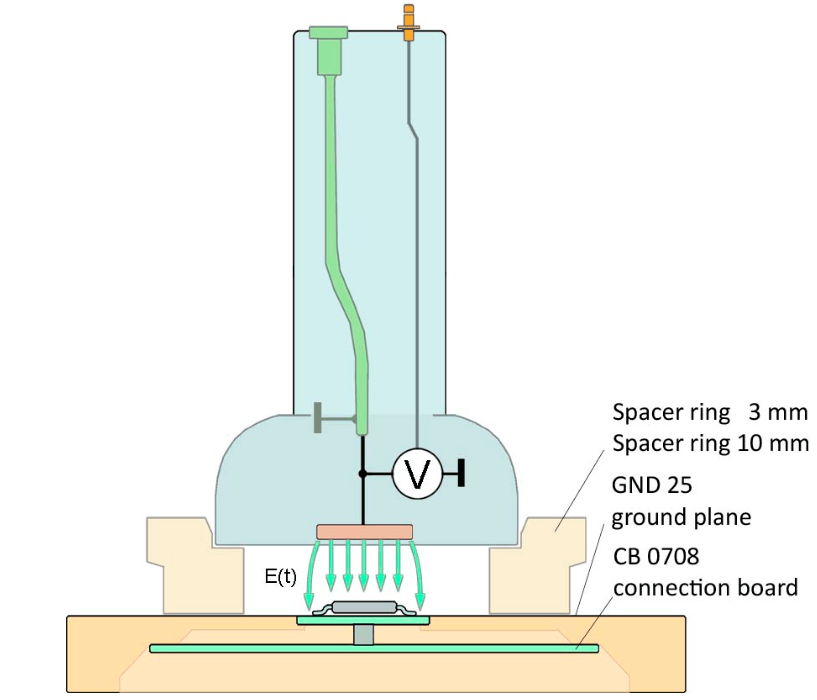

圖3用場源檢測到的微控制器的易感區(qū)域比如,為了提高 ESD 免疫力,可以在 IC 上方設置屏蔽罩,以攔截散熱片發(fā)出的電場,(如圖3所示),在進行靜電放電(ESD) 測試中,屏蔽罩還必須延伸到石英晶體上。從而將 ESD 免疫力提高到大約 15kV 左右。不過,需要注意的是,IC中的其他薄弱點可能會限制進一步提高免疫力,因為干擾仍可能通過線路網(wǎng)絡耦合到 IC。因此在電子設備的設計中,需要綜合考慮各種因素,不能僅僅依賴屏蔽層來解決電磁兼容性問題。

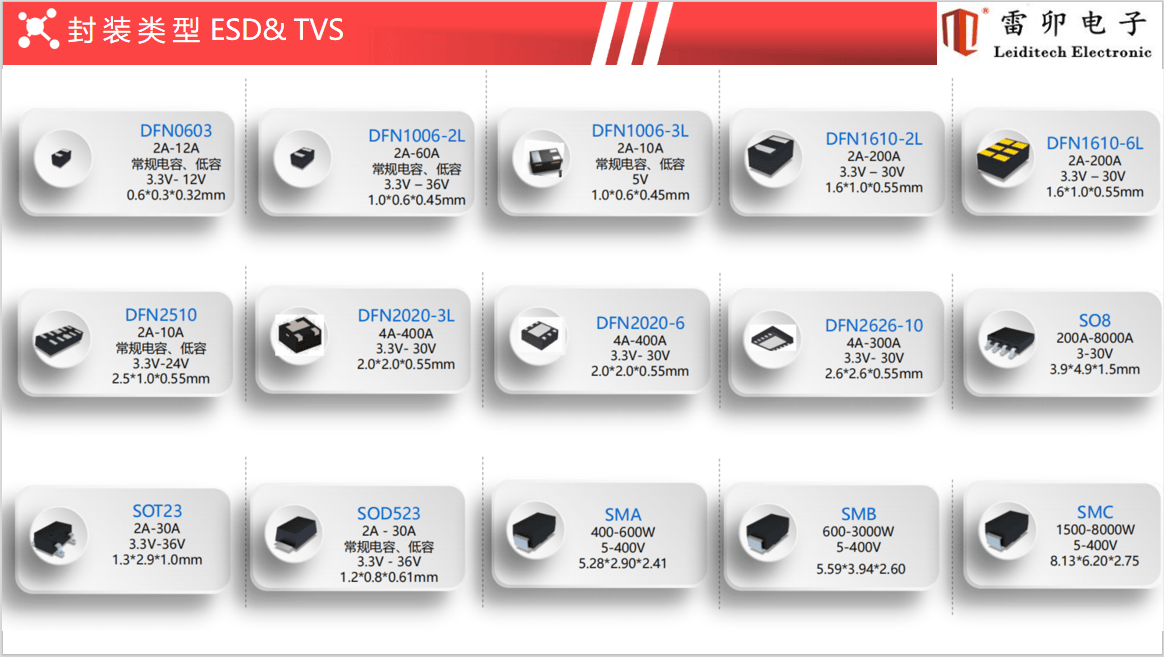

如果IC外部需要增加ESD二極管保護,可以聯(lián)系上海雷卯銷售人員或EMC小哥。

3、加強測試和評估:為了確保IC的 EMC 性能,需要進行嚴格的測試和評估。這包括 ESD 測試、電磁兼容性測試等,以驗證集成電路在各種電磁環(huán)境下的性能和可靠性。通過測試,可以及時發(fā)現(xiàn)問題并采取相應的改進措施,從而提高集成電路的質量和穩(wěn)定性。

下一篇將接著分享《集成電路ESD測試和評估》,歡迎各位關注。

Leiditech雷卯電子致力于成為電磁兼容解決方案和元器件供應領導品牌,供應ESD,TVS,TSS,GDT,MOV,MOSFET,Zener,電感等產(chǎn)品。雷卯擁有一支經(jīng)驗豐富的研發(fā)團隊,能夠根據(jù)客戶需求提供個性化定制服務,為客戶提供最優(yōu)質的解決方案。

審核編輯 黃宇

-

集成電路

+關注

關注

5418文章

11943瀏覽量

367073 -

ESD

+關注

關注

49文章

2265瀏覽量

175115 -

電磁兼容性

+關注

關注

6文章

464瀏覽量

34096

發(fā)布評論請先 登錄

中國集成電路大全 接口集成電路

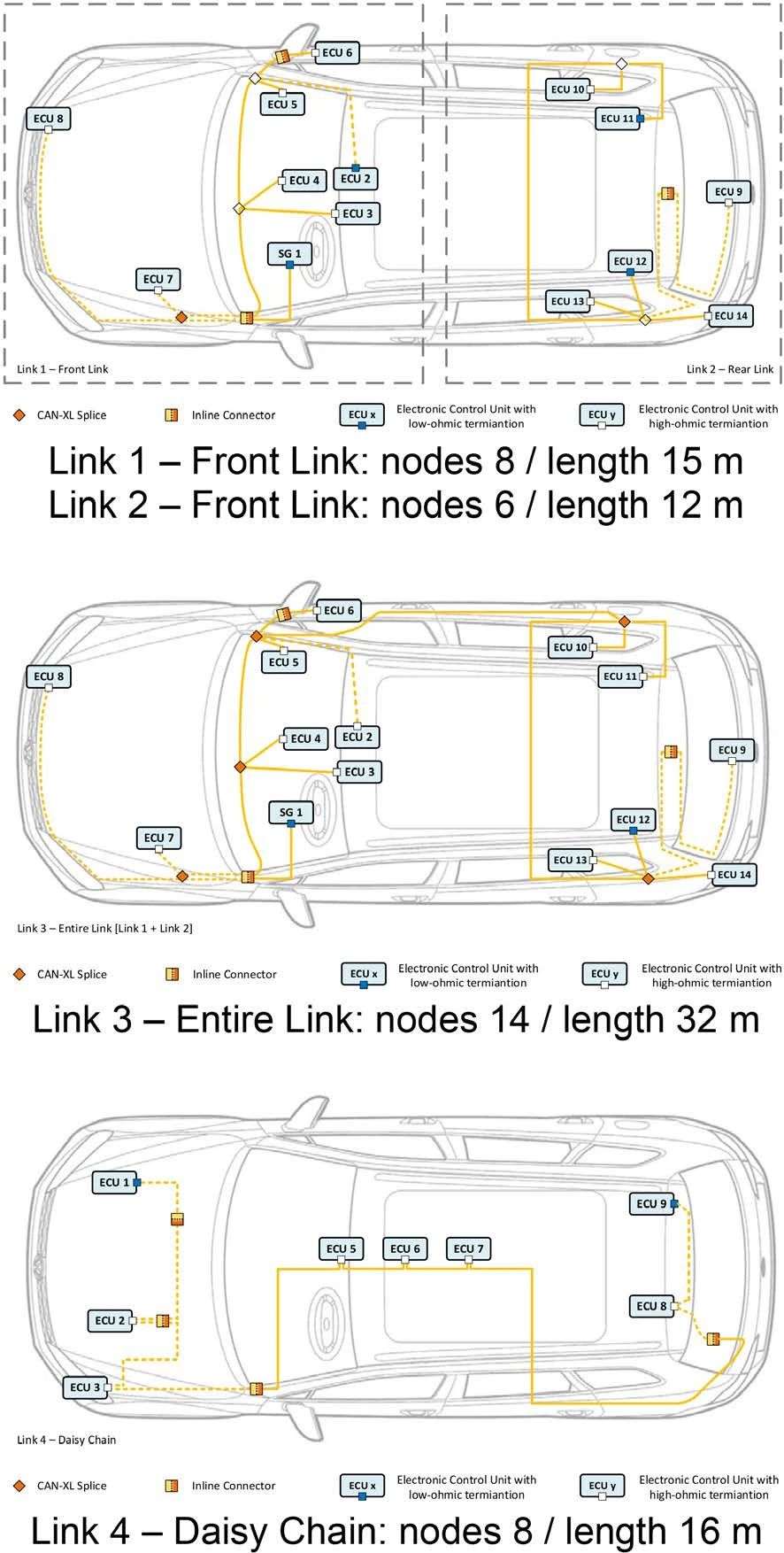

虹科干貨 車規(guī)級CAN XL的電磁兼容性能研究

電磁兼容性原理與設計

開關電源的PCB版圖設計及其電磁兼容分析(建議下載!)

科研分享|智能芯片與異構集成電路電磁兼容問題

集成電路為什么要封膠?

集成電路新建項目機電二次配制定減震措施的流程是怎樣的?

集成電路電磁兼容性及應對措施相關分析(三)集成電路ESD 測試與分析

集成電路電磁兼容性及應對措施相關分析(三)—集成電路ESD 測試與分析

什么是集成電路?有哪些類型?

語音集成電路有哪些特點

音響集成電路是數(shù)字集成電路嗎

綜合電磁兼容性設計與測試方法及案例分析

集成電路電磁兼容性及應對措施相關分析(二)—集成電路ESD問題應對措施

集成電路電磁兼容性及應對措施相關分析(二)—集成電路ESD問題應對措施

評論