教你如何使用Xilinx SDSoC

實現(xiàn)在ARTY Z7上進行軟硬協(xié)同設計

細心的小伙伴們可能早已留意到,在Digilent今年全新出品的Zynq評估板中,無論是第二代經(jīng)典入門級的Zynq? Board -ZYBO Z7,還是創(chuàng)客最愛的ARTY Z7,都全面支持Xilinx SDSoC開發(fā)環(huán)境。意味著如果你是一名系統(tǒng)或軟件工程師,現(xiàn)在無需深度的硬件專業(yè)知識,就能廣泛地利用Zynq? SoC,暢享超過100倍的軟件性能加速。

本篇干貨教程中,我們就將帶你入門了解如何使用Xilinx SDSoC工具來創(chuàng)建嵌入式C/C++/OpenCL應用開發(fā),并實現(xiàn)直接在ARTY Z7嵌入式視覺開發(fā)平臺的器件上進行軟件設計。

01

SDSoC軟硬協(xié)同設計與其開發(fā)流程

由于集成了ARM處理器內(nèi)核與可編程邏輯,對于眾多應用開發(fā)而言,Zynq 非常的靈活。這意味著開發(fā)人員可以將設計按不同的元素來優(yōu)化劃分,例如將其中那些高層次決策的部分放入ARM內(nèi)核(PS端),并將諸如圖像處理流水線等需要加速的部分用可編程邏輯(PL端)來實現(xiàn)。

當然,傳統(tǒng)的Zynq開發(fā)流程會將Vivado和SDK分離開來,這種方法很難在可編程邏輯(PL)和處理系統(tǒng)(PS)之間分配功能,因此無法獲得最優(yōu)的系統(tǒng)性能。

通過SDSoC,則可以解決上述問題。SDSoC是一個系統(tǒng)最優(yōu)編譯器,支持軟件定義的整個系統(tǒng)開發(fā),包括PS和PL。標準的SDSoC開發(fā)流程如下:

-

使用高層次語言開發(fā)應用

-

使用提供的性能監(jiān)視器來分析設計從而確定性能瓶頸

-

使用SDSoC將造成性能瓶頸的功能用可編程邏輯來實現(xiàn)加速

-

重新驗證性能,如果有必要也可以加速其它功能模塊

正是因為高層次綜合(HLS)和互聯(lián)框架的結合才使得各種功能模塊可以在PS和PL之間輕松的轉換:

-

使用Vivado HLS加速某個功能模塊

-

分析通信功能

-

建立AXI通信

-

生成軟件存根

為了能夠使可編程邏輯獲得最佳的性能,我們需要給加速的功能模塊定義一些優(yōu)化參數(shù),這樣才能夠確定HLS工具執(zhí)行哪些優(yōu)化操作。我們可以使用高層次語言(比如C/C++/OpenCL)來開發(fā)基于Zynq的設計。為了支持SDSoC的使用,我們需要一個面向SDSoC的基礎平臺來定義底層硬件和軟件環(huán)境。

對于Arty Z7,點擊「閱讀原文」,在“下載代碼”按鈕中可以找到Arty Z7對應的SDSoC基礎平臺,下載之后就可以在Arty Z7上開發(fā)相關的應用了。

02

創(chuàng)建一個新的SDSoC工程

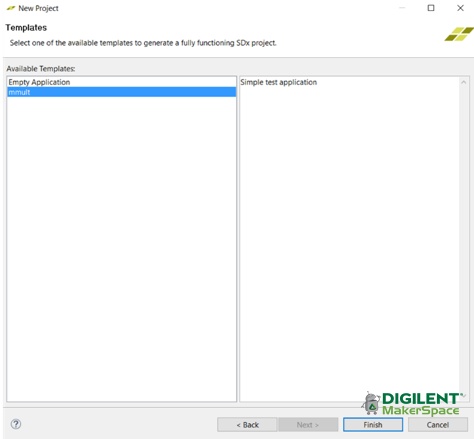

在這一教程中,我們將探究如何使用SDSoC平臺來加速矩陣乘法的性能。

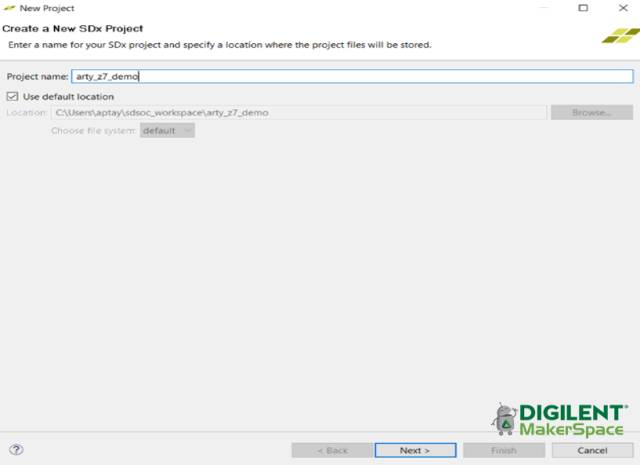

使用SDSoC工具創(chuàng)建一個新的SDSoC工程,具體操作步驟如下:File -> New -> Xilinx SDx Project。這會打開一個新工程的對話框,包括支持的平臺規(guī)范、操作系統(tǒng)選擇和示例應用選擇。詳細圖解如下。

創(chuàng)建一個新工程:

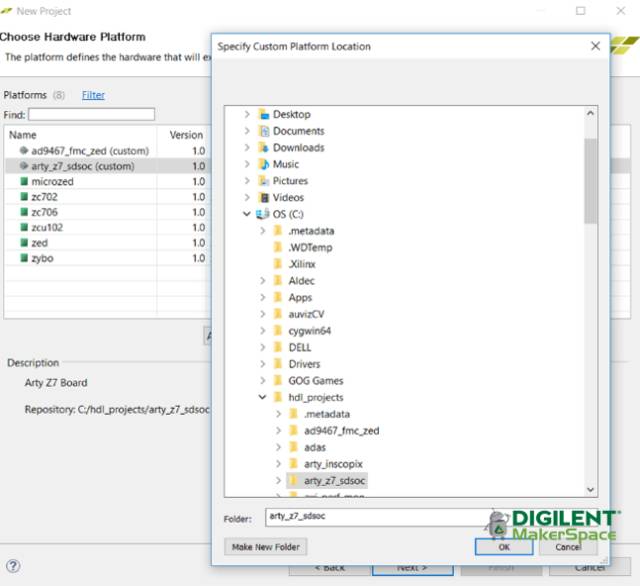

選擇Arty7 Z7-20作為硬件平臺。這里,在新工程對話框的第二頁選擇一個新的平臺,點擊添加自定義平臺選項(add custom platform)。然后對應找到已下載好的Arty Z7-20平臺,添加好后這個平臺就能在構建列表中看到,在此基礎上我們可以選擇它應用到我們的工程中:

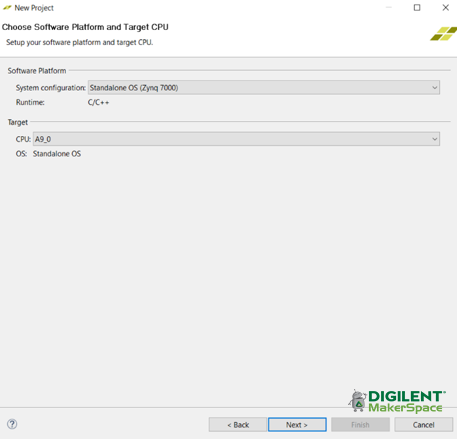

選擇操作系統(tǒng)(OS)和目標CPU:

然后選擇示例應用:

03

SDx項目設置頁面

完成項目新建之后,將在SDSoC開發(fā)環(huán)境中看到SDx項目設置頁面。我們使用這個項目設置選項卡可以在PS和PL之間轉移功能。實現(xiàn)方式是:選擇“Add HW Function”按鈕,然后選擇所需要移植到PL中的功能。

如果我們想將原本在PS中運行的功能轉移到PL中來實現(xiàn)加速,那么我們應當遵循以下幾條規(guī)則:

-

這個功能不能包含任何操作系統(tǒng)級的系統(tǒng)調(diào)用

-

這個功能必須完整

-

C結構體需要有界并固定大小

-

結構體的實現(xiàn)是明確的

在項目設置控制面板上,我們也可以控制加速模塊和PL與PS之間數(shù)據(jù)移動網(wǎng)絡傳遞數(shù)據(jù)的操作頻率。

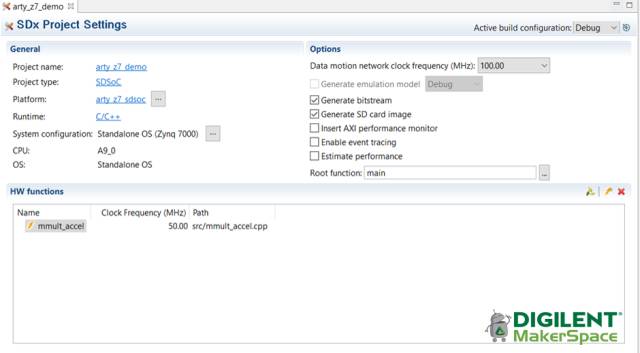

SDSoC Project Settings – 此界面顯示的是SDSoC主要的控制功能:

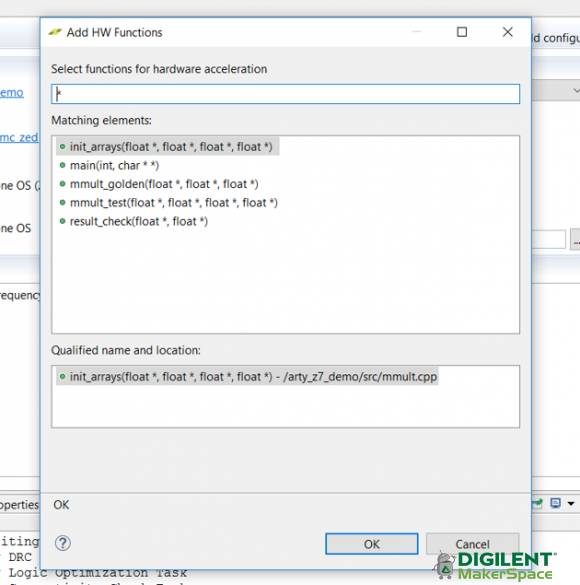

Add HW Function界面 – 顯示可以用于加速的函數(shù):

04

預估性能選項與啟動調(diào)試器

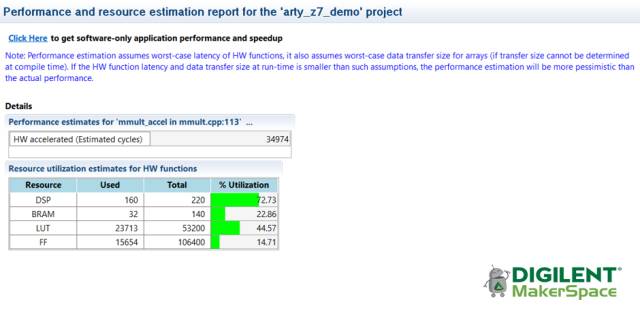

當SDSoC構建時會生成必要的bin文件,我們可以將其放到SD卡中來啟動運行或者下載到Zynq中用于調(diào)試。構建過程需要一定的時間,因此在很多情況下當我們選擇一個函數(shù)用于加速時,我們可以先運行一個功能,估計一下需要的總資源和預期的加速效果。通過在項目設置菜單中點擊“估計性能(estimate performance)”選項就可以實現(xiàn)上述這一步。

整個構建過程完成后就會生成一個結果報告,估計運行結果界面如下圖:

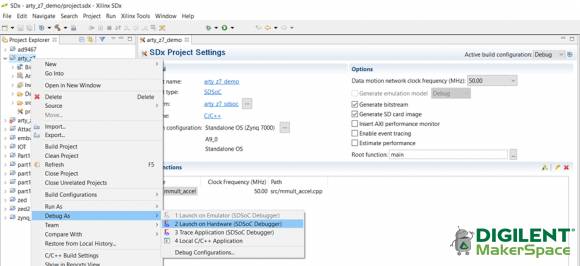

如果我們構建這個設計時沒有點擊預估性能選項,那么我們可以使用調(diào)試器(debugger)像正常應用那樣下載和運行示例程序。要想啟動調(diào)試器,在工程上右擊,然后選擇Debug As ->Launch on Hardware(SDSoC Debugger)。參考下圖啟動調(diào)試界面,這里我們會將應用下載到Arty Z7,并在編程入口使Zynq掛起。將SDSoC終端與Arty Z7 UART(串口)連接我們就可以看到示例程序的運行結果:

05

利用好SDSoC開發(fā)環(huán)境中庫的優(yōu)勢

當我們開發(fā)自己的SDSoC應用時,我們需要了解SDSoC提供的庫和加速棧資源。

為了幫助開發(fā)者能夠更快地開發(fā)最終應用,SDSoC提供了一些HLS庫,開發(fā)者可以將其應用到自己的設計中,具體包括:

-

reVison Stack– 提供了一個三元素開發(fā)棧,我們可以使用OpenCV、Caffe和一系列通用的神經(jīng)網(wǎng)絡開源框架到嵌入式視覺應用中。reVision包括多重加速能力的OpenCV。

-

數(shù)學庫– 提供了標準數(shù)據(jù)庫可綜合的實現(xiàn)。

-

IP庫– 提供了可以實現(xiàn)FFT、FIR和移位寄存器LUT功能的IP庫。

-

線性代數(shù)庫– 提供了通用線性代數(shù)功能的庫資源。

-

任意精度數(shù)據(jù)類型庫– 提供無二次冪和有符號/無符號整數(shù)任意數(shù)據(jù)長度的支持,這個庫可以讓開發(fā)者更加高效的使用FPGA資源。

06

總結

通過這個項目中的例子,我們看到借助SDSoC,我們可以在PS與PL之間輕松地轉移軟件(SW)函數(shù),并通過將之轉移到PL端來實現(xiàn)性能上的提升。

So,如果此刻,你已經(jīng)對利用SDSoC來實現(xiàn)軟硬協(xié)同開發(fā)與優(yōu)化產(chǎn)生了興趣,趕快拿起一塊Arty Z7,參照著教程嘗試一下快感吧!

-

ARM

+關注

關注

134文章

9349瀏覽量

377321 -

嵌入式

+關注

關注

5149文章

19655瀏覽量

317316 -

Xilinx

+關注

關注

73文章

2184瀏覽量

125261

原文標題:在Arty Z7上入門Xilinx SDSoC開發(fā)工具

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

Perforce QAC產(chǎn)品簡介:面向C/C++的靜態(tài)代碼分析工具(已通過SO 26262認證)

嵌入式軟件開發(fā)常用的軟件有哪些?

嵌入式開發(fā)入門指南:從零開始學習嵌入式

如何成為一名嵌入式軟件工程師?

Python在嵌入式系統(tǒng)中的應用場景

源代碼加密、源代碼防泄漏c/c++與git服務器開發(fā)環(huán)境

使用SEGGER工具實現(xiàn)嵌入式應用開發(fā)

為什么嵌入式驅動開發(fā)工程師可以拿高薪?

新手怎么學嵌入式?

一文了解嵌入式軟件開發(fā)的對象

如何利用SDSoC工具來創(chuàng)建嵌入式C/C++/OpenCL應用開發(fā)

如何利用SDSoC工具來創(chuàng)建嵌入式C/C++/OpenCL應用開發(fā)

評論