PCB( Printed Circuit Board),中文名稱(chēng)為印制電路板,又稱(chēng)印刷線路板,是重要的電子部件,是電子元器件的支撐體,是電子元器件電氣連接的載體。由于它是采用電子印刷術(shù)制作的,故被稱(chēng)為“印刷”電路板。

在任何電源設(shè)計(jì)中,PCB板的物理設(shè)計(jì)都是最后一個(gè)環(huán)節(jié),其設(shè)計(jì)方法決定了電磁干擾和電源穩(wěn)定,下面具體分析一下這些環(huán)節(jié):

一、從原理圖到PCB板的設(shè)計(jì)流程:建立元件參數(shù)→輸入原理網(wǎng)表→設(shè)計(jì)參數(shù)設(shè)置→手工布局→手工布線→驗(yàn)證設(shè)計(jì)→復(fù)查→CAM輸出。

二、參數(shù)設(shè)置相鄰導(dǎo)線間距必須能滿足電氣安全要求,而且為了便于操作和生產(chǎn),間距也應(yīng)盡量寬些。最小間距至少要能適合承受的電壓,在布線密度較低時(shí),信號(hào)線的間距可適當(dāng)?shù)丶哟螅瑢?duì)高、低電平懸殊的信號(hào)線應(yīng)盡可能地短且加大間距,一般情況下將走線間距設(shè)為8mil。焊盤(pán)內(nèi)孔邊緣到印制板邊的距離要大于1mm,這樣可以避免加工時(shí)導(dǎo)致焊盤(pán)缺損。當(dāng)與焊盤(pán)連接的走線較細(xì)時(shí),要將焊盤(pán)與走線之間的連接設(shè)計(jì)成水滴狀,這樣的好處是焊盤(pán)不容易起皮,而且走線與焊盤(pán)不易斷開(kāi)。

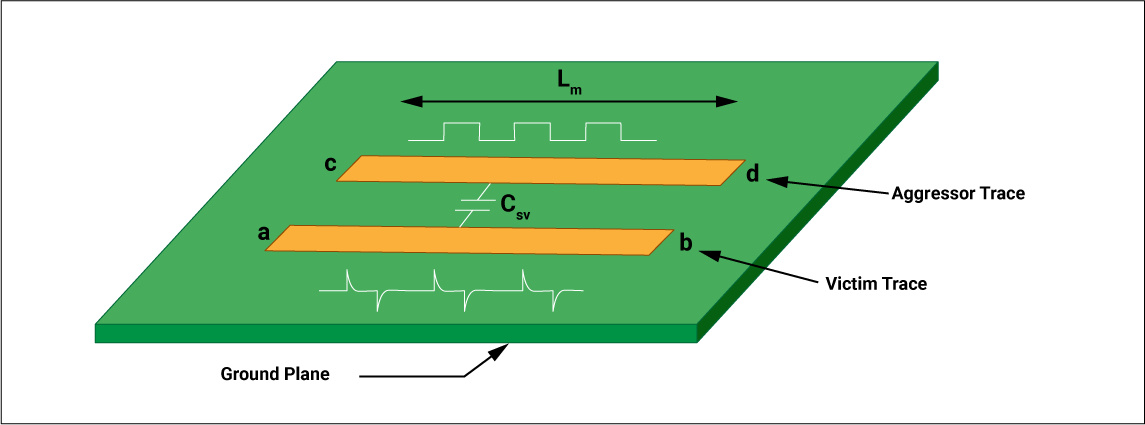

三、元器件布局實(shí)踐證明,即使電路原理圖設(shè)計(jì)正確,印制電路板設(shè)計(jì)不當(dāng),也會(huì)對(duì)電子設(shè)備的可靠性產(chǎn)生不利影響。例如,如果印制電路板兩條細(xì)平行線靠得很近,則會(huì)形成信號(hào)波形的延遲,在傳輸線的終端形成反射噪聲;由于電源、地線的考慮不周到而引起的干擾,會(huì)使產(chǎn)品的性能下降。因此,在設(shè)計(jì)印制電路板的時(shí)候,應(yīng)注意采用正確的方法。

四、布線開(kāi)關(guān)電源中包含有高頻信號(hào),PCB板上任何印制線都可以起到天線的作用,印制線的長(zhǎng)度和寬度會(huì)影響其阻抗和感抗,從而影響頻率響應(yīng)。即使是通過(guò)直流信號(hào)的印制線也會(huì)從鄰近的印制線耦合到射頻信號(hào)并造成電路問(wèn)題(甚至再次輻射出干擾信號(hào))。

五、檢查布線設(shè)計(jì)完成后,需認(rèn)真檢查布線設(shè)計(jì)是否符合設(shè)計(jì)者所制定的規(guī)則,同時(shí)也需確認(rèn)所制定的規(guī)則是否符合印制電路板生產(chǎn)工藝的需求,一般檢查線與線、線與元件焊盤(pán)、線與貫通孔、元件焊盤(pán)與貫通孔、貫通孔與貫通孔之間的距離是否合理,是否滿足生產(chǎn)要求。電源線和地線的寬度是否合適,在PCB板中是否還有能讓地線加寬的地方。還要注意的是,有些錯(cuò)誤不可以忽略,例如有些接插件的Outline的一部分放在了板框外,檢查間距時(shí)會(huì)出錯(cuò);另外每次修改過(guò)走線和過(guò)孔之后,都要重新覆銅一次。

六、復(fù)查根據(jù)“PCB板檢查表”,內(nèi)容包括設(shè)計(jì)規(guī)則,層定義、線寬、間距、焊盤(pán)、過(guò)孔設(shè)置,還要重點(diǎn)復(fù)查器件布局的合理性,電源、地線網(wǎng)絡(luò)的走線,高速時(shí)鐘網(wǎng)絡(luò)的走線與屏蔽,去耦電容的擺放和連接等。

-

pcb

+關(guān)注

關(guān)注

4352文章

23406瀏覽量

406650 -

開(kāi)關(guān)電源

+關(guān)注

關(guān)注

6500文章

8543瀏覽量

488467 -

電源電壓

+關(guān)注

關(guān)注

3文章

1121瀏覽量

24587 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2378瀏覽量

106296

發(fā)布評(píng)論請(qǐng)先 登錄

電磁干擾的PCB設(shè)計(jì)方法

如何避免開(kāi)關(guān)電源設(shè)計(jì)中PCB電磁干擾

減小PCB設(shè)計(jì)的電磁干擾的方法及注意事項(xiàng)

如何在PCB設(shè)計(jì)中避免出現(xiàn)電磁問(wèn)題

如何避免在PCB設(shè)計(jì)中出現(xiàn)電磁問(wèn)題

分析抑制電源模塊電磁干擾的幾種方法

PCB設(shè)計(jì)中如何避免出現(xiàn)電磁問(wèn)題

PCB設(shè)計(jì)中如何避免出現(xiàn)電磁問(wèn)題?

避免在PCB設(shè)計(jì)中出現(xiàn)電磁問(wèn)題的7個(gè)技巧

PCB設(shè)計(jì)避免電磁干擾和穩(wěn)定電源電壓電流的幾種常見(jiàn)方法

PCB設(shè)計(jì)避免電磁干擾和穩(wěn)定電源電壓電流的幾種常見(jiàn)方法

評(píng)論