SOC(System on Chip,芯片上的系統(tǒng))芯片的測(cè)試是一個(gè)復(fù)雜且全面的過程,涉及多個(gè)參數(shù)和模塊。以下是對(duì)SOC芯片測(cè)試的主要參數(shù)和模塊的歸納:

一、測(cè)試參數(shù)

- 電性能測(cè)試 :

- 性能測(cè)試 :

- 內(nèi)存帶寬 :衡量芯片處理數(shù)據(jù)的能力。

- CPU執(zhí)行速度 :反映芯片處理指令的速度。

- 功耗 :在不同工作模式和負(fù)載下的功耗表現(xiàn)。

- 其他特定參數(shù) :

- 靜態(tài)電流 :在靜態(tài)條件下的電流,用于檢測(cè)漏電流和短路故障。

- 低功耗模式測(cè)試 :在不同低功耗模式下的電流消耗。

- 靜電放電(ESD)耐受性 :通過人體放電模型(HBM)、機(jī)器放電模型(MM)等方法測(cè)試。

二、測(cè)試模塊

SOC芯片的測(cè)試模塊通常與其內(nèi)部集成的功能模塊相對(duì)應(yīng),包括但不限于:

- 處理器內(nèi)核測(cè)試 :

- 測(cè)試CPU的執(zhí)行速度、指令集支持情況等。

- 內(nèi)存測(cè)試 :

- 接口控制器測(cè)試 :

- 模擬電路測(cè)試 :

- 數(shù)字電路測(cè)試 :

- 包括邏輯電路的測(cè)試,如掃描測(cè)試(SCAN)、自動(dòng)測(cè)試向量生成(ATPG)、邏輯內(nèi)建自測(cè)試(LBIST)等。

- 邊界掃描測(cè)試 :

- 低功耗模式測(cè)試 :

- 測(cè)試芯片在不同低功耗模式下的功耗和性能表現(xiàn)。

- 靜電放電(ESD)測(cè)試 :

- 測(cè)試芯片對(duì)靜電的耐受性,確保其在靜電環(huán)境下能夠正常工作。

三、測(cè)試階段

SOC芯片的測(cè)試通常分為以下幾個(gè)階段:

- 晶圓測(cè)試(Wafer Test) :

- 包括WAT(Wafer Acceptance Test)和CP(Chip Probe)測(cè)試,用于在封裝前篩選出有問題的芯片。

- 最終測(cè)試(Final Test,F(xiàn)T) :

- 在芯片封裝后進(jìn)行的最終測(cè)試,確保芯片在用戶模式下所有功能正常。

- 板級(jí)測(cè)試(Board Test) :

- 將芯片安裝在電路板上后進(jìn)行的測(cè)試,以驗(yàn)證其在系統(tǒng)環(huán)境中的表現(xiàn)。

四、測(cè)試挑戰(zhàn)與未來趨勢(shì)

SOC芯片測(cè)試面臨著復(fù)雜性增加、成本控制、低功耗測(cè)試、測(cè)試自動(dòng)化等挑戰(zhàn)。未來趨勢(shì)包括利用人工智能和機(jī)器學(xué)習(xí)技術(shù)提高測(cè)試效率和覆蓋率、通過大數(shù)據(jù)分析優(yōu)化測(cè)試流程、在片測(cè)試(On-Chip Testing)等。

綜上所述,SOC芯片的測(cè)試是一個(gè)多維度、多階段的復(fù)雜過程,需要綜合考慮多個(gè)參數(shù)和模塊以確保芯片的質(zhì)量和性能。

-

模塊

+關(guān)注

關(guān)注

7文章

2783瀏覽量

49623 -

參數(shù)

+關(guān)注

關(guān)注

11文章

1867瀏覽量

32871 -

SoC芯片

+關(guān)注

關(guān)注

1文章

636瀏覽量

35667 -

漏電流

+關(guān)注

關(guān)注

0文章

273瀏覽量

17374

發(fā)布評(píng)論請(qǐng)先 登錄

片上芯片SoC挑戰(zhàn)傳統(tǒng)測(cè)試方案

SoC系統(tǒng)級(jí)芯片

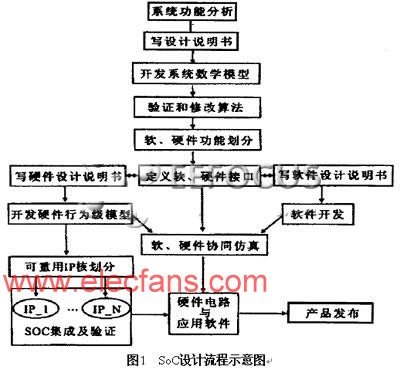

SoC芯片的開發(fā)流程有哪幾個(gè)階段

SoC和在線測(cè)試的好處

SOC測(cè)試訪問機(jī)制

基于IP核的SOC中ADC的測(cè)試技術(shù)

SoC系統(tǒng)知識(shí)與設(shè)計(jì)測(cè)試

SOC芯片的DFT策略的可測(cè)試性設(shè)計(jì)

soc芯片如何測(cè)試 soc是處理器嗎 soc是數(shù)字芯片還是模擬芯片

chiplet和soc有什么區(qū)別?

SoC芯片設(shè)計(jì)中的可測(cè)試性設(shè)計(jì)(DFT)

IGBT模塊測(cè)試:重要?jiǎng)討B(tài)測(cè)試參數(shù)介紹

芯片電學(xué)測(cè)試是什么?都有哪些測(cè)試參數(shù)?

一文了解SOC的DFT策略及全芯片測(cè)試的內(nèi)容

soc芯片測(cè)試有哪些參數(shù)和模塊

soc芯片測(cè)試有哪些參數(shù)和模塊

評(píng)論