確保多重 FPGA 電軌依正確順序關閉,跟確保開機程序是否正確一樣重要,可避免裝置因電壓狀態無法判斷而提早出現故障。

電源定序的安全考慮

在啟動目前的大型系統單芯片 FPGA 的多重電軌時,有許多技巧可用來控制其啟動順序和時序。遵照裝置制造商所指定的正確順序甚為重要,如此可避免裝置抽取過多電流而導致損壞。

有些方法是透過操縱各轉換器的電源良好輸出,來控制順序中下一個供應的 Enable 腳位。如需要繼電器,可插入電容器。另一種類似的方式則是使用重置 IC,在前一個供電達到所要求的電壓后啟動下一個轉換器。每種方法都有一些缺點,且這些方法都無法控制電源關閉的順序。依正確的相反順序關閉電軌,跟開啟電源順序是否正確一樣重要,都是為了確保裝置能安全運作。

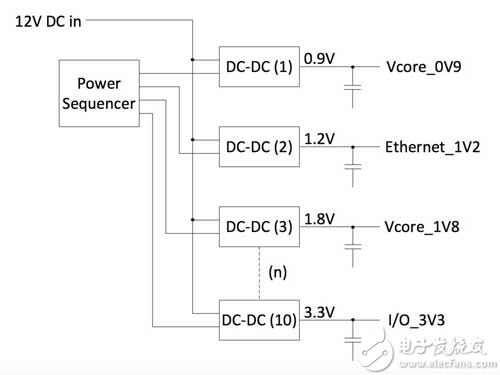

使用專用的電源定序 IC,則更能穩定確保其順序正確。IC 可程序化,在所要的時間點分別傳送 Enable 訊號。圖 1 顯示多信道序列發生器如何管理 FPGA 核心邏輯、周邊和 I/O 電域。即使如此,電源關閉順序仍舊難以控制,因為每個電軌上的去耦合電容器在轉換器關閉后仍可能殘留電荷,且殘留時間不一定,而每個電軌最多可能連接多達 20mF 的總去耦合電容。

圖 1. 透過定序 IC 管理 FPGA 電軌。

電源關閉控制

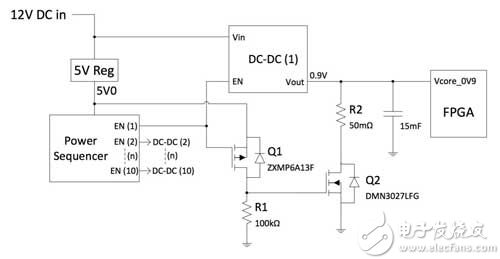

使用具有已知時間常數的電路,主動將去耦合電容器放電,序列發生器便能維持正確的電源關閉順序,其做法是在串聯的電容器中暫時插入放電電阻器。圖 2 顯示如何在加入最少必要組件下,使用一對細心挑選的 MOSFET 將電阻器插入電路中。

電源序列發生器的 EN 輸出連接到 DC-DC 穩壓器的 Enable 腳位,也連接到 P 通道 MOSFET (Q1) 的閘極。序列發生器輸出降低停用 DC-DC 穩壓器時,Q1 便會反轉訊號,開啟 N 信道 MOSFET Q2。開啟時,Q2 會透過 R2 電阻使 15mF 去耦合電容器放電到接地。

圖 2. 控制電源定序的主動放電電路。

圖中的電路假設 DC-DC 穩壓器在提供關機訊號后無法持續產生輸出。假如 DC-DC 穩壓器的輸出能在收到關機指令后持續供應電源,則需要額外的繼電器才能啟動放電電路。

選擇的 R2 值必須能確保適當的放電時間,讓序列發生器能在可接受的時間間隔內完成關機。另外還要注意的是,電阻必須夠大,才能避免電流尖峰值上升率過快,避免引發 EMI 問題,以及對 Q2 和去耦合電容器組造成瞬態熱應力。實務上,選擇 R2 值時需考慮一些額外的重要參數,像是 Q2 的導通電阻 (RDS(ON)) 和電容器組的等效串聯電阻 (ESR)。

選擇 MOSFET Q1 時應參考電源序列發生器的輸出電壓閾值。所選的裝置應有夠高的閘極閾值電壓 (VGS(th)),確保序列發生器輸出為高電位時能保持關閉,但要注意的是,VGS(th) 會隨接面溫度上升而下降。本范例中選擇的序列發生器操作供應電壓為 5V,最小指定高電位輸出電壓為 4.19V。Q1 的 VGS(th) 在 60°C 環境操作溫度下必須大于 0.9V,以確保運作正常。此外,閘極應使用 100k? 電阻下拉至源極電位,以避免誤開。查看 MOSFET 數據表中 VGS(th) 與溫度的標準化曲線,顯示 Diodes 公司的 ZXMP6A13F 符合要求:保證最小 VGS(th) 在室溫下為 1V,到 60°C 則下降至 0.9V 左右。

在此范例中,我們假設序列發生器必須在 100ms 內關閉總共 10V 的電軌。因此,每個電軌的去耦合電容器組必須在 10ms 內完成放電。目標是達成 RC 時間常數 8ms 的 3 倍,確保電容器在要求時間內放電到全電壓的 5% 以下。計算 RC 常數時,電容器組的 MOSFET RDS(ON)、寄生線路電阻和 ESR 都必須與電阻器 R2 一同納入考慮。

假設電容器 ESR 和線路電阻加起來不超過 10m?,去耦合電容器組的總電容值為 15mF,則 RDS(ON) 和 R2 的適當值可用下列表達式求得:

3 x (10mΩ + R2 + (1.5 x RDS(ON))) x 15mF = 8ms

假設 R2 = 50mΩ,功率 MOSFET Q2 的 RDS(ON) 在 VGS = 4.5V 且環境溫度為 25?C 下必須小于 80mΩ。

選擇 MOSFET 時,溫度相關變動的效應和 RDS(ON) 的批量變異也應考慮在內。RDS(ON) 在 4.5V 閘極驅動下、超出預期作業溫度范圍時的變異可能高達 15mΩ。因此最好的做法是,確定 R2 為所選 MOSFET 之制造商指定最大 RDS(ON) 的兩倍左右。如果 R2 為 50m?,則可選用 Diodes 公司的 DMN3027LFG N 通道 MOSFET。此裝置在 VGS = 4.5V、室溫下的 RDS(ON) 典型值和最大值分別為 22m? 和 26.5m?。因此,RDS(ON) 變化可從 15mΩ 到 40mΩ,放電時間從 95% (3 倍 RC) 的 3.9ms 起跳,使用最差 20mF 大小的電容器組時放電時間則可能拉長到 5.4ms。

MOSFET 夠耐用嗎?

DMN3027LFG 會隨時間以電流和電壓為函數消耗電容器內的能源,因此有需要評估最大單一脈沖,讓功率 MOSFET 能夠安全應付,同時確保接面溫度不會超過絕對最高額定典型值 TJ(max) = 150°C。相關詳細資料可查看 MOSFET 數據表中的安全操作區 (SOA)。SOA 應以所需的 MOSFET 閘極驅動器應用的環境操作溫度為基礎。在使帶 0.9V 電荷的電容器組放電時,可接受的 SOA 曲線應指出單一脈沖尖峰電流量為至少 1V,脈沖寬度介于 1ms 至 10ms。SOA 應適用于一般的應用環境溫度,安裝在使用最少散熱器 (亦稱最小建議墊片 (MRP) 配置) 下的電路板上時,亦即假設的 60°C。

此外也需要考慮 DMN3027LFG (Q2) MOSFET 和 R2 串聯電阻的功耗。最糟的使用情況,就是在很短的時間內對電容器進行充放電。假設最糟情況下,電源序列發生器可進入連續回路,每隔 20ms 啟動一次 DC-DC 穩壓器并接著停用 (10ms 啟用 + 10ms 停用),DMN3027LFG 和 R2 將會有大約 0.5W 的功耗。這是從電容器組儲存的已知總能源會每隔 20ms 放電計算得到:

P = E ÷ t = ?CV2 ÷ 20ms = 500mW (假設 C = 20mF,充電至 1V)

DMN3027LFG 的最大溫度調整 RDS(ON) 為 40mΩ,因此 Q2 和 R2 的功耗分別為 222mW 和 278mW。若 RDS(ON) 為較低的 15mΩ,R2 的功耗將增加到 385mW,因此需使用 0.5W 額定值的電阻。

在一般應用中,環境溫度預期接近 60°C,而 DMN3027LFG 在最小建議墊片配置下的接面至環境熱電阻 (RθJA) 為 130°C/W,功耗達 222mW 時 TJ 接近 90°C。這表示 TJ(max) = 150°C 還有很多預留空間。

圖 3 顯示電路實際運作方式。尖峰電流限制在大約 12.5A,電容器組從初始 1V 充電狀態下放電至 5% 的時間約為 4ms,此數值接近理論值的計算結果。

圖 3.在控制時間和限制放電電流下關閉單一電軌。

結論

依照正確順序關閉個別電源供應,跟確定開機順序是否正確一樣重要,都是為了避免復雜的多軌式 FPGA 損壞。讓去耦合電容器主動放電,有助于穩定確保每個電軌能在已知的時間內關閉。在選擇主動放電電路的組件,也就是主要的串聯電阻器和主要 MOSFET 開關時,應確保組件具備適當的時間常數,且能耐受最糟的電源循環條件下所造成的應力。

-

FPGA

+關注

關注

1643文章

21933瀏覽量

612985 -

FPGA器件

+關注

關注

1文章

22瀏覽量

11742

發布評論請先 登錄

IGBT器件的防靜電注意事項

手機喇叭氣密性檢測儀的注意事項

功放電路電源設計注意事項

運放電路設計注意事項有哪些

ADS8528、ADS8548和ADS8568時序注意事項

設計fpga穩定電源定序的注意事項

設計fpga穩定電源定序的注意事項

評論