LPC175x作為NXP公司主推的cortex-M3內(nèi)核芯片,廣泛應(yīng)用于各工控、電子計(jì)量、報(bào)警系統(tǒng)等領(lǐng)域,無論何種應(yīng)用,根據(jù)實(shí)際需求選擇合適的時(shí)鐘源并配置合理的系統(tǒng)時(shí)鐘頻率都是必不可少的。

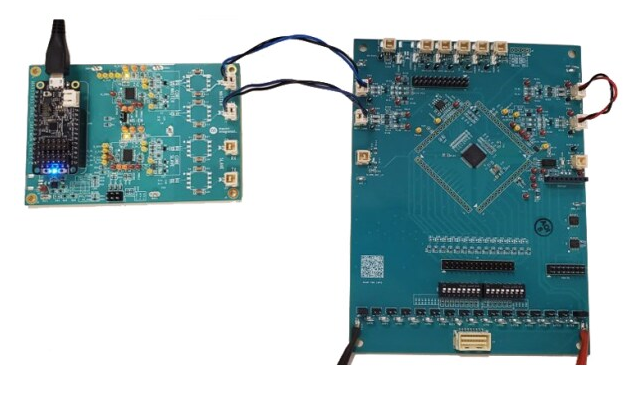

以EasyARM-1754M3開發(fā)板為例,LPC1754芯片外部晶體振蕩器包含兩個(gè),一個(gè)頻率為12MHz外部高速晶振和一個(gè)頻率為32.768KHz的外部低速晶振,兩個(gè)都可以使用軟件設(shè)置選用或不選用。此外LPC1754內(nèi)部也包含三個(gè)獨(dú)立的振蕩器,他們分別是內(nèi)部主振蕩器,內(nèi)部RC振蕩器和內(nèi)部RTC振蕩器。實(shí)際應(yīng)用當(dāng)中常用的振蕩器是外部高速晶體振蕩器,和外部低速晶體振蕩器。

LPC1754內(nèi)部PLL0原理簡介

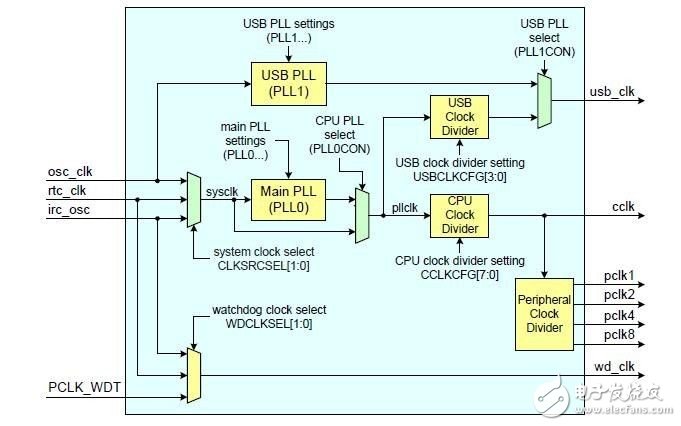

PLL0包含多個(gè)寄存器,其中PLL0時(shí)鐘源的選擇可在CLKSRCSEL寄存器中設(shè)置,PLL0將輸入時(shí)鐘進(jìn)行倍頻,然后再分頻為CPU及芯片外設(shè)提供實(shí)時(shí)時(shí)鐘信號。PLL0可產(chǎn)生的時(shí)鐘頻率最高可達(dá)100MHz,是CPU所允許的最大值。

PLL0內(nèi)部結(jié)構(gòu)可表示為下圖,PLL0的輸出時(shí)鐘信號即為pllclk,后經(jīng)過CPU時(shí)鐘分頻器的分頻,產(chǎn)生系統(tǒng)時(shí)鐘,系統(tǒng)時(shí)鐘再進(jìn)入外設(shè)時(shí)鐘分頻器后輸出多路的外設(shè)時(shí)鐘。

應(yīng)用舉例

EasyARM-1754M3開發(fā)板配套的所有例程使用統(tǒng)一的系統(tǒng)初始化函數(shù)SystemInit()將系統(tǒng)時(shí)鐘配置為96MHz,外設(shè)時(shí)鐘配置為默認(rèn)值24MHz。用戶可在對此函數(shù)有一定理解的條件下,根據(jù)自身實(shí)際需求,對參數(shù)進(jìn)行修改,可修改項(xiàng)一般包含時(shí)鐘源、倍頻系數(shù)、分配系數(shù)三個(gè)重要參數(shù),系統(tǒng)初始化函數(shù)當(dāng)中的PLL0配置部分如下程序清單所示:

#if (CLOCK_SETUP) /* Clock Setup */

LPC_SC->SCS = SCS_Val;

if (SCS_Val & (1 << 5)) {????????????????????????????? ?????/* If Main Oscillator is enabled? */

while ((LPC_SC->SCS & (1<<6)) == 0);???????????? ????????/* Wait for Oscillator to be ready*/

}LPC_SC->CCLKCFG = CCLKCFG_Val; /* 系統(tǒng)時(shí)鐘分頻值,CCLKCFG_Val值可改 */

LPC_SC->PCLKSEL0 = PCLKSEL0_Val; /* Peripheral Clock Selection */

LPC_SC->PCLKSEL1 = PCLKSEL1_Val;

LPC_SC->CLKSRCSEL = CLKSRCSEL_Val; /* 選取時(shí)鐘源,CLKSRCSEL_Val值可改 */

#if (PLL0_SETUP)

LPC_SC->PLL0CFG = PLL0CFG_Val; /*PLL0倍頻值,PLL0CFG_Val值可改 */LPC_SC->PLL0CON = 0x01; /* PLL0 Enable */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC->PLL0FEED = 0x55;

while (!(LPC_SC->PLL0STAT & (1<<26)));????????????? ??????/* Wait for PLOCK0?????????????? */

LPC_SC->PLL0CON = 0x03; /* PLL0 Enable & Connect */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC->PLL0FEED = 0x55;

#endifLPC_SC->PCONP = PCONP_Val; /* Power Control for Peripherals */

LPC_SC->CLKOUTCFG = CLKOUTCFG_Val; /* Clock Output Configuration */

#endif其中關(guān)鍵參數(shù)為PLL0倍頻系數(shù)PLL0CFG_Val、CPU時(shí)鐘分頻系數(shù)CCLKCFG_Val,由于寄存器值比實(shí)際值小1,因此它們實(shí)際值為16和4。另外每次想PLL0相關(guān)寄存器寫入新的數(shù)值時(shí),需要向饋送寄存器當(dāng)中寫入饋送系列以后才能生效,通常是將0xAA和0x55先后寫入PLLxFEED寄存器。

將相關(guān)參數(shù)準(zhǔn)備好之后,就要根據(jù)參數(shù)配置,判斷選中的時(shí)鐘源,并通過計(jì)算得出最后的系統(tǒng)時(shí)鐘頻率。在選用外部12MHz時(shí)鐘源的條件下,程序會跳轉(zhuǎn)到CASE1的位置運(yùn)行,并結(jié)合此前所給參數(shù),計(jì)算出系統(tǒng)時(shí)鐘頻率CCLK=12M×2×16/1/4=96MHz。

case 1: /* Main oscillator => PLL0 */

SystemFrequency = (OSC_CLK *

((2 * ((LPC_SC->PLL0STAT & 0x7FFF) + 1))) / /*PLL0STAT的低15位是15,倍頻值*/

(((LPC_SC->PLL0STAT >> 16) & 0xFF) + 1) / /*PLL0STAT的16~23位是0,分頻值*/

((LPC_SC->CCLKCFG & 0xFF)+ 1)); /*CCLKCFG是系統(tǒng)分頻值,3 */

break;又例如使用32.768KHz的外低速晶振作為時(shí)鐘源,并同樣產(chǎn)生96MHz的系統(tǒng)時(shí)鐘,只需將CLKSRCSEL_Val、CCLKCFG_Val、PLL0CFG_Val分別改為0x02、0x02、0x1127(4391)即可,含義分別是選擇外部低速晶振,系統(tǒng)分頻為3(寄存器值比實(shí)際值小1),PLL0倍頻值為4392(而PLL0分頻值不設(shè),默認(rèn)為0),計(jì)算:32.768×2×4392÷3=95944.704KHz,

約為96MHz。

時(shí)鐘配置注意事項(xiàng)

在整個(gè)代碼編寫過程中要格外注意對饋送寄存器PLLxFEED的操作,要嚴(yán)格遵循0xAA和0x55先后寫入的順序。另外要確保執(zhí)行寫入饋送序列時(shí),不會出現(xiàn)任何一個(gè)中斷服務(wù)程序,即在執(zhí)行PLL0饋送操作時(shí),必須禁止中斷,如果寫入的值不正確、或者沒有滿足無中斷發(fā)生的條件,那么對PLL0CFG寄存器的更改都不會生效。

在根據(jù)自身需求配置所需系統(tǒng)時(shí)鐘頻率時(shí),往往會使用仿真器的Debug功能,觀測相關(guān)參數(shù),以驗(yàn)證時(shí)鐘頻率配置的正確與否。但不能在執(zhí)行PLL0饋送操作時(shí),設(shè)置任何斷點(diǎn),否側(cè)同樣無法使配置生效。

-

LPC

+關(guān)注

關(guān)注

8文章

137瀏覽量

78382 -

NXP

+關(guān)注

關(guān)注

61文章

1347瀏覽量

189331 -

寄存器

+關(guān)注

關(guān)注

31文章

5434瀏覽量

124439 -

lpc1754

+關(guān)注

關(guān)注

0文章

1瀏覽量

1853

原文標(biāo)題:多種選擇—輕松配置LPC175x系統(tǒng)時(shí)鐘-ZLG技術(shù)研發(fā)中心

文章出處:【微信號:Zlgmcu7890,微信公眾號:周立功單片機(jī)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Analog Devices Inc. ADES1754 評估套件數(shù)據(jù)手冊

PLL用法

如何使用GPIO IRQ從Deep sleep喚醒LPC1768?

LT1754SI N溝道增強(qiáng)型功率MOSFET規(guī)格書

LT1754SIX N溝道增強(qiáng)型功率MOSFET規(guī)格書

LT1754SI-X N溝道增強(qiáng)型功率MOSFET規(guī)格書

DAC8311電源5V供電,sync/sclk/din引腳可否用3.3v驅(qū)動?

NXP1754調(diào)試TPL0401A,在發(fā)送命令(0x00)時(shí)總是沒有應(yīng)答,為什么?

DAC5687沒有設(shè)置差分,采用的等效單端,那么內(nèi)部PLL可以工作嗎?

請問PCM1754是只支持44.1KHz的采樣頻率?

使用內(nèi)部PLL同步多個(gè)并行器件

LPC1754內(nèi)部PLL0原理及應(yīng)用設(shè)計(jì)詳解

LPC1754內(nèi)部PLL0原理及應(yīng)用設(shè)計(jì)詳解

評論