在現代電子信號傳輸領域,差分信號因其出色的抗干擾能力和良好的信號質量而被廣泛應用于模擬信號傳輸中。然而,在使用差分信號時,我們必須注意共模電壓范圍的問題,以及對信號的適當處理和調節,以確保信號傳輸的準確性和穩定性。

差分信號優勢分析

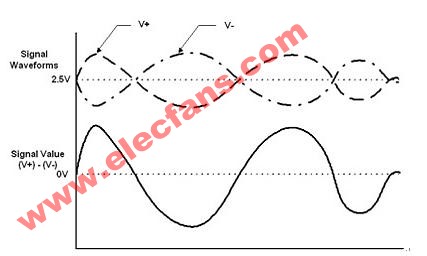

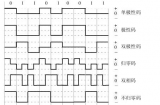

差分信號在模擬信號傳輸中的優勢主要體現在其對電源紋波和其他干擾的良好抵抗能力。在如橋式應變片式力傳感器等應用中,輸出信號可能非常微弱,滿量程時僅有2mV。在這種情況下,使用單端信號傳輸極易受到電源紋波的影響,導致信號失真。因此,差分信號成為更佳的選擇,通過儀表運算放大器進行信號放大和處理,可以有效保證信號的準確傳輸。

使用差分信號時的注意事項

1. 共模電壓范圍

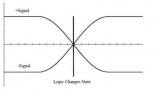

使用差分信號時,必須特別注意共模電壓范圍的問題。共模電壓是指兩根信號線上相對于系統地的電壓,這個電壓不能過大。例如,傳輸0.1V的信號是可行的,但如果一根線是1000.0V而另一根線是1000.1V,則可能導致問題。在許多場合下,使用差分信號的目的是為了避免兩個系統之間的地直接連接,因此需要采取措施抑制共模電壓。

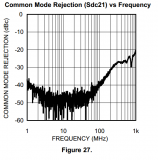

2. 共模電壓的抑制方法

為了抑制共模電壓,可以采用簡單的電路設計:將兩根信號線通過足夠大的電阻連接到系統的地上。這類似于放風箏時手中握著線,雖然在地上跑跳不會影響風箏的高度,但始終在控制范圍之內。在電子領域中,這個控制范圍被稱為共模電壓范圍。

單端轉差分信號的轉換方法

常見的方法是使用儀表運算放大器配合普通運算放大器搭建單端轉差分的電路。儀表運算放大器在處理差分信號方面具有強大的能力,可以有效地將單端信號轉換為高質量的差分信號,同時避免不必要的信號放大。

-

電路

+關注

關注

173文章

6022瀏覽量

174392 -

差分信號

+關注

關注

4文章

387瀏覽量

28112 -

共模電壓

+關注

關注

2文章

108瀏覽量

12990

發布評論請先 登錄

什么是差分信號?差分信號的優勢和注意事項

FPGA中差分信號的定義和使用(一)

高速LVDS(低壓差分信號)接口電路設計

使用差分信號時的注意事項

使用差分信號時的注意事項

評論