在Verilog HDL中實現鎖存器(Latch)通常涉及對硬件描述語言的基本理解,特別是關于信號如何根據控制信號的變化而保持或更新其值。鎖存器與觸發器(Flip-Flop)的主要區別在于,鎖存器是由電平觸發的,而觸發器則是由邊沿觸發的。這意味著鎖存器在控制信號(通常是使能信號)為高或低電平時保持數據狀態,而觸發器在時鐘信號的上升沿或下降沿更新其狀態。

不過,要注意的是,在現代數字設計中,鎖存器通常被觸發器所取代,因為觸發器提供了更好的時序控制和穩定性。然而,在某些特定應用中,如某些類型的存儲元件或需要電平觸發的場景中,鎖存器仍然有其用途。

下面,我將首先提供一個簡單的D鎖存器的Verilog實現,然后詳細解釋代碼的各個部分,并擴展到更復雜的場景和應用。

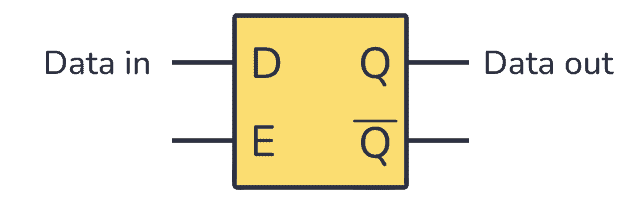

D鎖存器的基本實現

D鎖存器是最簡單的鎖存器類型之一,它有一個數據輸入(D),一個使能輸入(E),和一個數據輸出(Q)。當使能信號為高時,輸出跟隨輸入;當使能信號為低時,輸出保持其最后的狀態。

module D_latch(

input D, // 數據輸入

input E, // 使能輸入

output reg Q // 數據輸出

);

// D鎖存器的行為描述

always @(D or E) begin

if (E)

Q <= D; // 如果E為高,則Q更新為D的值

// 注意:這里沒有else語句,因為當E為低時,Q的值保持不變

end

endmodule

代碼詳細解釋

- 模塊定義 :

module D_latch(...)定義了一個名為D_latch的模塊,它有三個端口:D(數據輸入)、E(使能輸入)、Q(數據輸出)。輸出被聲明為reg類型,因為我們需要在這個模塊內部對其進行賦值。 - always塊 :

always @(D or E)指定了一個始終塊,它會在D或E的值發生變化時執行。這是實現電平觸發邏輯的關鍵。 - 條件語句 :

if (E)檢查使能信號E是否為高。如果是,則執行Q <= D;,將Q的值更新為D的值。這里使用了非阻塞賦值(<=),因為在這個上下文中,我們并不關心賦值操作的立即結果,而是希望所有的賦值操作都在同一個仿真時間點完成,以模擬硬件的并行行為。 - 保持狀態 :當E為低時,沒有執行任何操作來顯式地更新Q的值。在Verilog中,如果reg類型的變量在某個always塊中沒有被賦予新值,它將保持其上一個值。這正是鎖存器保持狀態的功能所在。

擴展應用

1. 邊緣觸發的近似實現

雖然鎖存器是電平觸發的,但我們可以通過一些技巧來近似實現邊緣觸發的行為。例如,我們可以使用一個額外的信號來檢測使能信號的上升沿,并據此更新輸出。然而,這種實現方式并不是真正的邊緣觸發,因為它仍然依賴于電平檢測。

2. 鎖存器陣列

在需要存儲多個數據位的場景中,可以使用鎖存器陣列。這可以通過將多個D鎖存器實例化為一個模塊,并共享相同的使能信號來實現。每個鎖存器處理一個數據位。

3. 異步控制邏輯

鎖存器在異步控制邏輯中特別有用,因為它們允許在不確定的時間點捕獲數據。例如,在需要處理來自不同時鐘域的信號時,可以使用鎖存器來同步這些信號,盡管這通常不是最佳實踐(因為可能導致亞穩態問題)。

4. 寄存器文件

雖然寄存器文件通常由觸發器組成,但在某些特定應用中,鎖存器也可以用于構建簡單的寄存器文件。這可以通過將多個鎖存器組織成一個數組,并使用解碼器來選擇要訪問的鎖存器來實現。

結論

Verilog HDL中的鎖存器實現相對簡單直接,但它們在數字電路設計中的使用需要謹慎。由于它們對電平變化敏感,因此可能會引入時序問題和亞穩態風險。然而,在需要電平觸發邏輯或特定存儲行為的場景中,鎖存器仍然是一個有用的工具。

-

Verilog

+關注

關注

29文章

1366瀏覽量

112057 -

鎖存器

+關注

關注

8文章

923瀏覽量

42253 -

觸發器

+關注

關注

14文章

2034瀏覽量

62009

發布評論請先 登錄

D鎖存器的基本實現

D鎖存器的基本實現

評論