本節內容主要講述CortexR52內核Cache的具體操作包括使緩存無效(invalidate)操作,清除(clean)緩存。有的時候客戶可能需要對cache做一些清理,比如invalidate,clean等操作。雖然目前在cortex R52內核很少需要操作cache,但是本節依然給一些操作指導和實踐,以備以后不時之須。

Cache Line緩存行的概念

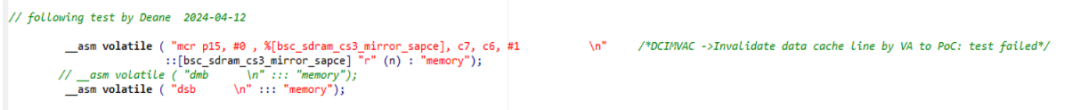

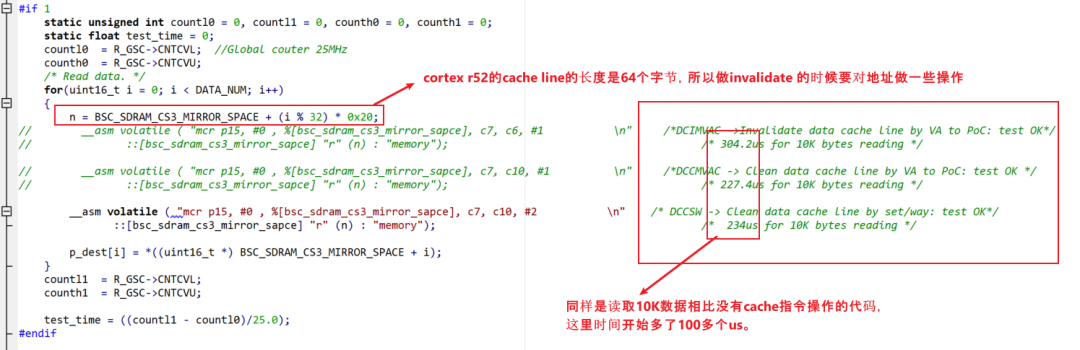

操作cache相關指令需要通過匯編代碼來操作,也都是以緩存行(Cache Line)為單位來進行操作。CortexR52緩存行的長度是64字節,比如下面的invalidate指令:

點擊可查看大圖

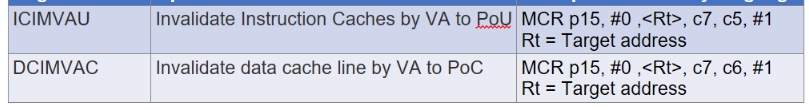

指令的解釋如下:

點擊可查看大圖

1__asm volatile

這表示這是一段內聯匯編代碼,并且使用volatile關鍵字告訴編譯器不要對這段代碼做優化。

2"mcr p15, #0, %[bsc_sdram_cs3_mirror_space], c7, c6, #1 "

這是ARM處理器的指令。mcr是一個協處理器數據操作指令,用于向協處理器(如CP15)中的特定寄存器寫入數據。在這里,它將數據寫入到CP15寄存器中。p15, #0: 指定了協處理器的編號,這里表示CP15。

3%[bsc_sdram_cs3_mirror_space] "r" (n)

這里使用了內聯匯編中的替換字符串(substitution strings),%[bsc_sdram_cs3_mirror_space] 用于指定一個替換占位符,它將在后面的 :: 部分中提供實際的值。"r" (n) 則表示使用寄存器(register)約束,這意味著n是一個變量。通常情況下,使用 "i" 約束表示將一個立即數直接嵌入到匯編指令中,而不是從變量中加載。但在你的代碼中,你想要從一個變量中加載一個值傳遞給匯編指令。因此,你應該使用 "r" 約束來表示將一個寄存器中的值傳遞給匯編指令,而不是使用 "i"。

4:: 和 : "memory"

這兩個部分是內聯匯編的修飾符。:: 表示沒有輸出寄存器,"memory" 則表示該內聯匯編代碼可能會對內存進行讀寫操作,因此編譯器需要考慮到內存屏障(memory barrier)的影響。

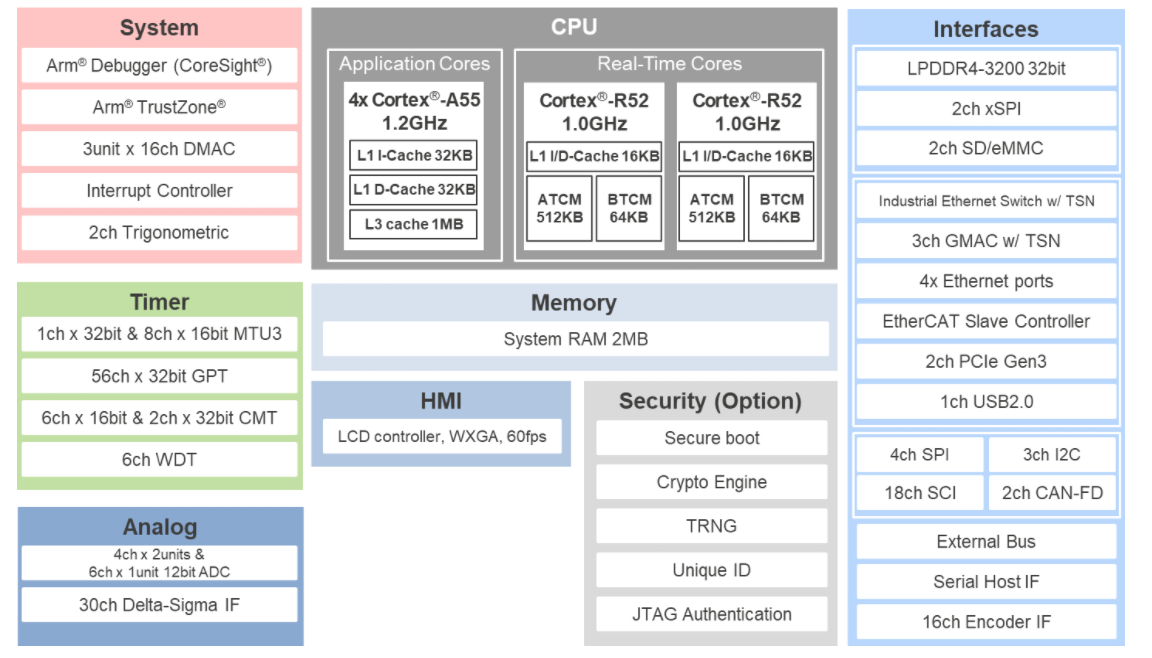

以RZT2M為例對cache作一些操作

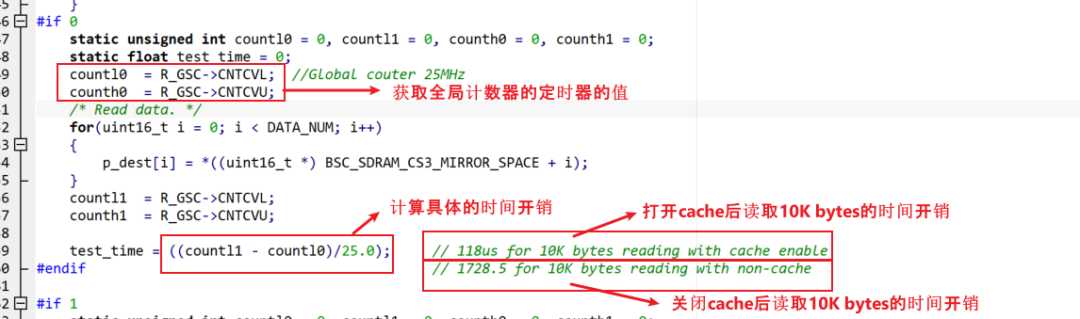

1以rzt2m讀取SDRAM為例,做一個打開和關閉cache的性能比較

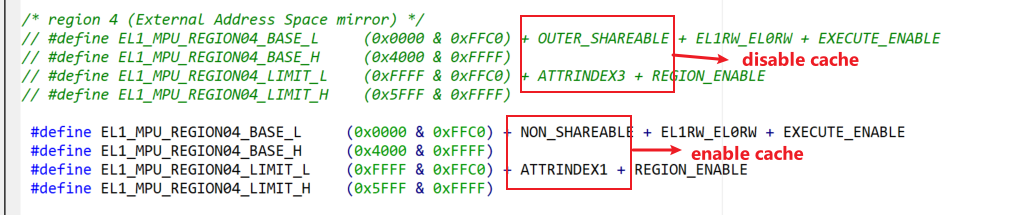

SDRAM在代碼中如果使用external Address sapce mirror的地址空間,那么開啟和關閉cache的配置如下圖所示:

點擊可查看大圖

點擊可查看大圖

從上圖可以看出關閉cache后讀取數據的時間是打開cache后時間開銷的十多倍。所以cache是否使能,性能差別十分顯著。

2如果同樣是讀取10K bytes的數據,加上一起對cache invalidate/clean的操作之后,時間開銷如下

點擊可查看大圖

上面的代碼每讀取sdram一次,都有對cache做操作。所以時間開銷增加了很多,但是實際情況,是否需要頻繁的操作cache需要看實際情況而定。注意每次對cache的操作都是以,cache line的長度(64字節)對cache做處理的。比如invalidate某段sdram地址對應的cache, 0x58000000-0x58000040, 那么對這段地址的invalidate操作是:

左右滑動查看完整內容

__asm volatile ( "mcr p15, #0 , %[bsc_sdram_cs3_mirror_sapce], c7, c6, #1 " /*DCIMVAC ->Invalidate data cache line by VA to PoC: test OK*/ ::[bsc_sdram_cs3_mirror_sapce] "i" (0x58000000) : "memory");

注意代碼中 "i" 與 "r" 的區別,在上文中已經有提到。

注意對cache的操作需要十分慎重,并且充分驗證的情況下進行。

-

內核

+關注

關注

3文章

1406瀏覽量

41059 -

指令

+關注

關注

1文章

614瀏覽量

36198 -

Cortex

+關注

關注

2文章

203瀏覽量

47104

原文標題:解密Cortex R52內核Cache:操作實踐、性能測試與深度解析(4)

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【RA-Eco-RA4M2開發板評測】利用GPIOPUT結合繼電器控制臺燈頻閃

滲壓計‘喝飽水’有多重要?透水板浸飽和的具體操作步驟

DeepSeek企業部署依托raksmart裸機云具體操作指南

如何從R52_0使用SD Boot啟動S32z ?

集成應用處理功能和高精度實時控制性能的高端 MPU RZ/T2H數據手冊

定位器氣密性檢測儀的具體操作流程

ADS1115在配置和轉換時的具體操作步驟,每一步的寄存器配置是怎樣的?

Arm Cortex-R82AE賦能高性能區域控制器設計

RM57L843基于ARM? Cortex?-R內核的Hercules?微控制器數據表

TMS570LC4357基于ARM Cortex?-R內核的Hercules?微控制器數據表

Cortex R52內核Cache的相關概念(1)

Cortex R52內核Cache的具體操作(2)

Cortex R52內核Cache的具體操作(2)

評論