一、D觸發器的基本概念

D觸發器(Data Flip-Flop或Delay Flip-Flop)是數字電子電路中一種重要的存儲器件,主要用于存儲1位二進制數據。它具有記憶功能,能夠在特定的時鐘脈沖作用下,將輸入端的信號狀態鎖存到輸出端,并保持該狀態直到下一個時鐘脈沖的到來。D觸發器是數字邏輯電路中構成多種時序電路的基本邏輯單元,因此在數字系統和計算機中有著廣泛的應用。

二、D觸發器的工作原理

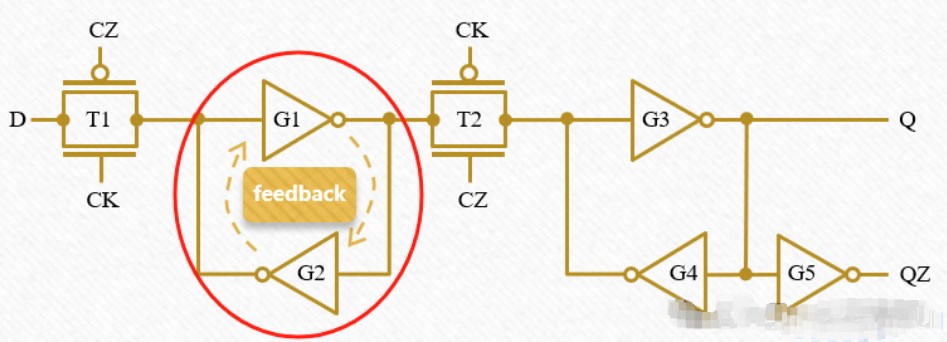

時鐘信號CK通過倒相器生成反相信號CZ。D端是D觸發器的信號輸入。Q和QZ是D觸發器的輸出端。QZ通過G5輸出Q的反相信號。為了便于文字表達,通常用CZ和QZ表示!CK和!Q(用“!”表示取反NOT,和上劃線表示一樣,讀“bá”)。

G1和G2形成回路。G1的輸出通過G2連接到G1的輸入,稱為反饋(feed back)。同理,G3和G4也形成反饋回路。

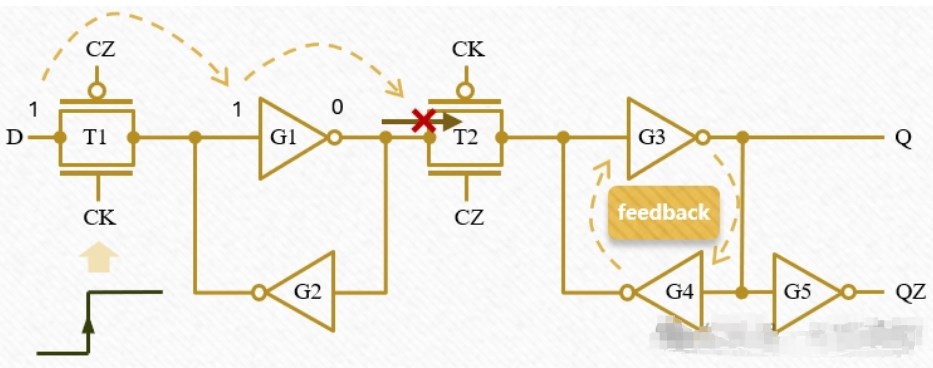

當CK為高電平時,T1導通,輸入端D的信號通過G1和G2的反饋回路,使得G1的輸出始終保持為D的反相電平。此時,T2截止,呈現高阻狀態,G3不能接受G1的輸出,而是通過G3和G4的反饋回路,保持其原有的信號。

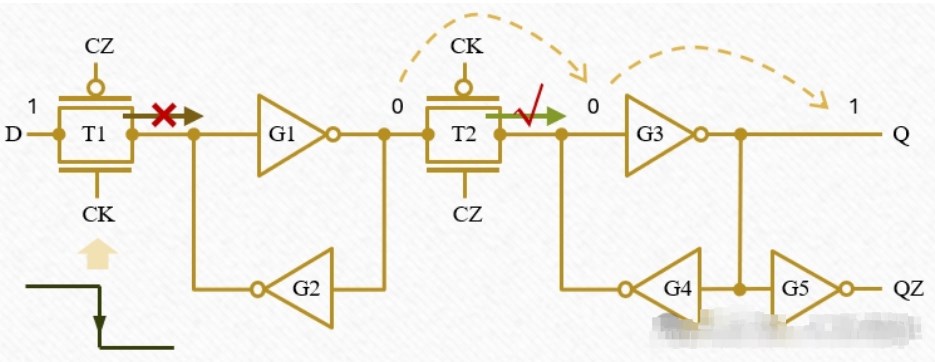

當CK為低電平時,T1截止,呈現高阻狀態,G1不能接受D的輸入信號,而是保持T1導通時輸入的信號。而T2導通,G3接受G1的輸出信號,將改變其輸出Q的信號。

等到下一個時鐘信號CK再為高電平時下一個D信號才能進入這個D觸發器。

CK為高電平期間,稱為保持狀態。CK為低電平期間,稱為傳輸狀態。

這種由時鐘控制的電路,稱為時序電路。這是由于D觸發器與時鐘信號控制來決定其信號的狀態,而且能夠保持一定的電平,所以稱為具有記憶功能的電路。

其中,由T1、G1、G2構成的電路,以及由T2、G3、G4構成的電路都稱為鎖存器(latch)。

這種D觸發器的類型稱為主從觸發器(master-slave)。前一個鎖存器為主觸發器,后一個鎖存器為從觸發器。

三、D觸發器的電路結構

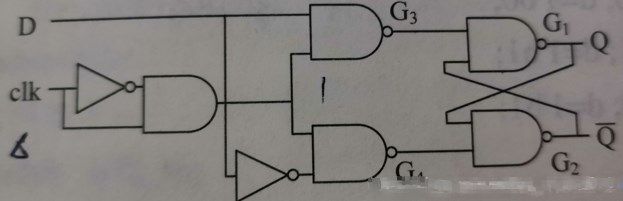

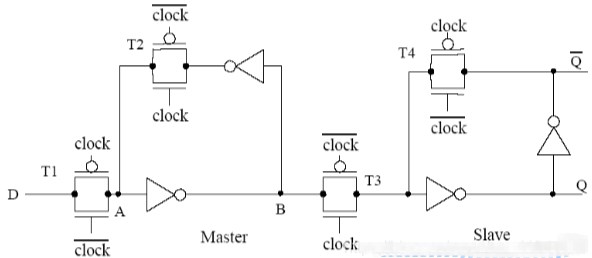

觸發器主要有兩種電路結構,CMOS邏輯門如圖,和傳輸門構成的D觸發器如圖所示。

圖為CMOS邏輯門構成D觸發器

圖為傳輸門構成D觸發器

兩種電路結構實現的D觸發器功能一模一樣,我們以圖2-1為例來分析觸發工作原理。如圖2-1所示:在clk上升沿到來之前,D輸入端無論輸入任何值觸發器狀態不會改變,次態等于現態。當時鐘上升沿到來時,與時鐘信號連接的非門產生的短暫延遲,使得觸發器狀態置成D輸入端的狀態。

四、D觸發器的脈沖特性

D觸發器的脈沖特性主要體現在其觸發方式上,主要分為電平觸發和邊沿觸發兩種。

1. 電平觸發

電平觸發D觸發器在時鐘脈沖(CP)等于某一特定電平(如高電平)時即可觸發。這種觸發方式相對簡單,但在實際應用中容易受到干擾,因為只要CP保持在該電平,輸入端D的狀態變化就可能影響觸發器的輸出。因此,電平觸發D觸發器的抗干擾能力較弱。

2. 邊沿觸發

邊沿觸發D觸發器在時鐘脈沖的上升沿或下降沿觸發。這種觸發方式具有更強的抗干擾能力,因為輸入信號D的狀態變化只有在時鐘脈沖的邊沿到來時才會被觸發器捕獲并鎖存。邊沿D觸發器也被稱為維持-阻塞邊沿D觸發器,因為它在CP=1期間具有維持阻塞作用,即D端的數據狀態變化不會影響觸發器的輸出狀態。

邊沿觸發D觸發器的脈沖特性可以進一步細化為以下幾個方面:

建立時間(t_set):指輸入信號D在時鐘脈沖邊沿到來之前必須保持穩定的最小時間。這是為了確保D端的數據在觸發器翻轉前已經穩定地傳輸到內部邏輯電路中。

保持時間(t_hold):指時鐘脈沖邊沿到來之后,輸入信號D必須繼續保持穩定的最小時間。這是為了防止在觸發器翻轉過程中,D端的數據發生變化而導致輸出狀態錯誤。

傳輸延遲(t_pd):指從時鐘脈沖邊沿到來到觸發器輸出狀態穩定所需的時間。這是觸發器內部邏輯電路處理輸入信號并產生輸出響應的時間延遲。

五、D觸發器的應用

D觸發器在數字系統和計算機中有著廣泛的應用,主要包括以下幾個方面:

1. 時序控制

D觸發器可以用于時序電路中,通過控制時鐘脈沖的序列來控制電路的狀態變化。例如,在計數器電路中,D觸發器可以存儲和傳遞計數信息,實現計數的功能。

2. 寄存器

D觸發器可以作為寄存器的基本單元,用于存儲和傳輸數據。在數字系統中,寄存器是存儲數據的重要部件,D觸發器通過其記憶功能,能夠穩定地保存數據并在需要時將其輸出。

3. 波形發生器

通過特定的連接方式和時鐘脈沖序列,D觸發器可以生成各種波形信號。例如,利用D觸發器的翻轉功能,可以產生方波、鋸齒波等周期性波形信號。

4. 同步電路

在同步電路中,D觸發器用于同步不同部分的時鐘信號,確保整個電路按照統一的時鐘節拍工作。這有助于減少電路中的時序錯誤和信號沖突。

D觸發器作為數字電子電路中的重要存儲器件,具有記憶功能和多種觸發方式。其結構主要由存儲單元和控制單元組成,通過控制時鐘脈沖的序列和D端的輸入信號來實現對輸出狀態的控制。D觸發器的功能包括置0、置1、保持和翻轉等,這些功能使得D觸發器在時序控制、計數器、寄存器和波形發生器等領域有著廣泛的應用。隨著數字技術的不斷發展,D觸發器的性能和功能也將不斷提升和完善。

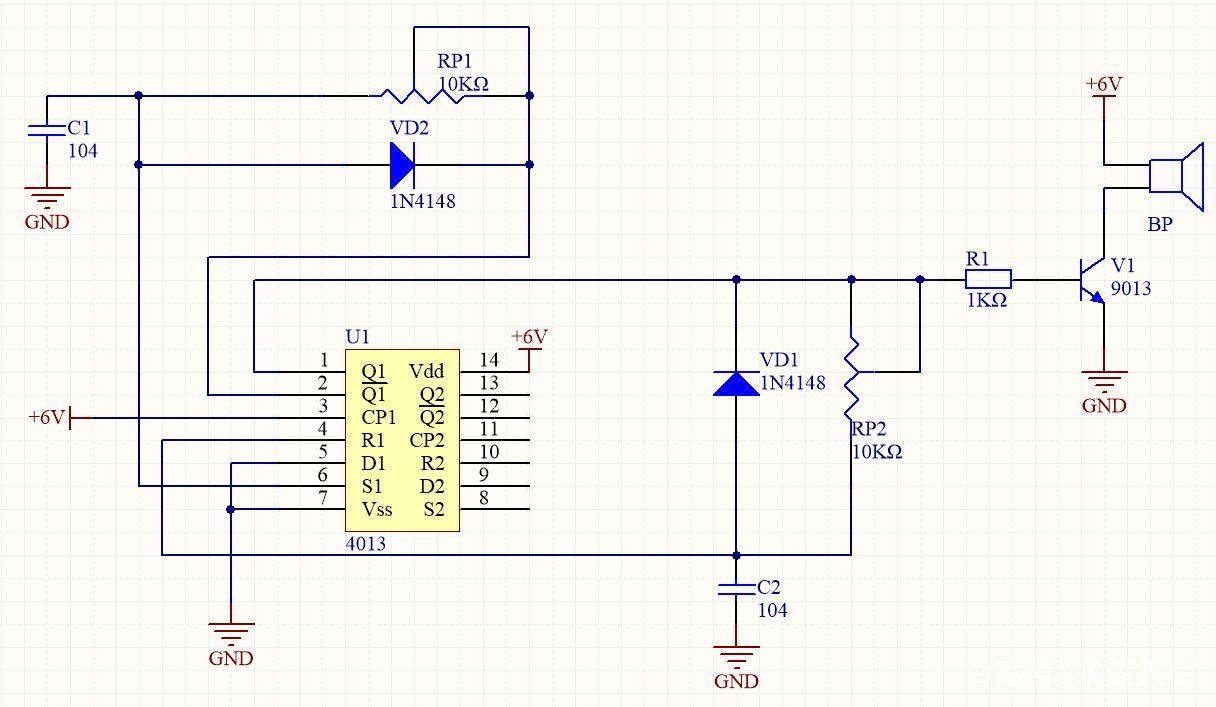

六、基于D觸發器的音頻信號發生器電路圖

這是一個用D觸發器組成音頻信號發生器,電路原理圖如圖所示。

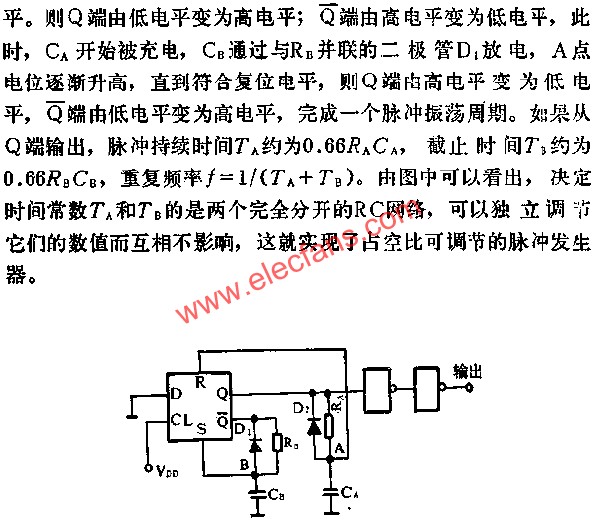

在電源接通后的瞬間,Q1端(第1腳)輸出為高電平,該高電平通過RP2向C2充電,當C2端電壓上升到復位電平時,Q1 端變為低電平,C2通過二極管VD2向Q1端放電。此時!Q1(Q1的取反)輸出端(第2腳)變為高電平,該高電平通過RP1向C1充電。當C1端電壓上升到置位電平時,觸發器翻轉,Q1變為高電平,!Q1變為低電平,Q1端的高電平向C2充電,C1通過二極管VD1向變為低電平的!Q1端放電,如此不斷循環,在Q1和!Q1端交替出現高、低電平,形成振蕩。因此該電路是一個無穩態的振蕩器。QI 端的振蕩信號通過電阻R1加到三極管V1的基極,經過V1放大后推動揚聲器BP發出響亮的音頻聲。

-

邏輯電路

+關注

關注

13文章

502瀏覽量

43164 -

計算機

+關注

關注

19文章

7626瀏覽量

90135 -

D觸發器

+關注

關注

3文章

165瀏覽量

48501 -

音頻信號發生器

+關注

關注

1文章

5瀏覽量

3298

發布評論請先 登錄

基于D觸發器的音頻信號發生器電路圖 D觸發器的工作原理和脈沖特性

基于D觸發器的音頻信號發生器電路圖 D觸發器的工作原理和脈沖特性

評論