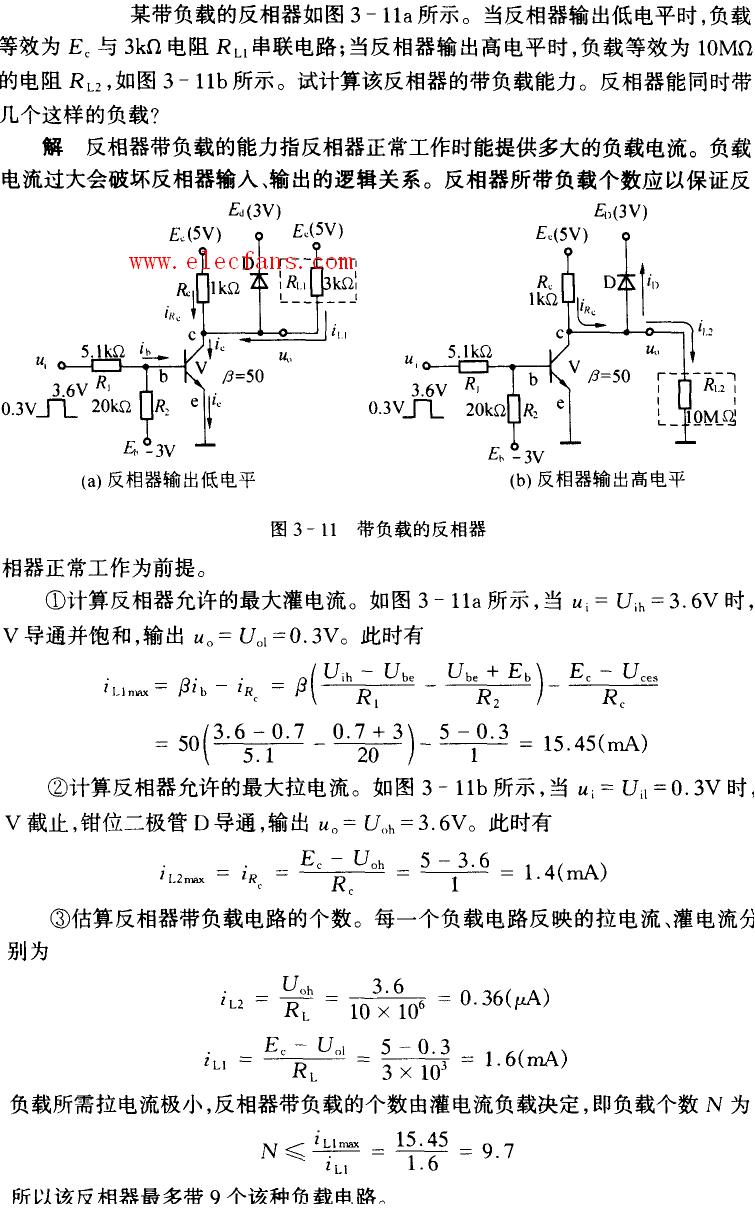

反相器和非門是數字邏輯電路中的基本組件,它們在數字電路設計中扮演著重要的角色。盡管它們在功能上有一定的相似性,但它們之間還是存在一些關鍵的區別。

- 定義

反相器(Inverter)是一種只有一個輸入端和一個輸出端的數字邏輯門,其輸出狀態與輸入狀態相反。當輸入為高電平時,輸出為低電平;當輸入為低電平時,輸出為高電平。反相器的邏輯功能可以用邏輯非(NOT)運算表示。

非門(NAND gate)是一種具有兩個輸入端和一個輸出端的數字邏輯門,其輸出狀態為兩個輸入端的邏輯與(AND)運算的反(NOT)。當兩個輸入端都為高電平時,輸出為低電平;當至少有一個輸入端為低電平時,輸出為高電平。非門的邏輯功能可以用邏輯與非(NAND)運算表示。

反相器的工作原理相對簡單。當輸入端接收到高電平時,反相器內部的晶體管或邏輯門會將電流導向地線,使輸出端呈現低電平狀態;反之,當輸入端接收到低電平時,反相器內部的晶體管或邏輯門會將電流導向電源,使輸出端呈現高電平狀態。

非門的工作原理稍微復雜一些。非門內部通常包含兩個晶體管或邏輯門,它們通過與門(AND gate)和非門(NOT gate)的組合實現邏輯與非運算。當兩個輸入端都為高電平時,與門的輸出為高電平,經過非門后,輸出端呈現低電平狀態;當至少有一個輸入端為低電平時,與門的輸出為低電平,經過非門后,輸出端呈現高電平狀態。

- 電路結構

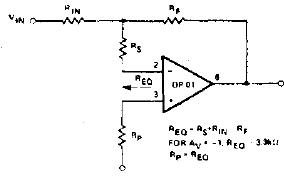

反相器的電路結構相對簡單,通常由一個晶體管或邏輯門組成。在CMOS技術中,反相器通常由一個N型晶體管和一個P型晶體管組成,它們通過互補對稱的方式實現反相功能。

非門的電路結構相對復雜,通常由兩個晶體管或邏輯門組成。在CMOS技術中,非門通常由兩個N型晶體管和兩個P型晶體管組成,它們通過與門和非門的組合實現邏輯與非功能。

- 邏輯功能

反相器的邏輯功能是邏輯非(NOT)運算,其真值表如下:

| 輸入A | 輸出Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

非門的邏輯功能是邏輯與非(NAND)運算,其真值表如下:

| 輸入A | 輸入B | 輸出Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

- 應用場景

反相器和非門在數字電路設計中都有廣泛的應用場景。

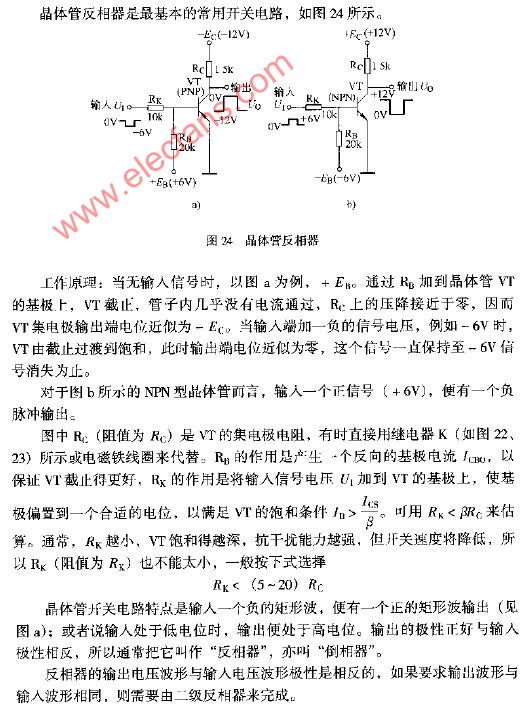

反相器主要用于實現信號的反向、信號的緩沖、信號的隔離等。在實際電路設計中,反相器可以用于消除信號的延遲、提高信號的穩定性、減少信號的干擾等。

非門則主要用于實現復雜的邏輯運算,如與非、或非、異或等。在實際電路設計中,非門可以用于實現各種復雜的邏輯功能,如數據選擇、數據編碼、數據解碼等。

- 優缺點

反相器的優點是電路結構簡單、功耗低、速度快。但是,反相器的缺點是功能單一,只能實現邏輯非運算。

非門的優點是功能強大,可以組合成各種復雜的邏輯功能。但是,非門的缺點是電路結構復雜、功耗較高、速度較慢。

反相器與非門的差異:

- 功能與邏輯表達式

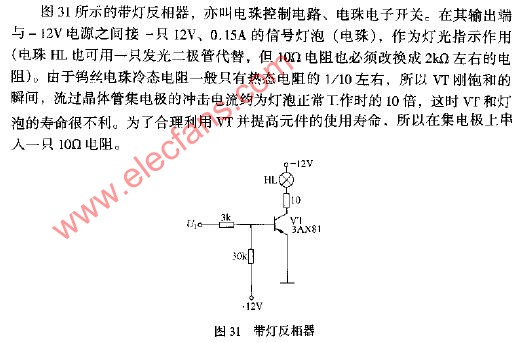

- 功能:反相器和非門在功能上都實現了信號的取反,即輸入和輸出之間具有反相關系。但反相器主要應用于模擬電路,而非門則更多地應用于數字電路和邏輯運算。

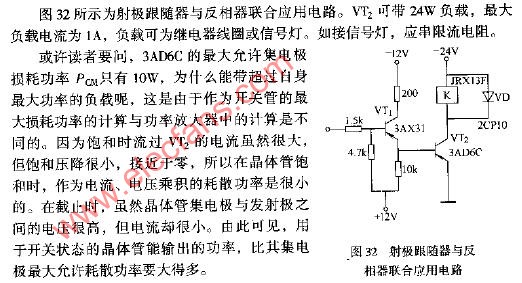

- 邏輯表達式:反相器和非門的邏輯表達式均為Y = ?A(其中A為輸入信號,Y為輸出信號,?表示邏輯非操作)。這表明兩者在邏輯功能上是等效的。

- 構成方式與實現

- 構成方式:反相器通常通過晶體管等元件構成的電路來實現,其實現方式較為單一。而非門則可以用多種電子元件實現,包括晶體管、集成電路等,具有更靈活的實現方式。

- 實現技術:在CMOS技術中,反相器是基本的構建模塊,而非門則是基于CMOS或其他邏輯技術(如TTL)實現的。這反映了兩者在實現技術上的差異。

- 符號表示

- 反相器在電路圖中通常用一個圓圈或帶小圓圈的三角形表示,強調其相位反轉的功能。

- 非門在電路圖中則通常用一個三角形表示,強調其邏輯非的功能。這種符號表示的差異有助于在電路圖中快速識別兩者的功能。

- 應用領域

反相器是所有數字設計的核心。靜態CMOS反相器具有以下重要特性:

①輸出高電平為V DD ,輸出低電平為GND;

②屬于無比邏輯,功能不受晶體管相對尺寸影響;

③具有低輸出阻抗,輸入電阻極高;

④理論上具有無窮大扇出,單個反相器可以驅動無窮多個門,增加扇出會增加傳播延時,動態特性會變差,但不會影響穩態特性;

⑤在穩態工作情況下,電源線和地線之間沒有直接通路,沒有電流存在,意味著理論上沒有靜態功耗。

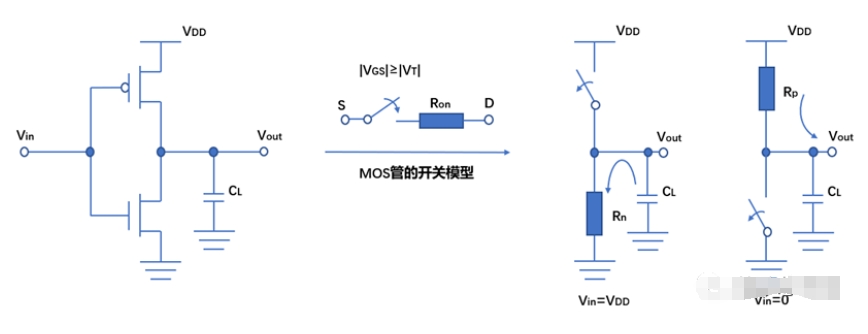

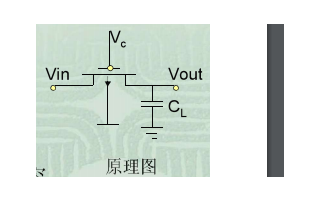

如下圖是一個靜態CMOS反相器的電路圖,由一個上拉的PMOS器件和一個下拉的NMOS器件組成。通過使用MOS管的開關模型,可以將其等效成右邊所示的反相器開關模型。當V in =VDD時,下拉NMOS器件開始工作,PMOS器件斷開,將存儲在負載電容CL上的電壓放電至0V。當V in =0V時,上拉PMOS器件開始工作,NMOS器件斷開,向負載電容CL充電至V DD 。

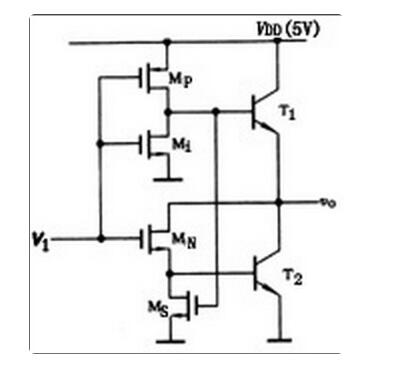

我們為什么要使用NMOS器件作為下拉器件,PMOS器件作為上拉器件呢?主要原因是PMOS器件是強1器件,而NMOS器件是強0器件。如下圖所示,使用NMOS器件放電時可以將存儲在負載電容CL上的電壓放電至0V,而使用PMOS器件只能放電至|V Tp |。同樣,使用PMOS器件充電時,可以向負載電容CL充電至V DD ,而使用NMOS器件只能充電至V DD -V Tn 。

CMOS反相器的總功耗分為動態功耗和靜態功耗,我們首先看一下動態功耗。動態功耗主要有兩種,由充放電電容引起的動態功耗和由直接通路電流引起的動態功耗。充放電電容引起的動態功耗大致過程是在充電過程中,一半能量被PMOS管消耗,一半能量存儲在CL負載電容中;放電過程中,存儲在電容上的能量被NMOS管消耗。

f 0→1 :稱為開關活動性,是消耗能量的翻轉頻率,也就是每秒通斷次數

另一種動態功耗是由于輸入波形存在上升和下降時間,導致在開關過程中從VDD到GND之間在短期內出現一條直流通路,造成短路電流。

接下來,我們分析一下峰值電流

? 當負載很大,輸出的下降時間明顯比輸入上升時間大,輸入在輸出改變之前就已經通過了過渡區,PMOS的源漏電壓近似為0,P管就基本關斷了,所以Ipeak很小

? 反之,當負載很小,輸出下降時間明顯小于輸入上升時間,PMOS的VDS大部分時間等于V DD ,所以導致了最大的短路電流

我們得到的結論是:使輸出的下降時間大于輸入上升時間可以減小短路功耗,但輸出的上升/下降時間太大會降低電路速度,并在扇出門中引起短路電流。換句話說,當負載電容比較小時,直接通路電流引起的動態功耗將占主導,而當負載電容較大時,充放電負載電容引起的動態功耗將占主導。

靜態功耗一般由源(或漏)與襯底之間的反偏二極管漏電和亞閾值漏電構成:

①源(或漏)與襯底之間的反偏二極管漏電

通常情況下非常小,該部分漏電是由熱產生的載流子引起的,該數值隨結溫而增加,并且呈指數關系。

②亞閾值漏電

VGS接近閾值電壓時會有源漏電流,在深亞微米工藝下,電源電壓降低導致這一電流越發顯著。

靜態功耗計算公式為:

I stat :指在沒有開關活動存在時在電源兩條軌線之間流動的電流。

CMOS反相器的總功耗為:

應當指出的是在典型的CMOS電路中由充放電電容引起的動態功耗占主導地位,直接通路電流引起的功耗可以通過設計控制在限定范圍內,而漏電造成的靜態功耗在未來的工藝制程下會占據更大比重。

反相器和非門在數字邏輯電路中都有重要的作用。它們在定義、工作原理、電路結構、邏輯功能、應用場景等方面都存在一定的區別。在實際電路設計中,需要根據具體的應用需求和性能要求,選擇合適的邏輯門。

-

反相器

+關注

關注

6文章

315瀏覽量

44063 -

數字電路

+關注

關注

193文章

1637瀏覽量

81597 -

非門

+關注

關注

1文章

32瀏覽量

34268 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

16045

發布評論請先 登錄

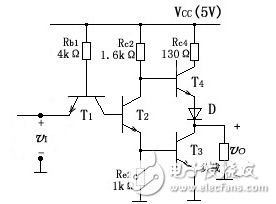

TTL反相器的基本電路圖

反相器和非門有什么區別

TTL反相器的基本電路(六款TTL反相器的基本電路設計原理圖詳解)

cmos反相器設計電路圖

MOS反相器和CMOS反相器的詳細資料說明

反相器和非門的區別 反相器電路圖介紹

反相器和非門的區別 反相器電路圖介紹

評論