CSI總線介紹與優勢

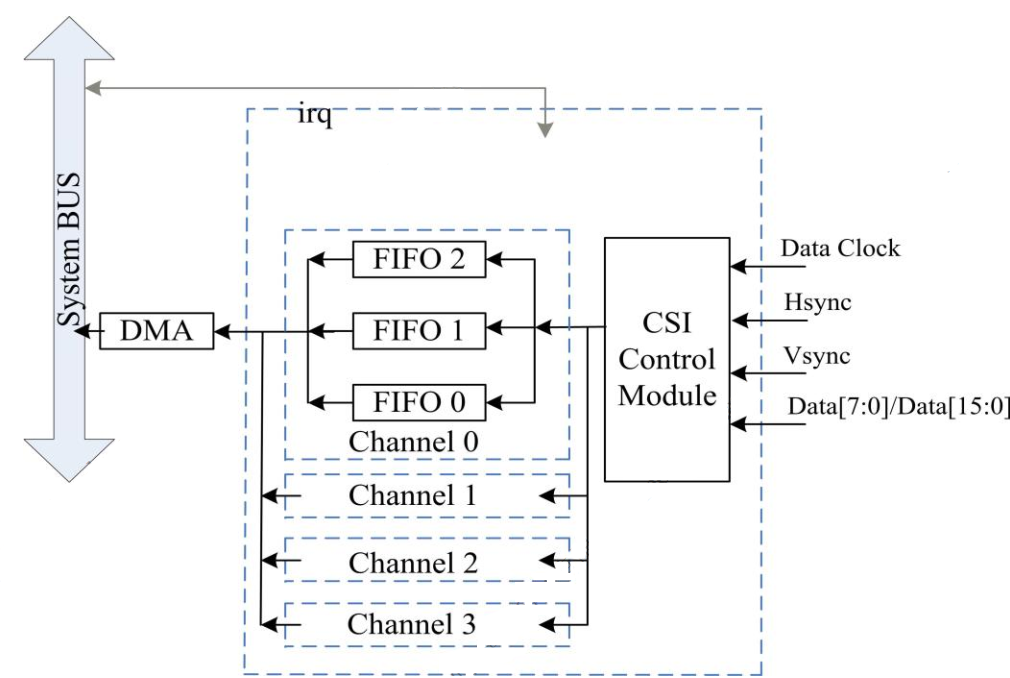

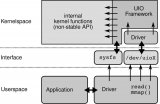

CSI(CMOS sensor parallel interfaces)總線是一種用于連接圖像傳感器和處理器的并行通信接口,應用于工業自動化、能源電力、智慧醫療等領域,CSI總線接口示意圖如下所示(以全志科技T3處理器的CSI0為例)。

圖1

高帶寬:CSI總線支持高速數據傳輸,可以滿足多通道高速AD數據的傳輸需求。

開發難度低:CSI總線采用并行數據和控制信號分離方式,時序簡單,FPGA端接口開發難度低。

低成本:CSI總線采用并行傳輸方式,FPGA端使用資源少,對FPGA器件資源要求低。

國產ARM+FPGA架構介紹與優勢

近年來,隨著中國新基建、中國制造2025規劃的持續推進,單ARM處理器越來越難勝任工業現場的功能要求,特別是如今能源電力、工業控制、智慧醫療等行業,往往更需要ARM + FPGA架構的處理器平臺來實現例如多路/高速AD采集、多路網口、多路串口、多路/高速并行DI/DO、高速數據并行處理等特定功能,因此ARM + FPGA架構處理器平臺愈發受市場歡迎。

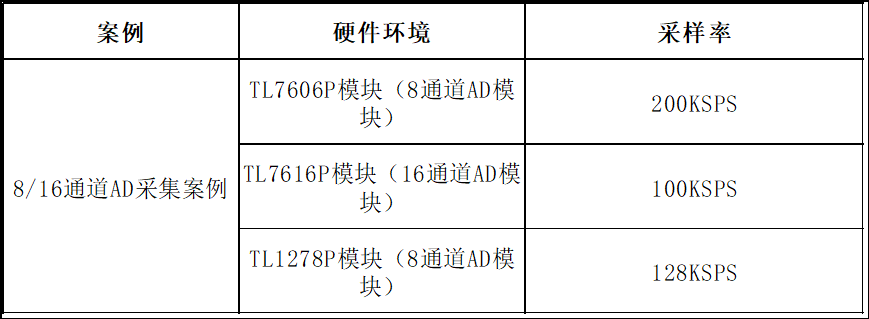

圖2

創龍科技SOM-TLT3F是一款基于全志科技T3四核ARM Cortex-A7處理器 + 紫光同創Logos PGL25G/PGL50G FPGA設計的異構多核全國產工業核心板,ARM Cortex-A7處理單元主頻高達 1.2GHz。核心板ARM、FPGA、ROM、RAM、電源、晶振、連接器等所有元器件均采用國產工業級方案,國產化率100%。

全志T3為準車規級芯片,四核ARM Cortex-A7架構,主頻高達1.2GHz,支持雙路網口、八路UART、SATA大容量存儲接口,同時支持4路顯示、GPU以及1080P H.264視頻硬件編解碼。另外,創龍科技已在T3平臺適配國產嵌入式系統翼輝SylixOS,真正實現軟硬件國產化。

紫光同創Logos PGL25G/PGL50G FPGA在工業領域應用廣泛,邏輯資源分別為27072/51360,與國外友商產品pin to pin兼容,主要用于多通道/高速AD采集或接口拓展。因其價格低、質量穩定、開發環境易用等優點,受到工業用戶的廣泛好評。

國產ARM+FPGA的CSI通信案例介紹

本章節主要介紹全志科技T3與紫光同創Logos基于CSI的ARM + FPGA通信方案,使用的硬件平臺為:創龍科技TLT3F-EVM工業評估板。

為了簡化描述,正文僅摘錄方案功能描述與測試結果,詳細開發文檔請掃描文末二維碼下載。

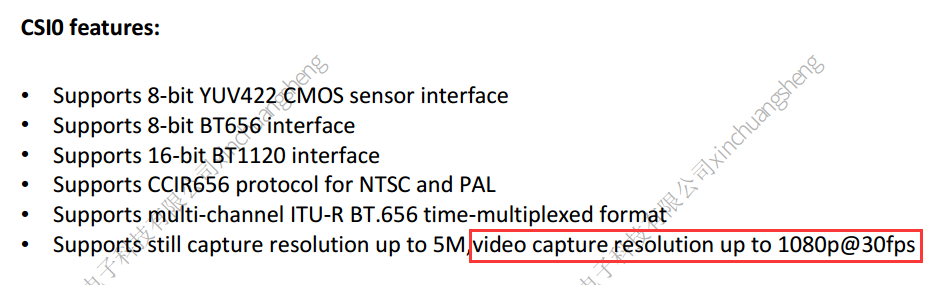

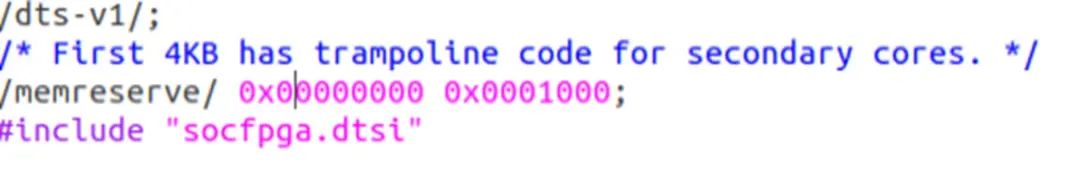

該案例實現T3(ARM Cortex-A7)與FPGA的CSI通信功能。案例使用的CSI0總線,最高支持分辨率為1080P@30fps,數據位寬為8bit,如下圖所示。CSI0理論傳輸帶寬為:1920 x 1080 x 8bit x 30fps ≈ 59MB/s。

圖4

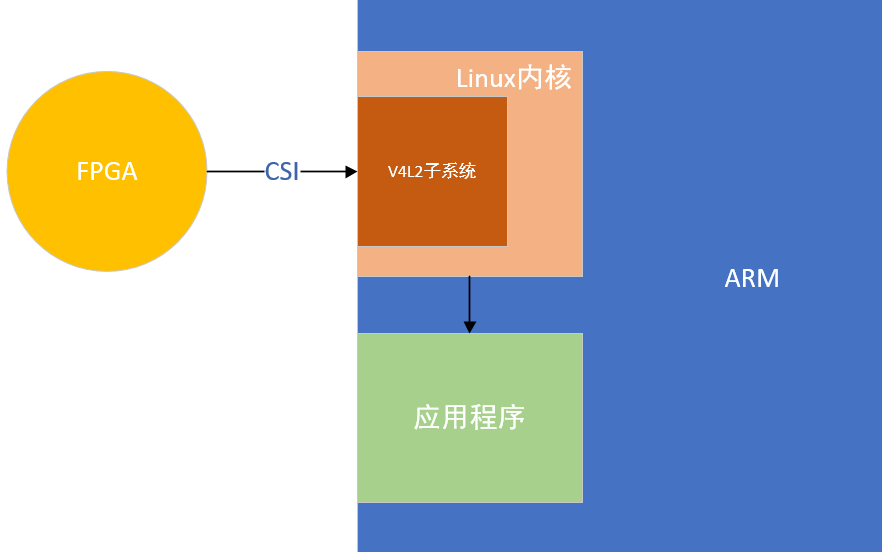

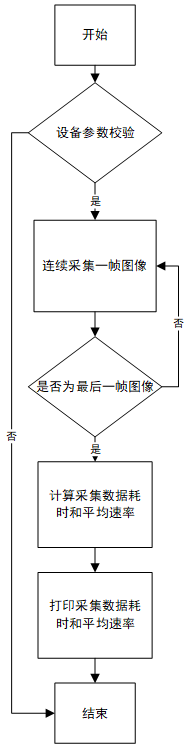

功能框圖與程序流程圖,如下圖所示。

圖5 功能框圖

圖6ARM程序流程圖

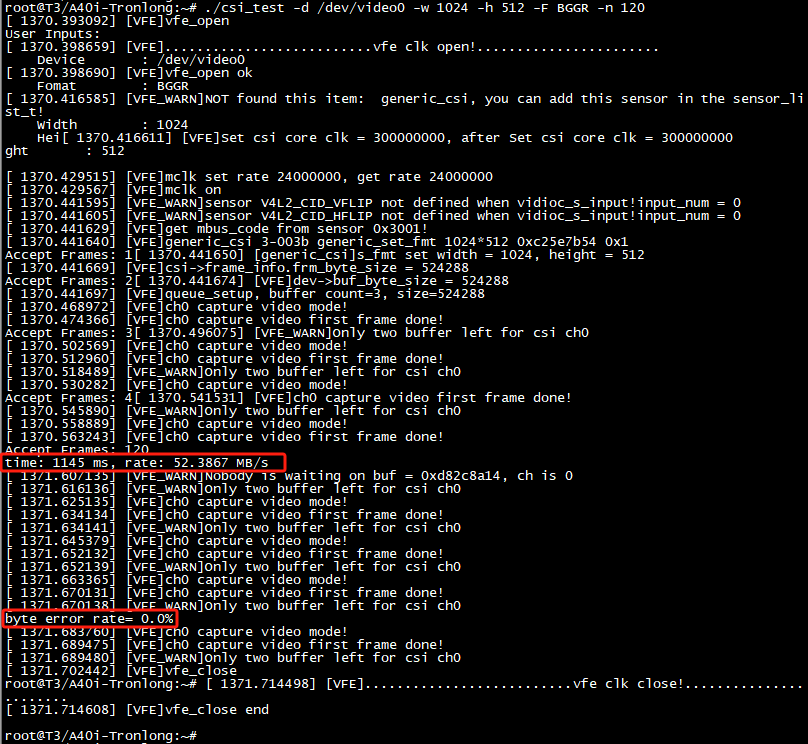

ARM端案例csi_test案例說明

ARM端案例csi_test主要功能如下:(1)基于Linux子系統V4L2;(2)通過CSI總線,采集指定幀數數據;(3)計算總耗時;(4)打印平均采集速率,并校驗最后一幀圖像的數據。

FPGA端案例parallel_csi_tx案例說明

FPGA端案例parallel_csi_tx主要功能如下:

(1)將測試數據(0x00~0xFF)寫入FIFO;

(2)從FIFO讀出數據,按行與幀的方式、1024x512的分辨率,通過CSI總線發送至ARM端。

案例測試演示

FPGA程序將CSI_PCLK設置為65MHz,測試數據寫入FIFO的時鐘FIFO_WR_CLK設置為59MHz。由于FPGA端需將數據寫入FIFO再從FIFO讀出后發送,每一行與每一幀之間的間隔時間會受FIFO寫入的速率影響,因此CSI通信的實際理論傳輸帶寬應為:(59MHz x 8bit / 8)MB/s = 59MB/s。從上圖可知,本次實測傳輸速率約為52.4MB/s,誤碼率為0,接近理論通信速率。

圖7

審核編輯 黃宇

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613992 -

ARM

+關注

關注

134文章

9304瀏覽量

374939 -

CSI

+關注

關注

1文章

38瀏覽量

51235

發布評論請先 登錄

RK3576 + FPGA并口通信方案,實測高達280MB/s

直面LoRa!ZLG致遠電子新一代全國產SubG無線模組有哪些亮點?

國產FPGA往事

【國產FPGA入學必備】國產FPGA權威設計指南+配套FPGA圖像視頻教程

16通道AD采集方案,基于復旦微ARM + FPGA國產SoC處理器平臺

實測52.4MB/s!全國產ARM+FPGA的CSI通信案例分享!

實測52.4MB/s!全國產ARM+FPGA的CSI通信案例分享!

評論