一、產(chǎn)品失效案例分析

>> 1、失效現(xiàn)象:

經(jīng)過電參數(shù)測試合格的產(chǎn)品2N**經(jīng)過客戶SMT(無鉛工藝260±5℃)生產(chǎn)線貼裝后,發(fā)現(xiàn)大量產(chǎn)品電參數(shù)失效,出現(xiàn)的現(xiàn)象是D、S間漏電,產(chǎn)品短路,失效比例超過50%。

>> 2、分析思路:

該產(chǎn)品芯片面積較大,且采用TO-252(D-PAK)表面貼裝封裝形式,產(chǎn)品組裝時采用無鉛工藝260±5℃,對產(chǎn)品的耐濕等級及氣密性要求較高,封裝時會碰到大芯片應(yīng)力匹配等一系列問題。因此根據(jù)失效現(xiàn)象重點對產(chǎn)品離層進行調(diào)查研究。

>> 3、分析方法:

模擬SMT生產(chǎn)條件對同封裝批次產(chǎn)品進行分析,采用超聲掃描儀(C-SAM)對產(chǎn)品進行離層掃描。

>> 4、分析過程:

(略)

>> 5、分析結(jié)論:

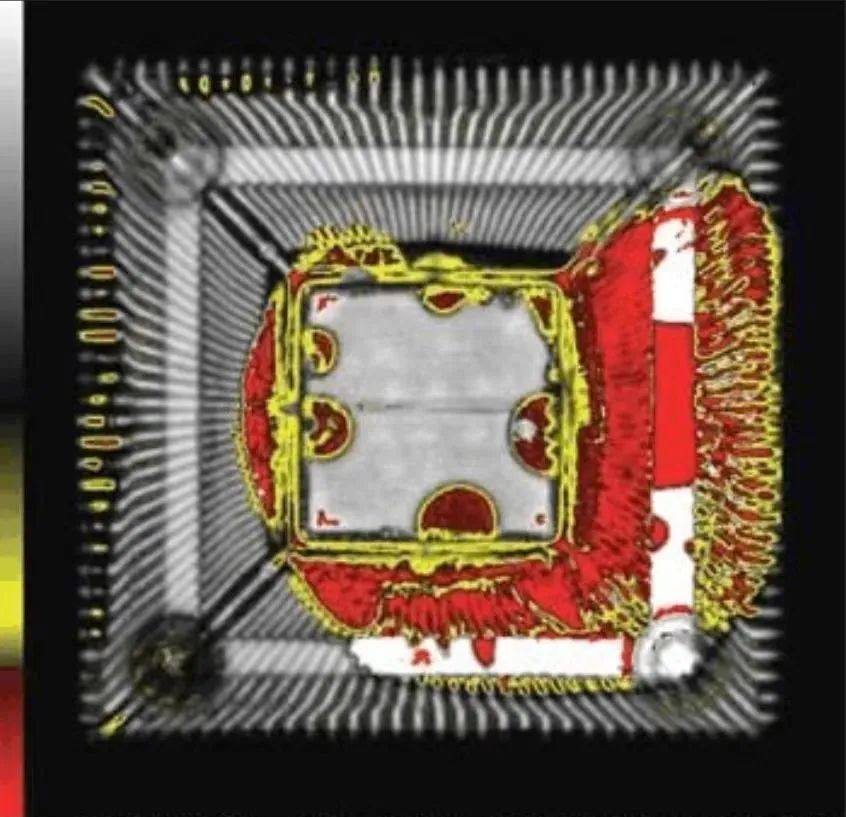

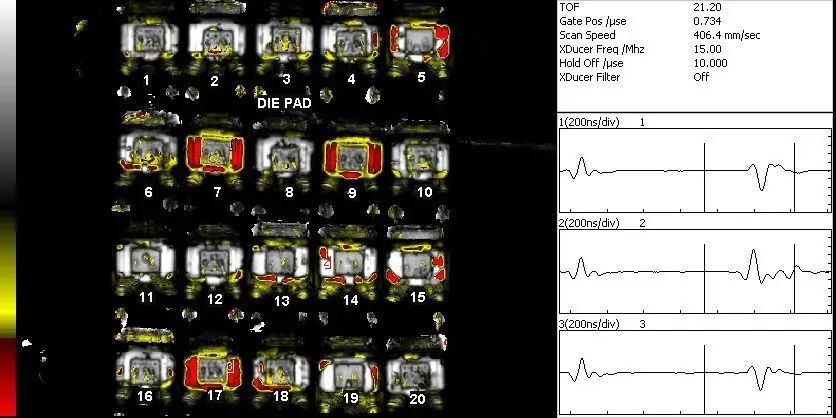

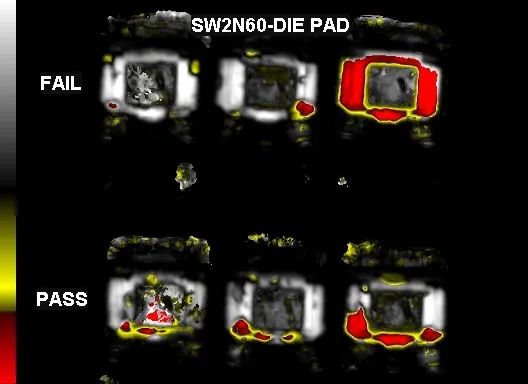

通過對經(jīng)過SMT工藝試驗的產(chǎn)品抽樣進行超聲掃描,發(fā)現(xiàn)產(chǎn)品載片區(qū)(PAD)與模塑料之間存在較為嚴重的離層現(xiàn)象,(詳見圖片1)

圖1:紅色區(qū)域為離層現(xiàn)象

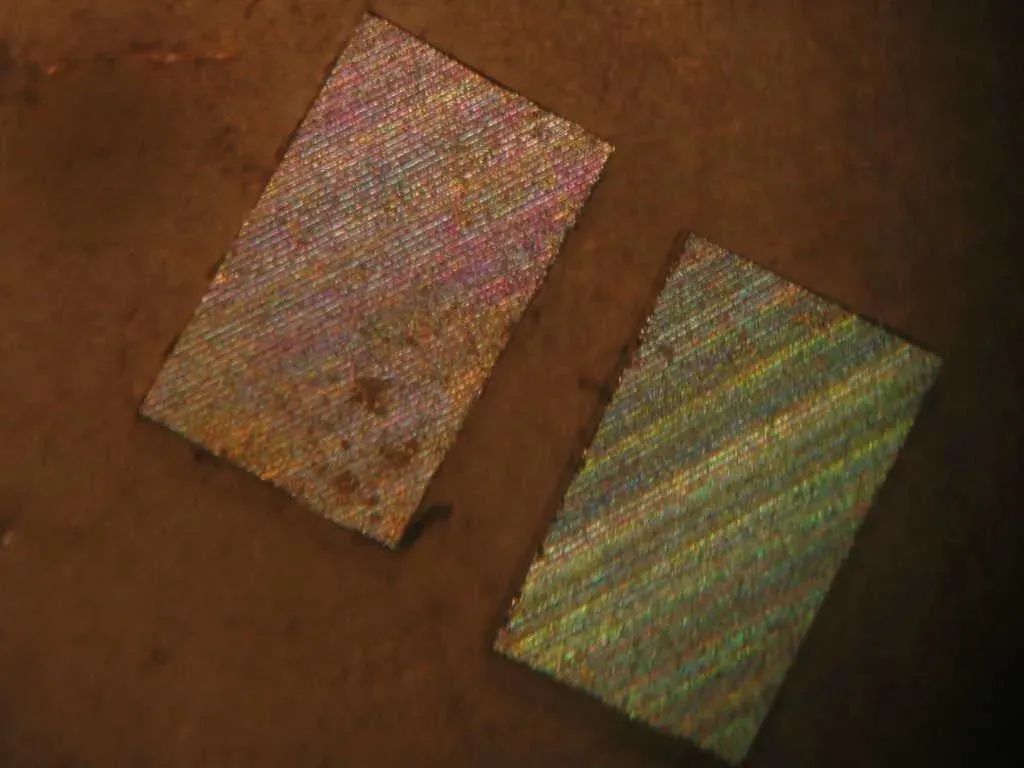

經(jīng)過對失效產(chǎn)品進行解剖,發(fā)現(xiàn)失效芯片內(nèi)部已對裂,詳見圖2、圖3:

圖2:紅圈區(qū)域為裂紋

圖3:芯片取下后呈斷裂狀

解剖結(jié)果與電參數(shù)失效項目完全吻合,表明產(chǎn)品經(jīng)過表面貼裝,在高溫的影響下,芯片破裂導(dǎo)致電參數(shù)失效。這是一個非常典型的因封裝未解決應(yīng)力問題而引起芯片破裂最終導(dǎo)致產(chǎn)品失效的案例。

二、 芯片碎裂概述:

芯片碎裂是硅器件的一種失效模式,約占早期失效總數(shù)的1%,而對于薄芯片的MOSFET產(chǎn)品,芯片碎裂則占其失效的較大比例。雖然,通過改進封裝設(shè)計、限制器件使用環(huán)境可以有效地防止芯片碎裂引起的器件失效,但即使在良好的設(shè)計、合格的制造工藝以及規(guī)范的使用環(huán)境下,依然存在著一定的芯片碎裂幾率。隨著器件可靠性級別和系統(tǒng)復(fù)雜程度的不斷提高,十分有必要對芯片碎裂失效機理加以進一步的研究。

三、芯片碎裂的機理

芯片碎裂是由內(nèi)外因素造成的,內(nèi)因:芯片強度存在“脆弱”之處。外因:在外加條件(受熱、通電熱耗散)作用下,應(yīng)力導(dǎo)致對芯片的剪切力。相對應(yīng)力而言,芯片的強度差異影響非常微小,因此芯片碎裂主要是由應(yīng)力造成的。

應(yīng)力產(chǎn)生的原因隨具體情況而不同:硅片前道工藝中的外延層淀積、擴散和離子注入、氧化、退火、淀積形成歐姆接觸、金屬內(nèi)連、鈍化層淀積:硅片后道工藝中的機械減薄(研磨、拋光)、化學(xué)減薄(濕法或者干法刻蝕)、背面金屬層淀積;封裝工藝中的劃片、 裝片、壓焊、塑封等都將會產(chǎn)生或影響硅片/芯片的應(yīng)力。其中,減薄、裝片、壓焊、塑封是產(chǎn)生芯片碎裂隱患的主要工序。更為嚴重的是,一般在工藝過程中觀察不到碎裂現(xiàn)象,只有產(chǎn)品經(jīng)過熱固化或者器件熱耗散時的瞬時加熱,特別對表面貼裝器件波峰焊接時的瞬間高溫的作用下,由于芯片和封裝材料熱膨脹系數(shù)存在差異或者使用中受外界應(yīng)力作用,芯片碎裂才會最終顯現(xiàn)。例如:穿過結(jié)的裂紋可能導(dǎo)致短路或者漏電,(以上案例就是一個證明)。裂紋也可能全部或者部分截斷電路。最為致命的是,裂紋引起的這些效應(yīng)只有瞬間受熱或者電流通過時才會顯現(xiàn),而標(biāo)準的電性能測試則根本無法檢測到這些失效。比較有效的檢測手段是模擬器件使用環(huán)境,運用超聲掃描儀(C-SAM)對產(chǎn)品進行離層掃描,如以上案例分析使用的方法,通過對離層的檢測預(yù)防芯片的破裂發(fā)生。

四、離層的定義:

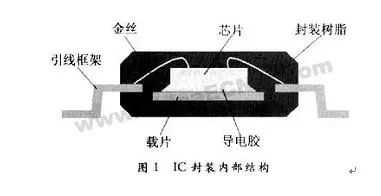

離層又叫分層,在電子封裝中,是可靠性評價的一個主要方面。分層是塑封體內(nèi)部各界面之間發(fā)生了微小的剝離或裂縫,一般在l~2 μm以上。主要發(fā)生的區(qū)域包括:封裝樹脂與芯片界面之間、封裝樹脂與(PAD)載片界面之間、封裝樹脂與引線框架界面之間、芯片與銀漿(焊料)界面之間、銀漿(焊料)與引線框架界面之間。(見下圖)

五、離層的機理

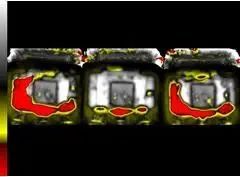

產(chǎn)生離層的工序是塑封工序,導(dǎo)致離層的因素主要為兩個:一是芯片與封裝樹脂、芯片與裝片焊料、引線框架材料與封裝樹脂等之間的熱膨脹系數(shù)不匹配使產(chǎn)品瞬間受熱時內(nèi)部產(chǎn)生巨大應(yīng)力,導(dǎo)致分層;二是封裝樹脂耐濕性差,產(chǎn)品吸濕。當(dāng)封裝體在環(huán)境溫度劇變時,內(nèi)部水分急劇汽化,當(dāng)蒸汽壓力大于封裝樹脂與芯片、載片以及框架表面之間的粘接力,以致于使它們的界面之間出現(xiàn)剝離現(xiàn)象,嚴重時還會導(dǎo)致封裝樹脂或芯片出現(xiàn)裂紋,此種情況一般在表面貼裝器件波峰焊接時較為常見,俗稱“爆米花”效應(yīng)。見下圖,紅色區(qū)域表明有嚴重離層發(fā)生。

六、 離層的有效控制

離層在產(chǎn)生的同時對芯片表面形成較大的剪切力,當(dāng)于剪切力大于芯片強度時,芯片的破裂就產(chǎn)生了。因此如何有效控制表面貼裝MOSFET產(chǎn)品封裝及波峰焊接過程中離層的產(chǎn)生,是降低產(chǎn)品上線早期失效的一個關(guān)鍵。為此國際JEDEC(電子工程設(shè)計發(fā)展聯(lián)合會議)組織制訂了《JESD22-A111》控制標(biāo)準,可作為實際生產(chǎn)控制與檢驗標(biāo)準。

(《JESD22-A111》全稱為“Evaluation Procedure for Determining Capability to Bottom Side Board Attach by Full Body Solder Immersion of Small Surface Mount Solid State Devices” 中文解釋為“評價決定表面貼裝類產(chǎn)品浸入焊料性能的程序”)

同時正確地選用各種封裝材料,特別注意選用低應(yīng)力的高溫裝片焊料、選用低應(yīng)力高耐濕性的塑封料、注意引線框架的選材和設(shè)計均是封裝工藝工程師所需要重點研究的項目。

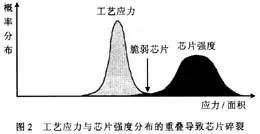

七、芯片強度

芯片強度是研究芯片碎裂的另一個重要參數(shù)。芯片強度各不相同,只有強度最低的才最容易碎裂失效。此外,強度分布范圍很廣,那些最“脆弱”的芯片碎裂時候的強度只相當(dāng)于芯片平均強度的幾分之一。因此只需設(shè)法將最“脆弱”芯片的強度提高或者予以剔除,就能從根本上提高芯片整體強度。下圖給出了工藝應(yīng)力與芯片強度的大致分布,兩者重疊區(qū)域表示可能發(fā)生芯片碎裂。

硅和其它半導(dǎo)體材料屬于高脆性材料,在材料完整無缺陷時,外加應(yīng)力在樣品上的分布是均勻的。它們在碎裂時是由于原子間的鍵發(fā)生斷裂,因而它們的機械強度就決定于鍵的強度。在材料表面出現(xiàn)劃痕后,外加應(yīng)力時,出現(xiàn)應(yīng)力集中現(xiàn)象。特別對于垂直于表面劃痕的張應(yīng)力,應(yīng)力集中于裂紋的尖端。裂紋的擴展取決于裂紋尖端的應(yīng)力分布。當(dāng)其應(yīng)力超過材料的應(yīng)力強度因子時,裂紋就會失去穩(wěn)定而發(fā)生擴展。因而對于脆性材料來說,表面劃痕對材料的強度有很大的影響。尤其是對于半導(dǎo)體器件中的薄芯片,它的厚度很小,表面劃痕的影響將更為嚴重。

八、表面劃痕產(chǎn)生的原因分析與控制

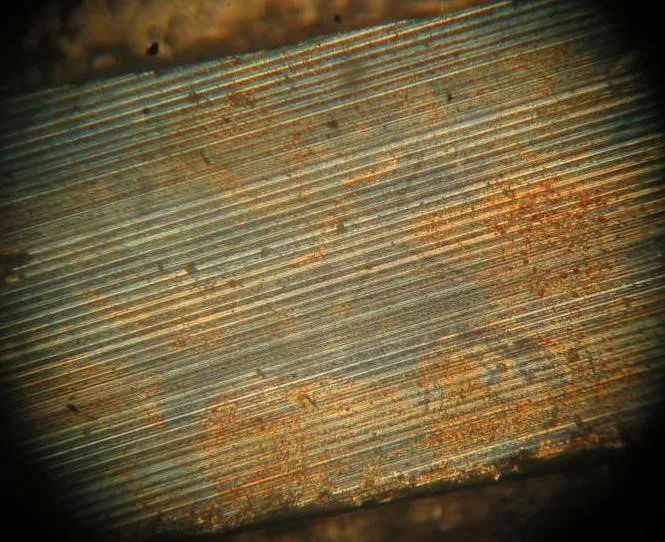

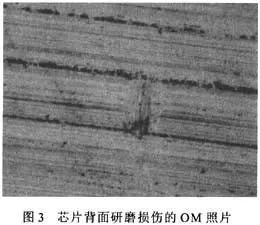

表面劃痕產(chǎn)生的原因之一:減薄(磨片):

硅片減薄,一般采用磨削法,是利用固定在特定模具上的尺寸適宜的金剛砂輪對硅片背面進行磨削,磨片引起的背面損傷(如圖3)極大地影響了硅片的強度,尤其在硅片不同介質(zhì)層的作用下,薄硅片很容易彎曲變形,產(chǎn)生了碎裂隱患。

改善手段:正確選用砂輪,砂輪磨料的粒度大小直接影響硅片亞表面的損傷程度。在細磨工藝后可采用濕法腐蝕工藝、常壓等離子腐蝕、化學(xué)機械拋光等方法去除硅片背面的殘留的晶格損傷層與殘余應(yīng)力,大大增強芯片強度,避免硅片因殘余應(yīng)力而碎裂。

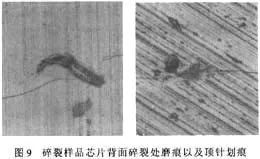

表面劃痕產(chǎn)生的原因之二:劃片

芯片劃片槽的斷面往往比較粗糙,有少量微裂紋(崩角)和凹槽存在;同時有些地方劃片時并未劃透,裝片時頂針向上頂使芯片“被迫”分離,致使斷口呈不規(guī)則狀。實驗顯示,劃片引起的芯片邊緣的損傷同樣會嚴重影響芯片的碎裂強度。(見下圖)

改善手段:改善劃片工藝,盡可能地降低切割殘余量,從而減少崩角產(chǎn)生的幾率。

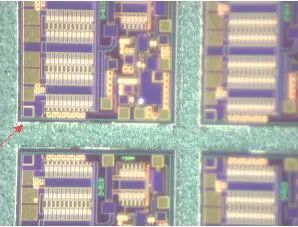

表面劃痕產(chǎn)生的原因之三:粘片(裝片)

粘片工藝包括裝片機頂針從薄膜上頂起芯片,真空吸頭吸起芯片將其粘結(jié)到芯片引線框架上。對芯片的損傷主要表現(xiàn)為頂針刺破藍膜而損傷芯片。見下圖:

改善手段:裝片過程中,頂針的頂出高度、拾取高度、吸嘴的大小、頂針的選用等必須隨芯片厚度、芯片大小不同而進行調(diào)整,同時對芯片背面頂針損傷進行有效質(zhì)量監(jiān)控,以防止頂針刺破藍膜而損傷芯片。

結(jié)論

芯片碎裂已經(jīng)成為表面貼裝MOSFET 產(chǎn)品上線失效的主要模式之一,封裝材料及工藝選配的不合理,在產(chǎn)品瞬間受熱時產(chǎn)生的過大應(yīng)力是造成產(chǎn)品失效的主要原因。而硅片減薄、劃片、裝片過程中對芯片的損傷是芯片碎裂的主要誘因。通過優(yōu)化封裝工藝,選配合適的材料與工藝,將熱應(yīng)力控制在安全范圍內(nèi)。以及通過改進研磨工藝,采用合理的劃片技術(shù),改善裝片機的工藝參數(shù),將有利于降低芯片的碎裂幾率,從而進一步提高表面貼裝MOSFET 產(chǎn)品可靠性。

審核編輯:劉清

-

MOSFET

+關(guān)注

關(guān)注

149文章

8224瀏覽量

218271 -

PAD

+關(guān)注

關(guān)注

1文章

101瀏覽量

31017 -

smt

+關(guān)注

關(guān)注

42文章

3014瀏覽量

71217

原文標(biāo)題:表面貼裝MOSFET產(chǎn)品上線高失效原因初探

文章出處:【微信號:可靠性技術(shù)交流,微信公眾號:可靠性技術(shù)交流】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

表面貼裝焊接的不良原因和防止對策

表面貼裝的GDT

表面貼裝技術(shù)特點與分析

smt表面貼裝技術(shù)

表面貼裝焊接的不良原因和防止對策

表面貼裝型PGA

表面貼裝型PGA是什么意思

表面貼裝技術(shù)與通孔貼裝技術(shù)

Arduino Nanuno(表面貼裝版)

表面貼裝MOSFET產(chǎn)品上線高失效原因及其案例分析

表面貼裝MOSFET產(chǎn)品上線高失效原因及其案例分析

評論