減法器電路與原理

減法器是一種電路,它可以實(shí)現(xiàn)二進(jìn)制數(shù)字的減法運(yùn)算。減法器的工作原理基于位運(yùn)算和進(jìn)位/借位機(jī)制。

常見的減法器有硬件實(shí)現(xiàn)的二進(jìn)制減法器和軟件實(shí)現(xiàn)的程序減法器。硬件實(shí)現(xiàn)的減法器通常是由一組異或門(XOR)、與門(AND)和或門(OR)組成,而軟件實(shí)現(xiàn)的減法器則可以在計(jì)算機(jī)程序中實(shí)現(xiàn)。

在二進(jìn)制減法中,如果第二個(gè)操作數(shù)是被減數(shù),則第一個(gè)操作數(shù)是減數(shù)。減數(shù)和被減數(shù)的每一位分別被進(jìn)行異或運(yùn)算,然后再進(jìn)行與運(yùn)算,以確定是否需要進(jìn)位/借位。通過這種方式,減法器可以實(shí)現(xiàn)二進(jìn)制數(shù)的減法運(yùn)算。

減法器是一種用于實(shí)現(xiàn)二進(jìn)制數(shù)減法運(yùn)算的電路,它通過使用異或門、與門和或門來實(shí)現(xiàn)二進(jìn)制減法運(yùn)算的進(jìn)位/借位機(jī)制。

減法器電路圖分享

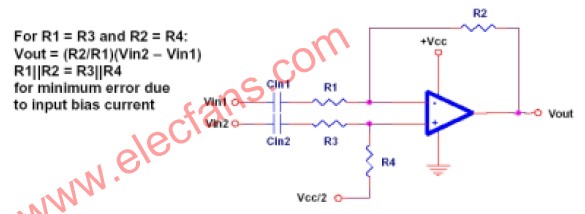

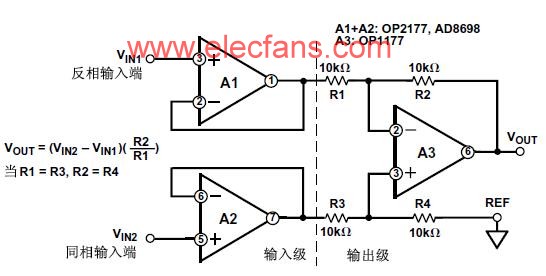

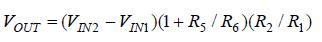

通用減法器電路

圖(a)電路輸入輸出關(guān)系為:V0=Vi2-Vi1圖中放大器的輸出信號(hào)電壓極性通常與輸入電壓極性相同。如果要求反相輸出,則采用圖(b)所示電路。其輸入輸出關(guān)系為:Vo=Vi1-Vi2。

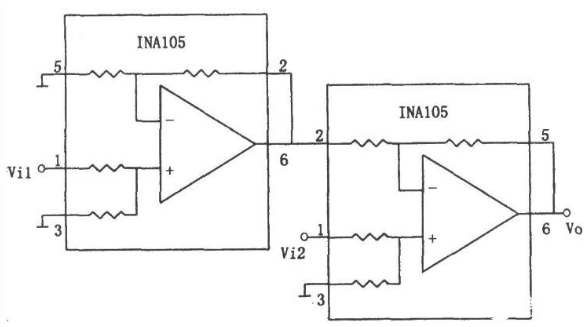

INA105構(gòu)成的減法電路

如圖所示為其他器件組成的減法電路(2)。該電路輸入輸出關(guān)系為:Vo=Vi2-Vi1。

-

放大器

+關(guān)注

關(guān)注

145文章

14090瀏覽量

216135 -

二進(jìn)制

+關(guān)注

關(guān)注

2文章

803瀏覽量

42122 -

減法器

+關(guān)注

關(guān)注

1文章

26瀏覽量

17013

發(fā)布評(píng)論請(qǐng)先 登錄

數(shù)字電路中加法器和減法器邏輯圖分析

8位減法器求解?

哪一個(gè)是減法器?負(fù)反饋在減法器電路中的原理?

如何用最簡單的方法設(shè)計(jì)一個(gè)減法器?

本的二進(jìn)制加法/減法器,本的二進(jìn)制加法/減法器原理

減法器電路

8位加法器和減法器設(shè)計(jì)實(shí)習(xí)報(bào)告

減法器電路設(shè)計(jì)方案匯總(五款模擬電路設(shè)計(jì)原理圖詳解)

FPGA常用運(yùn)算模塊-加減法器和乘法器

減法器電路與原理 減法器電路圖分享

減法器電路與原理 減法器電路圖分享

評(píng)論