怎么根據外圍電路配置單片機gpio的時鐘

根據外圍電路配置單片機GPIO的時鐘是一項重要的任務,它決定了單片機與外部設備的通信速度和穩定性。在本文中,我將詳細介紹如何根據外圍電路配置單片機GPIO的時鐘。

一、時鐘信號的基本原理

時鐘信號是單片機內部各個模塊同步運行的基礎,是單片機操作和功能的支持。單片機通常有內部時鐘源和外部時鐘源兩種形式。

內部時鐘源由單片機內部的振蕩器驅動,通常有RC振蕩器和晶體振蕩器兩種形式。RC振蕩器是通過電阻和電容來實現的,成本低廉但不夠穩定;晶體振蕩器則采用晶振元件,精度高但成本較高。

外部時鐘源由外部電路提供,可以是晶振、電路或其他穩定的高頻信號。這種方式可提供更高的時鐘頻率和更好的精度,適用于對時鐘信號要求較高的應用。

二、外圍電路配置時鐘信號

理論上,外圍電路可以使用各種方式來配置時鐘信號,但最常見的方式是使用晶振。以下是配置時鐘信號的詳細步驟:

1. 確定時鐘信號的頻率和精度要求。根據單片機型號的規格書或應用需求,確定所需的時鐘頻率和精度。

2. 選擇合適的晶振。根據時鐘信號的頻率和精度要求,在市場上選擇合適的晶振元件。一般來說,晶振元件有多種頻率和精度可供選擇。

3. 連接晶振元件。將晶振元件連接到單片機的時鐘引腳上。時鐘引腳通常標有CLK、OSC或XTAL等標志,根據單片機的規格書確定具體的引腳號。

4. 連接電容。對于晶振元件,通常需要連接兩個電容到單片機的時鐘引腳上,以提供穩定的工作環境。電容的選擇和連接方式需要根據晶振元件的規格書來確定。

5. 設計電路板。根據晶振元件的封裝形式和引腳排列,設計電路板布線。確保晶振元件引腳與單片機時鐘引腳之間能夠正確連接,并注意避開其他干擾源。

6. 布線分析和優化。對電路板進行布線分析和優化,確保時鐘信號的傳輸路徑最短、最穩定,并盡可能減少干擾源對時鐘信號的影響。

7. 進行測試和驗證。完成電路板的布線后,進行測試和驗證。通過示波器、頻譜儀或其他合適的工具,檢測時鐘信號的頻率、穩定性和精度是否符合要求。

8. 調整和優化。根據測試結果,對電路進行調整和優化,以獲得更好的時鐘信號質量和性能。

以上是基于晶振元件的時鐘信號配置流程,對于其他類型的外部時鐘源,也可以參考類似的步驟進行配置。

三、常見問題和注意事項

1. 時鐘信號的頻率和精度需要符合單片機的規格要求和應用需求,過高或過低的頻率都可能影響單片機的正常工作。

2. 晶振元件的選擇要根據單片機的規格書和應用需求來確定,頻率和精度要與單片機匹配。

3. 電容的選擇和布線要符合晶振元件的規格要求,以提供穩定的工作環境。

4. 布線要合理,盡量減少干擾源對時鐘信號的影響。時鐘信號的傳輸路徑應盡量短,盡量避免與其他高頻、高電壓信號的交叉、干擾。

5. 在進行測試和驗證時,應使用合適的工具和方法,確保時鐘信號的質量和性能符合要求。

總結:

根據外圍電路配置單片機GPIO的時鐘是一個關鍵的任務,通過選擇合適的外部時鐘源并進行正確的連接、布線和調試,可以確保單片機的穩定工作和高性能。

在配置時鐘信號時,需要根據單片機的規格書和應用需求,選擇合適的時鐘頻率和精度。在連接和布線時,需要根據外部時鐘源的規格要求,設計合適的電路板布線。最后,通過測試和驗證,調整和優化,可以獲得滿足要求的時鐘信號,并確保單片機的正常工作。

-

單片機

+關注

關注

6063文章

44925瀏覽量

646982 -

GPIO

+關注

關注

16文章

1274瀏覽量

53585 -

時鐘信號

+關注

關注

4文章

465瀏覽量

29078

發布評論請先 登錄

單片機外圍電路設計 (第2版)

單片機學習之GPIO

單片機芯片不直接集成所有外圍電路?

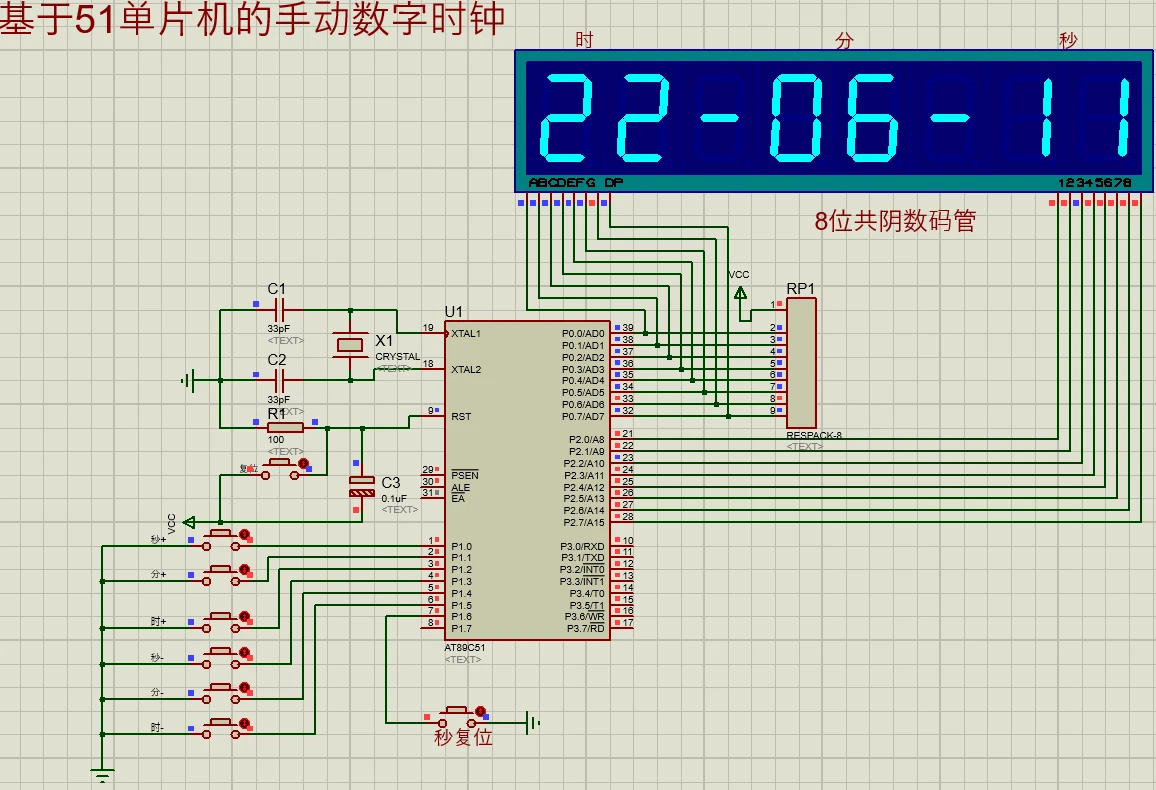

基于51單片機的手動數字時鐘

怎么根據外圍電路配置單片機gpio的時鐘

怎么根據外圍電路配置單片機gpio的時鐘

評論