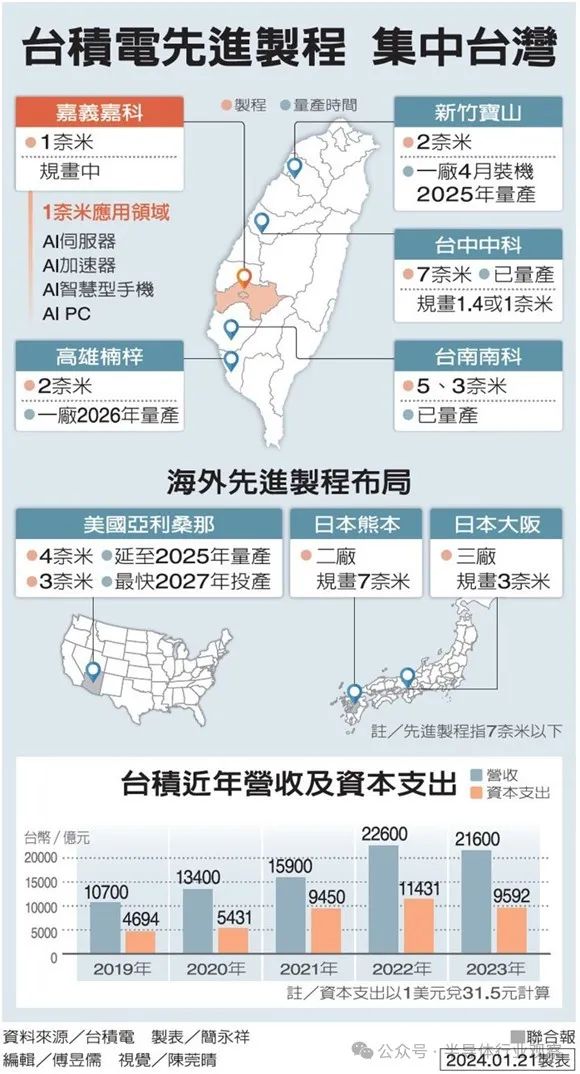

投資金額逾兆元的臺積電一納米建廠計劃,擬在嘉義縣太保市的科學園區設廠。這是臺積電繼日前法說會宣布在高雄廠增建第三座二納米晶圓廠。

消息人士透露,臺積電已向主管嘉義科學園區的南科管理局提出一百公頃用地需求,其中四十公頃設先進封裝廠,后續六十公頃將作為一納米建廠用地。由于臺積電用地需求超出嘉義科學園區第一期規劃的八十八公頃面積,預期將加速第二期擴編,以利臺積電進駐。

臺積電表示,設廠地點選擇有諸多考量因素,臺積電以臺灣作為主要基地,不排除任何可能,也持續與管理局合作評估在適合半導體建廠用地。臺積電指出,一切資訊請以公司對外公告為主。

嘉義縣長翁章梁指出,尊重臺積電設廠地點決定,相信會有最佳評估,誠摯歡迎臺積電投資嘉義、更歡迎優秀的人才來嘉義,相信嘉縣未來幾年將成為西部走廊最具競爭力和發展潛力城市。他也說,嘉義科學園區目前綠電充足,也擬興建海水淡化廠,為產業打造發展好基地,優渥條件絕對是首選。

據了解,臺積電建廠小組在嘉義科學園區去年八月編定納入南科管理局管轄的科學園區前,即派人前往進行廠勘,這也是在進駐桃園龍潭科學園區第三期擴建遭激烈抗爭后,臺積電建廠小組啟動備案計劃,最后決定放棄在龍科三期擴建案內的設廠計劃。

臺積電放棄龍潭建廠后,立即引來包括高雄、臺中、彰化、嘉義、云林、臺南及屏東等各縣市首長爭相拉攏前去投資,各地方政府也都表明將在土地和供水供電全力協助。翁章梁當時即表態,若臺積電要到嘉義評估,他將擔任召集人,并組專業小組全力協助,并強調該縣有很多臺糖土地,未來征收不會有太大問題。

不過,臺積電長期向國科會主管的管理局租地,雙方建立單一窗口,最后擇定落腳嘉義科學園區,主要是因為此科學園區地理位置佳、 土地面積完整,并具可擴充性。這與翁章梁說法吻合。

一納米制程落腳嘉科,可分散區域風險,也有利嘉義縣城市發展,縮小城鄉差距。再者,嘉義科學園區離嘉義高鐵站車程僅七分鐘,往北串起臺積電中科、竹科廠,往南串連南科廠及高雄廠,均符合臺積電創辦人張忠謀先前所提可在一日內動員上千名工程師支援各廠區運作,讓臺灣西部科技廊帶更完整。

業界人士分析,臺積電進來宣布高雄擴建第三座2納米廠、美國二廠踩煞車、1納米落腳嘉義,宣示了臺積電將先進制程根留臺灣的決心。

此舉不僅向全球芯片商表達「你要最具性價比且最先進的芯片代工,就是要來臺灣生產」,也向三星及英特爾展現臺積電擁有全球最完善的晶圓代工生態系,加上政策強力支持,要撼動臺積電全球晶圓代工龍頭地位,套句臺積電總裁魏哲家的話「門都沒有!」

臺積電2nm工廠,也規劃了兩座

當臺積電 (TSMC) 準備推出全新工藝技術時,通常會建造一座新晶圓廠來滿足其 alpha 客戶的需求,然后通過升級現有晶圓廠或建造另一座工廠來增加產能。對于 N2(2 納米級),該公司似乎采取了略有不同的方法,因為它已經建造了兩座具備 N2 能力的晶圓廠,并正在等待政府批準第三座晶圓廠。

我們還準備從 2025 年開始量產 N2,”臺積電即將離任的董事長劉馬克在與財務分析師和投資者舉行的公司財報電話會議上表示。“我們計劃在新竹和高雄建設多個晶圓廠或多期 2nm 技術科學園,以支持客戶強勁的結構性需求。[…]“在臺中科學園區,政府審批程序正在進行中,也已步入正軌。”

臺積電正準備在臺灣建設兩家能夠生產 N2 芯片的制造工廠。第一個晶圓廠計劃選址新竹縣寶山附近,毗鄰 R1 研發中心,該中心是專門為開發 N2 技術及其后續技術而建造的。該工廠預計將于 2025 年下半年開始大批量制造 (HVM) 2 納米芯片。第二個具有 N2 能力的制造工廠將位于高雄科學園區,該園區是高雄附近的南臺灣科學園區的一部分。該工廠 HVM 的啟動預計會稍晚一些,可能在 2026 年左右。

此外,該代工廠正在努力獲得政府批準,在臺中科學園區建造另一座具有 N2 能力的晶圓廠。如果該公司在 2025 年開始建設該工廠,該工廠最快可在 2027 年投產。

臺積電擁有三個能夠使用其 2nm 工藝技術制造芯片的晶圓廠,準備在未來幾年提供巨大的 2nm 產能。

臺積電預計在 2025 年下半年左右啟動使用其 N2 工藝技術的 HVM,該技術采用環柵 (GAA) 納米片晶體管。臺積電的第二代2納米級工藝技術 - N2P - 將增加背面功率傳輸。該技術將于2026年實現量產。

1nm后的芯片,靠什么?

毫無疑問,下一代的CMOS邏輯將邁入1nm時代,在即將舉行的IEDM上,。有不少關于“下一代 CMOS”的著名講座。因此,我們將它們分為“互補FET”、“2D材料”和“多層布線”子類別。

在本文中,按順序進行介紹。

將構成 CMOS 的兩個 FET 堆疊起來,將硅面積減少一半

第一個是“下一代 CMOS 邏輯”領域中的“互補 FET (CFET)”。CMOS邏輯(邏輯電路)由至少兩個晶體管組成:一個n溝道MOS FET和一個p溝道MOS FET。晶體管數量最少的邏輯電路是反相器(邏輯反相電路),由1個n溝道MOS和1個p溝道MOS組成。換句話說,它需要相當于兩個晶體管的硅面積。

CFET 是這兩種類型 MOSFET 的三維堆疊。理論上,可以使用一個 FET 占用的硅面積來創建 CMOS 邏輯。與傳統CMOS相比,硅面積減半。但制造工藝相當復雜,挑戰重重,打造難度較大。

在IEDM 2023上,CFET研發取得了重大進展。臺積電和英特爾均推出了單片堆疊下層 FET 和上層 FET 的 CMOS 電路。TSMC 演示了一個 CFET 原型,該原型將 n 溝道 FET 單片堆疊在 p 溝道 FET 之上。所有 FET 均具有納米片結構。柵極間距為48nm。制造成品率達90%以上。目前的開/關比超過6位數。

Intel 設計了一個 CFET 原型,將三個 n 溝道 FET 單片堆疊在三個 p 溝道 FET 之上 (29-2)。所有 FET 均具有納米帶結構(與納米片結構基本相同的結構)。我們制作了柵極間距為 60nm 的 CMOS 反相器原型并確認了其運行。

采用二維材料制成GAA結構的納米片通道

下一代 CMOS 邏輯晶體管的另一個有希望的候選者是通道是過渡金屬二硫屬化物 (TMD) 化合物的二維材料(單層和極薄材料)的晶體管。當 MOSFET 的溝道尺寸縮短時,“短溝道效應”成為一個主要問題,其中閾值電壓降低且變化增加。減輕短溝道效應的一種方法是使溝道變薄。TMD很容易形成單分子層,原則上可以創建最薄的通道。

TMD 溝道最初被認為是一種用于小型化傳統平面 MOSFET 的技術(消除了對鰭結構的需要)。最近,選擇TMD作為環柵(GAA)結構的溝道材料的研究變得活躍。候選通道材料包括二硫化鉬(MoS2)、二硫化鎢(WS2)和二硒化鎢(WSe2)。

包括臺積電等在內的聯合研究小組開發了一種具有納米片結構的n溝道FET,其中溝道材料被單層MoS2取代。柵極長度為40nm。閾值電壓高,約為1V(常關操作),導通電流約為370μA/μm(Vds約為1.0V),電流開關比為10的8次方。

imec和 Intel 的聯合研究團隊使用二維溝道候選材料在 300mm 晶圓上制造了原型 n 溝道 MOS 和 p 溝道 MOS,并評估了它們的特性。候選材料有 MoS2、WS2和 WSe2。MoS2單層膜適用于n溝道FET,WSe多層膜適用于p溝道FET。

包括臺積電等在內的聯合研究小組開發出一種二維材料晶體管,其電流-電壓特性與n溝道FET和p溝道FET相同。MoS2(一種 n 溝道材料)和 WSe2(一種 p 溝道材料)在藍寶石晶圓上生長,并逐個芯片轉移到硅晶圓上。此外,英特爾還原型制作了具有GAA結構的二維材料溝道FET,并在n溝道和p溝道上實現了相對較高的遷移率。

石墨烯、釕和鎢將取代銅 (Cu) 互連

多層布線是支持CMOS邏輯擴展的重要基礎技術。人們擔心,當前流行的銅(Cu)多層互連的電阻率將由于小型化而迅速增加。因此,尋找金屬來替代 Cu 的研究非常活躍。候選材料包括石墨烯、釕 (Ru) 和鎢 (W)。

臺積電將宣布嘗試使用石墨烯(一種片狀碳同素異形體)進行多層布線。當我們制作不同寬度的互連原型并將其電阻與銅互連進行比較時,我們發現寬度為15 nm或更小的石墨烯互連的電阻率低于銅互連的電阻率。石墨烯的接觸電阻率也比銅低四個數量級。將金屬離子嵌入石墨烯中可以改善互連的電性能,使其成為下一代互連的有前途的材料。

imec 制作了高深寬比 (AR) 為 6 至 8、節距為 18 nm 至 26 nm 的 Ru 兩層精細互連原型,并評估了其特性。制造工藝為半鑲嵌和全自對準過孔。在AR6中原型制作寬度為10 nm(對應間距18 nm至20 nm)的Ru線測得的電阻值低于AR2中模擬的Cu線的電阻值。

應用材料公司開發了一種充分利用 W的低電阻互連架構。適用于2nm以上的技術節點。我們充分利用 W 襯墊、W 間隙填充和 W CMP(化學機械拋光)等基本技術。

將存儲器等元件納入多層布線過程

一種有些不尋常的方法是研究多層互連過程(BEOL)中的存儲器等構建元件。多層布線下面通常是 CMOS 邏輯電路。因此,理論上,BEOL 中內置的元件不會增加硅面積。它是提高存儲密度和元件密度的一種手段。

斯坦福大學和其他大學的聯合研究小組將提出在多層邏輯布線工藝中嵌入氧化物半導體 (OS) 增益單元晶體管型存儲元件的設計指南。操作系統選擇了氧化銦錫 (ITO) FET。我們比較了 OS/Si 混合單元和 OS/OS 增益單元。

imec 開發了MRAM技術,可將自旋軌道扭矩 (SOT) 層和磁隧道結 (MTJ) 柱減小到大致相同的尺寸。它聲稱可以將功耗降低到傳統技術的三分之一,將重寫周期壽命延長10的15次方,并減少存儲單元面積。

加州大學洛杉磯分校率先集成了壓控 MRAM 和 CMOS 外圍電路。MRAM的切換時間極短,為0.7ns(電壓1.8V)。原型芯片的讀取訪問時間為 8.5ns,寫入周期壽命為 10 的 11 次方。

將計算功能納入傳感器中

我還想關注“傳感器內計算技術”,它將某種計算功能集成到傳感器中。包括旺宏國際在內的聯合研究小組將展示基于 3D 單片集成技術的智能圖像傳感器。使用 20nm 節點 FinFET 技術,將類似于 IGZO DRAM 的存儲層單片層壓在 CMOS 電路層的頂部,并在其頂部層壓由二維材料 MoS2制成的光電晶體管陣列層。光電晶體管陣列的布局為 5 x 5。

西安電子科技大學和西湖大學的聯合研究小組設計了一種光電神經元,由一個光電晶體管和一個閾值開關組成,用于尖峰神經網絡。對連續時間內的傳感信號(光電轉換信號)進行壓縮編碼。

在硅晶圓上集成 GaN 功率晶體管和 CMOS驅動器

對于能帶隙比 Si 更寬的化合物半導體器件(寬禁帶器件),在 Si 晶圓上制造氮化鎵 (GaN) 基 HEMT 的運動十分活躍。英特爾在 300mm 硅晶圓上集成了 GaN 功率晶體管和 CMOS 驅動器。CMOS驅動器是GaN增強型n溝道MOS HEMT和Si p溝道MOS FET的組合。用于GaN層的Si晶片使用面。對于 Si MOS FET,將另一個面的硅晶片粘合在一起,只留下薄層,用作溝道。

CEA Leti 開發了用于 Ka 波段功率放大器的 AlN/GaN/Si MIS-HEMT (38-3)。兼容200mm晶圓Si CMOS工藝。通過優化SiN柵極絕緣膜原型制作的HTMT的ft為81GHz,fmax為173GHz。28GHz 時的 PAE(功率負載效率)極高,達到 41%(電壓 20V)。假設我們已經實現了與 GaN/SiC 器件相當的性能。

6400萬像素、像素尺寸為0.5μm見方的小型CMOS圖像傳感器。

在圖像傳感器中,顯著的成果包括像素數量的增加、像素尺寸的減小、噪聲的減少以及自動對焦功能的進步。三星電子已試制出具有 6400 萬像素、小像素尺寸為 0.5 μm 見方的高分辨率 CMOS 圖像傳感器。

使用銅電極混合鍵合堆疊三個硅晶片,并為每個像素連接一個光電二極管和后續電路。與傳統型號相比,RTS(隨機電報信號)噪聲降低了 85%,FD(浮動擴散)轉換增益提高了 67%。

OmniVision Technologies 開發了一款 HDR 全局快門 CMOS 圖像傳感器,其像素間距為 2.2μm。它是通過將兩片硅片粘合在一起而制成的。FPN(固定模式噪聲)為1.2e-(rms值),時間噪聲為3.8e-(rms值)。

佳能已經推出了雙像素交叉 CMOS 圖像傳感器原型,其中一對光電二極管以 90 度扭轉排列。通過全方位相位差檢測執行自動對焦 (AF)。AF 的最低照度低至 0.007 lux。

-

臺積電

+關注

關注

44文章

5738瀏覽量

168882 -

晶圓廠

+關注

關注

7文章

636瀏覽量

38328 -

光電二極管

+關注

關注

10文章

415瀏覽量

36495

原文標題:臺積電,1nm

文章出處:【微信號:jbchip,微信公眾號:電子元器件超市】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

1nm后的芯片,靠什么?

1nm后的芯片,靠什么?

評論