一、摘要

DE2_TV中,有關(guān)于寄存器的配置的部分,采用的方法是通過(guò)IIC的功能,這里對(duì)IIC總線的FPGA實(shí)現(xiàn)做個(gè)說(shuō)明。

二、實(shí)驗(yàn)平臺(tái)

軟件平臺(tái):ModelSim-Altera 6.4a (Quartus II 9.0)

硬件平臺(tái):DIY_DE2

三、實(shí)驗(yàn)原理

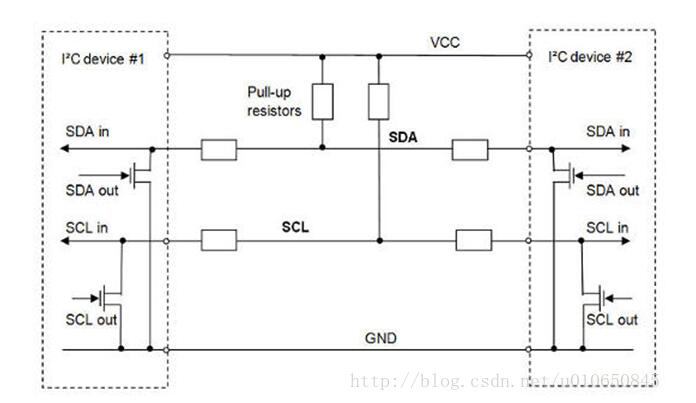

1、IIC總線器件工作原理

在IIC總線上傳送信息時(shí)的時(shí)鐘同步信號(hào)是由掛接在SCL時(shí)鐘線上的所有器件的邏輯“與”完成的。SCL線上由高電平到低電平的跳變將影響到這些器件,一旦某個(gè)器件的時(shí)鐘信號(hào)變?yōu)榈碗娖剑瑢⑹筍CL線上所有器件開(kāi)始并保護(hù)低電平期。此時(shí),低電平周期短的器件的時(shí)鐘由低至高的跳變并不影響SCL線的狀態(tài),這些器件將進(jìn)入高電平等待的狀態(tài)。

當(dāng)所有器件的時(shí)鐘信號(hào)都變?yōu)楦唠娖綍r(shí),低電平期結(jié)束,SCL線被釋放返回高電平,即所有的器件都同時(shí)開(kāi)始它們的高電平期。其后,第一個(gè)結(jié)束高電平期的器件又將SCL線拉成低電平。這樣就在SCL線上產(chǎn)生一個(gè)同步時(shí)鐘。可見(jiàn),時(shí)鐘低電平時(shí)間由時(shí)鐘低電平期最長(zhǎng)的器件決定,而時(shí)鐘高電平時(shí)間由時(shí)鐘高電平期最短的器件決定。

IIC總線上數(shù)據(jù)的傳輸速率在標(biāo)準(zhǔn)模式下可達(dá)100kbit/s 在快速模式下可達(dá)400kbit/s 在高速模式下可達(dá)3.4Mbit/s ,連接到總線的接口數(shù)量只由總線電容是400pF 的限制決定。

2、IIC總線的傳輸協(xié)議與數(shù)據(jù)傳送時(shí)序

(1)起始和停止條件

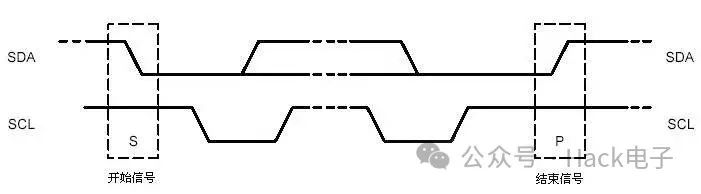

在數(shù)據(jù)傳送過(guò)程中,必須確認(rèn)數(shù)據(jù)傳送的開(kāi)始和結(jié)束。在IIC總線技術(shù)規(guī)范中,開(kāi)始和結(jié)束信號(hào)(也稱啟動(dòng)和停止信號(hào))的定義如圖1所示。

圖1起始和停止信號(hào)圖

開(kāi)始信號(hào):當(dāng)時(shí)鐘總線SCL為高電平時(shí),數(shù)據(jù)線SDA由高電平向低電平跳變,開(kāi)始傳送數(shù)據(jù)。

結(jié)束信號(hào):當(dāng)SCL線為高電平時(shí),SDA線從低電平向高電平跳變,結(jié)束傳送數(shù)據(jù)。

開(kāi)始和結(jié)束信號(hào)都是由主器件產(chǎn)生。在開(kāi)始信號(hào)以后,總線即被認(rèn)為處于忙狀態(tài),其它器件不能再產(chǎn)生開(kāi)始信號(hào)。主器件在結(jié)束信號(hào)以后退出主器件角色,經(jīng)過(guò)一段時(shí)間過(guò),總線被認(rèn)為是空閑的。(2)數(shù)據(jù)格式

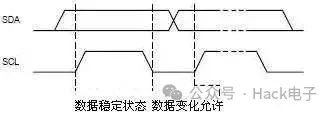

IIC總線數(shù)據(jù)傳送采用時(shí)鐘脈沖逐位串行傳送方式,在SCL的低電平期間,SDA線上高、低電平能變化,在高電平期間,SDA上數(shù)據(jù)必須保護(hù)穩(wěn)定,以便接收器采樣接收,時(shí)序如圖2所示。

圖2 數(shù)據(jù)傳送時(shí)序圖

IIC總線發(fā)送器送到SDA線上的每個(gè)字節(jié)必須為8位長(zhǎng),傳送時(shí)高位在前,低位在后。與之對(duì)應(yīng),主器件在SCL線上產(chǎn)生8個(gè)脈沖;第9個(gè)脈沖低電平期間,發(fā)送器釋放SDA線,接收器把SDA線拉低,以給出一個(gè)接收確認(rèn)位;第9個(gè)脈沖高電平期間,發(fā)送器收到這個(gè)確認(rèn)位然后開(kāi)始下一字節(jié)的傳送,下一個(gè)字節(jié)的第一個(gè)脈沖低電平期間接收器釋放SDA。每個(gè)字節(jié)需要9個(gè)脈沖,每次傳送的字節(jié)數(shù)是不受限制的。

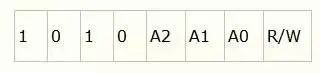

IIC總線的數(shù)據(jù)傳送格式是在IIC總線開(kāi)始信號(hào)后,送出的第一字節(jié)數(shù)據(jù)是用來(lái)選擇從器件地址的,其中前7位為地址碼,第8位為方向位(R/W)。方向位為“0”表示發(fā)送,即主器件把信息寫到所選擇的從器件中;方向位為“1”表示主器件將從從器件讀信息。格式如下:

開(kāi)始信號(hào)后,系統(tǒng)中的各個(gè)器件將自己的地址和主器件送到總線上的地址進(jìn)行比較,如果與主器件發(fā)送到總線上的地址一致,則該器件即被主器件尋址的器件,其接收信息還是發(fā)送信息則由第8位(R/W)決定。發(fā)送完第一個(gè)字節(jié)后再開(kāi)始發(fā)數(shù)據(jù)信號(hào)。(3)響應(yīng)

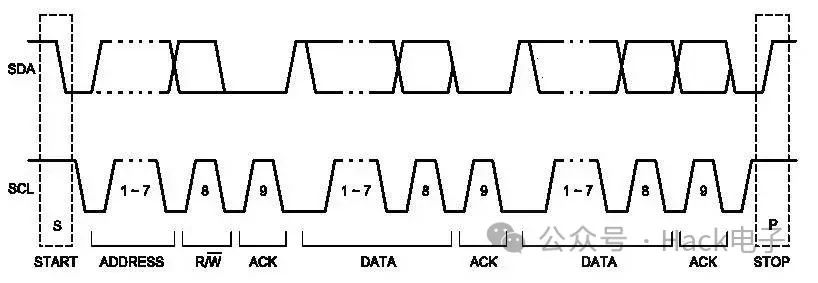

數(shù)據(jù)傳輸必須帶響應(yīng)。相關(guān)的響應(yīng)時(shí)鐘脈沖由主機(jī)產(chǎn)生,當(dāng)主器件發(fā)送完一字節(jié)的數(shù)據(jù)后,接著發(fā)出對(duì)應(yīng)于SCL線上的一個(gè)時(shí)鐘(ACK)認(rèn)可位,此時(shí)鐘內(nèi)主器件釋放SDA線,一字節(jié)傳送結(jié)束,而從器件的響應(yīng)信號(hào)將SDA線拉成低電平,使SDA在該時(shí)鐘的高電平期間為穩(wěn)定的低電平。從器件的響應(yīng)信號(hào)結(jié)束后,SDA線返回高電平,進(jìn)入下一個(gè)傳送周期。

通常被尋址的接收器在接收到的每個(gè)字節(jié)后必須產(chǎn)生一個(gè)響應(yīng)。當(dāng)從機(jī)不能響應(yīng)從機(jī)地址時(shí),從機(jī)必須使數(shù)據(jù)線保持高電平,主機(jī)然后產(chǎn)生一個(gè)停止條件終止傳輸或者產(chǎn)生重復(fù)起始條件開(kāi)始新的傳輸。如果從機(jī)接收器響應(yīng)了從機(jī)地址但是在傳輸了一段時(shí)間后不能接收更多數(shù)據(jù)字節(jié),主機(jī)必須再一次終止傳輸。這個(gè)情況用從機(jī)在第一個(gè)字節(jié)后沒(méi)有產(chǎn)生響應(yīng)來(lái)表示。從機(jī)使數(shù)據(jù)線保持高電平主機(jī)產(chǎn)生一個(gè)停止或重復(fù)起始條件。完整的數(shù)據(jù)傳送過(guò)程如圖3所示。

圖3 完整的數(shù)據(jù)傳送過(guò)程

另外,IIC總線還具有廣播呼叫地址用于尋址總線上所有器件的功能。若一個(gè)器件不需要廣播呼叫尋址中所提供的任何數(shù)據(jù),則可以忽咯該地址不作響應(yīng)。如果該器件需要廣播呼叫尋址中按需提供的數(shù)據(jù),則應(yīng)對(duì)地址作出響應(yīng),其表現(xiàn)為一個(gè)接收器。

四、實(shí)驗(yàn)過(guò)程

根據(jù)上述的實(shí)驗(yàn)原理,對(duì)DE2_TV中的IIC部分進(jìn)行modelsim仿真。

1、IIC所需時(shí)鐘的仿真

FPGA作為IIC器件的主機(jī),要產(chǎn)生IIC的工作時(shí)鐘,下面先對(duì)IIC所需的時(shí)鐘信號(hào)進(jìn)行仿真。

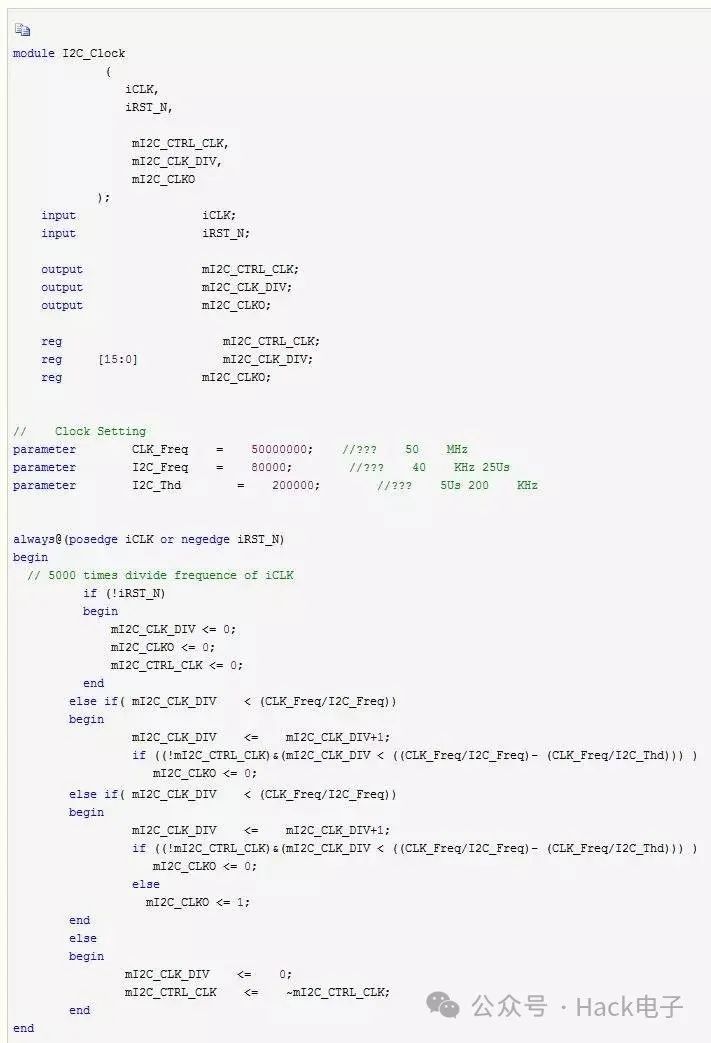

待仿真的時(shí)鐘信號(hào)程序如下:

testbench程序如下:

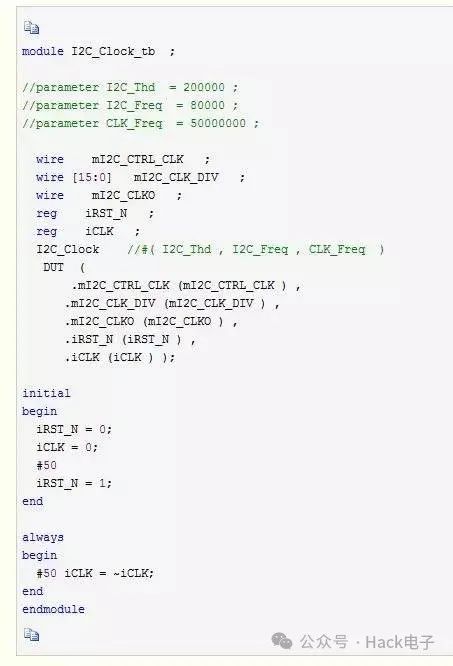

modelsim仿真的波形如下:

圖4 IIC內(nèi)部時(shí)鐘仿真圖

經(jīng)過(guò)計(jì)算,IIC內(nèi)部所用的時(shí)鐘頻率為40KHz。

2、IIC整體仿真

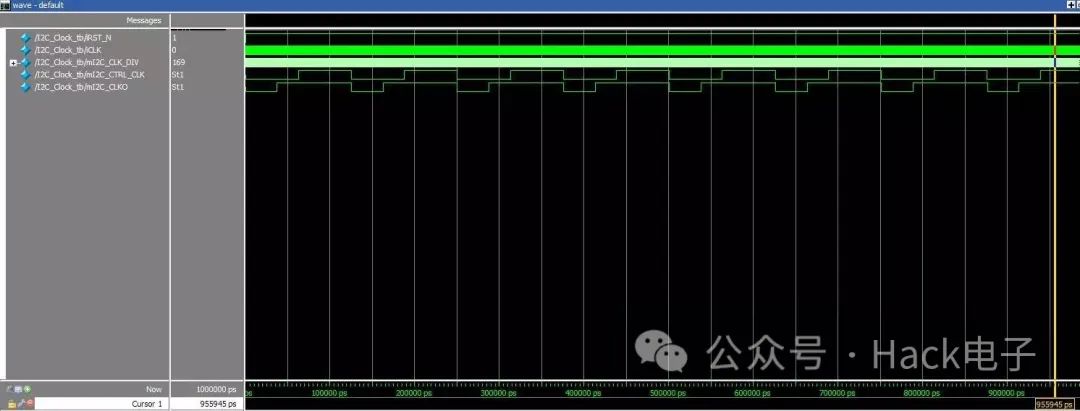

相關(guān)程序在附件中。下面是仿真波形。

圖5 IIC整體仿真波形圖

結(jié)合上述仿真波形圖和程序可以看出:

起始位:SCLK為高電平時(shí),SDAT由高到低,指示IIC總線傳輸數(shù)據(jù)的開(kāi)始;

之后,傳送一個(gè)字節(jié)的數(shù)據(jù),即4A,為從機(jī)的地址,隨后,跟了一個(gè)高電平,為應(yīng)答位;

之后,傳送一個(gè)字節(jié)的數(shù)據(jù),即01,為從機(jī)地址的子地址,隨后,跟了一個(gè)高電平,為應(yīng)答位;

之后,傳送一個(gè)字節(jié)的數(shù)據(jù),即08,為上面子地址寄存器配置的數(shù)據(jù),隨后,跟了一個(gè)高電平,為應(yīng)答位;

最后,為停止位,SCLK為高電平時(shí),SDAT由低到高,指示該次IIC總線傳輸數(shù)據(jù)的結(jié)束。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21941瀏覽量

613322 -

寄存器

+關(guān)注

關(guān)注

31文章

5412瀏覽量

123110 -

接口

+關(guān)注

關(guān)注

33文章

8918瀏覽量

153118 -

發(fā)送器

+關(guān)注

關(guān)注

1文章

261瀏覽量

27115 -

IC總線

+關(guān)注

關(guān)注

0文章

8瀏覽量

7292

原文標(biāo)題:技術(shù)貨:IIC總線的FPGA實(shí)現(xiàn)

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA實(shí)現(xiàn)模擬IIC總線

【FPGA參賽作品】用fpga模擬IIC總線并與外部設(shè)備進(jìn)行數(shù)據(jù)交流

IIC總線時(shí)序啟動(dòng)時(shí)序

IIC總線接口學(xué)習(xí)

一文解讀IIC總線的FPGA實(shí)現(xiàn)原理及過(guò)程

IIC總線接口的資料詳細(xì)說(shuō)明

C51—模擬IIC總線實(shí)現(xiàn)EEPROM存取數(shù)據(jù)

IIC總線上掛載多個(gè)從機(jī)的程序實(shí)現(xiàn)

基于IIC總線的FPGA實(shí)現(xiàn)方案

IIC總線的原理與Verilog實(shí)現(xiàn)

IIC總線的FPGA實(shí)現(xiàn)說(shuō)明

IIC總線的FPGA實(shí)現(xiàn)說(shuō)明

評(píng)論