RISC-V(發音為“RISC five”)的目標是成為一款通用的指令集架構(Instruction Set Architecture,ISA):

? 它要適合設計各種規模的處理器,包括從最小的嵌入式控制器到最快的高性能計算機。

? 它要兼容各種流行的軟件棧和編程語言。

? 它要適用于所有實現技術,包括 FPGA(Field-Programmable Gate Array,現場可編程邏輯門陣列)、ASIC(Application-Specific Integrated Circuit,專用集成電路)、全定制芯片,甚至未來的制造元件技術。

? 它能用于高效實現所有微體系結構,包括微程序或硬連線控制,順序、解耦或亂序流水線,單發射或超標量等。

? 它要支持高度定制化,成為定制加速器的基礎,以應對摩爾定律的放緩。

? 它要穩定,基礎 ISA 不會改變。更重要的是,它不能像以往的公司專有 ISA 那樣消亡,包括 AMD 的 Am29000、Digital 的 Alpha 和 VAX、Hewlett Packard1 的 PARISC、Intel 的 i860 和 i960、Motorola 的 88000,以及Zilog 的 Z8000。

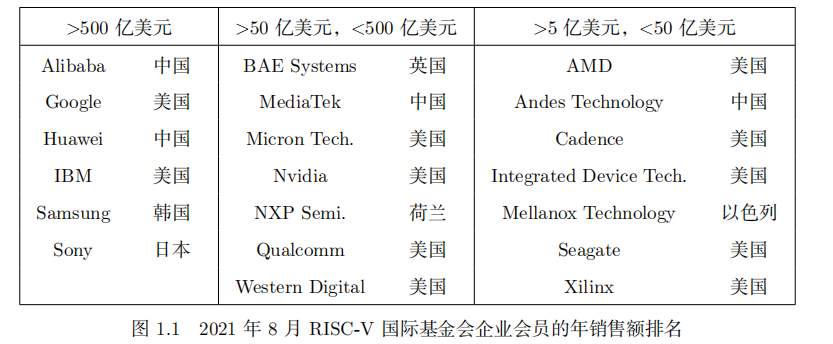

RISC-V 是一款與眾不同的 ISA,不僅因為它年輕(它誕生于 2010 年,而其他 ISA 大多誕生于 20 世紀 70 年代或 80年代),而且因為它開放。與過去幾乎所有的架構不同,其未來不受任何一家公司的興衰或心血來潮的決策所影響(過去許多 ISA 因此消亡)。相反,RISC-V 屬于一個開放的、非營利性質的基金會。RISC-V 國際基金會的目標是維護 RISC-V 的穩定性,僅出于技術原因而緩慢謹慎地改進 RISC-V,并推動RISC-V 在硬件中流行起來,猶如 Linux 在操作系統中流行一般。圖 1.1 列出了 RISC-V 國際基金會最大的企業會員,展示了 RISC-V 的繁榮。

模塊化ISA和增量型ISA

Intel 曾將其未來押在高端微處理器上,但這還需要很多年時間。為與 Zilog 公司抗衡,Intel 開發了一款名為8086 的過渡產品。它本該朝生暮死,無任何后續產品,但事實并非如此。高端處理器姍姍來遲,等它最終面世時,性能卻不如人意。因此,8086 架構得以延續——它演化為 32 位處理器,最終又演化為 64 位。其名稱不斷更替(80186、80286、i386、i486、Pentium),但底層指令集絲毫未減。 ——Stephen P. Morse,8086 架構師 (Morse, 2017)

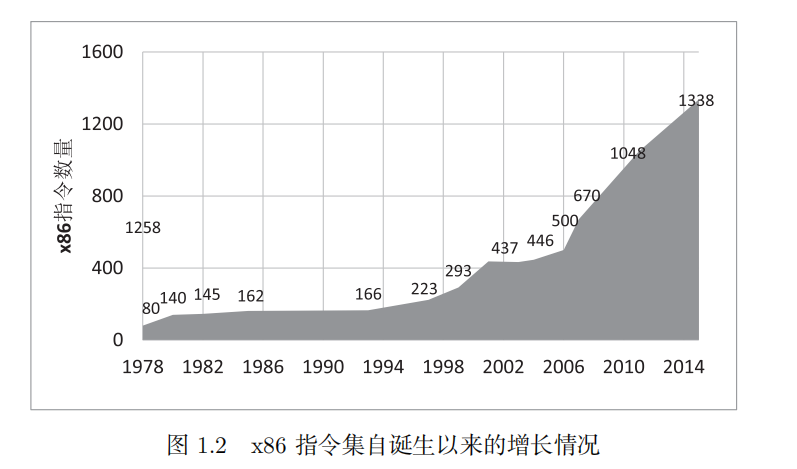

計算機體系結構的傳統發展方式是增量型 ISA,這意味著新處理器不僅需要實現新的 ISA 擴展,還必須實現過去的所有擴展。其目的是保持向過去的二進制兼容性,使數十年前的二進制程序仍可在最新處理器上正確運行。出于市場營銷的目的,新一代處理器的發布通常伴隨著新指令的發布。這兩點需求共同導致 ISA 的指令數量隨時間流逝而大幅增長。圖 1.2 展示了當今主流 ISA x86 的指令數量增長過程。x86 的歷史可追溯到 1978 年,在漫長的生命周期中,它每個月大約增加 3 條指令。

x86 在 1978 年誕生時有 80 條指令,2015 年增長到 1 338 條,翻了 16 倍,并且仍在增長。但圖中數據仍偏保守。一篇 2015 年的 Intel 博客指出,統計結果為 3600條指令 (Rodgers et al. 2017)。按這個數據,在 1978 年到 2015 年期間,x86 指令平均每 4 天增長 1 條。我們統計的是匯編語言指令,他們統計的也許是機器語言指令。增長的主要原因是 x86 ISA 通過 SIMD 指令實現數據級并行。

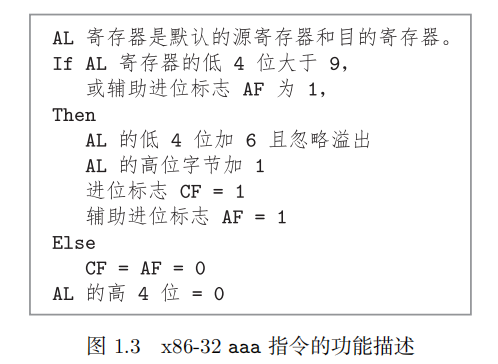

這種約定意味著 x86-32(我們用它表示 32 位地址版本的x86)的每款處理器都必須實現過去擴展的錯誤設計,即便它們已無意義。例如,圖 1.3 列出了 x86 的 aaa(ASCII Adjustafter Addition)指令,該指令早已失去用處。

它以二進制編碼十進制數(Binary Coded Decimal,BCD)的形式進行算術運算,但它已化為信息技術的歷史塵埃。x86 還有 3 條類似的指令,分別用于減法(aas)、乘法(aam)和除法(aad)。它們都是單字節指令,因此一共占用寶貴操作碼空間的 1.6%(4/256)。

打個比方,假設一家餐館只提供價格固定的套餐,最開始只有漢堡加奶昔的小餐。隨著時間的推移,套餐中加入了薯條,然后是冰淇淋圣代,還有沙拉、餡餅、葡萄酒、素食意大利面、牛排、啤酒,無窮無盡,最后變成饕餮盛宴。食客能在這家餐館找到他們過去吃過的任何一種食物(盡管這樣沒什么意義)。然而,這對食客來說是一個壞消息,他們每次的餐費將隨盛宴加量而不斷上漲。

除年輕和開放之外,RISC-V 還是模塊化的,這與過去幾乎所有 ISA 都不同。其核心是一個名為 RV32I 的基礎 ISA,可運行完整的軟件棧。RV32I 已凍結,永不改變,這為編譯器開發者、操作系統開發者和匯編語言程序員提供了穩定的指令目標。模塊化特性源于可選的標準擴展,硬件可根據應用程序的需求決定是否包含它們。利用這種模塊化特性能設計出面積小、能耗低的 RISC-V 處理器,這對于嵌入式應用至關重要。RISC-V 編譯器得知當前硬件包含哪些擴展后,便可為該硬件生成最優代碼。一般約定將擴展對應的字母加到指令集名稱之后,以指示包含哪些擴展。例如,RV32IMFD 在必選基礎指令集(RV32I)上添加了乘法(RV32M)、單精度浮點(RV32F)和雙精度浮點(RV32D)擴展。如果軟件使用了一條未實現的可選 RISC-V 擴展指令,硬件將發生自陷,并在軟件層執行該指令的功能。此特性屬于標準庫的一部分。

繼續用我們剛才的比方,RISC-V 提供的是一份菜單,而不是一頓應有盡有的自助餐。主廚只需烹飪食客需要的食物,而不是每次都烹飪一頓大餐,食客也只需為他們點單的食物付費。RISC-V 無須僅為市場營銷的熱鬧而添加新指令。RISC-V國際基金會決定何時往菜單中添加新的選擇,經過由軟硬件專家組成的委員會公開討論后,他們才會出于必要的技術原因添加指令。即使這些新的選擇出現在菜單上,它們仍是可選的,不像增量型 ISA 那樣成為未來所有實現的必要組成部分。

審核編輯:黃飛

-

處理器

+關注

關注

68文章

19890瀏覽量

235118 -

FPGA

+關注

關注

1645文章

22046瀏覽量

618277 -

加速器

+關注

關注

2文章

827瀏覽量

39112 -

微處理器

+關注

關注

11文章

2383瀏覽量

84163 -

RISC-V

+關注

關注

46文章

2563瀏覽量

48794

原文標題:圖靈獎得主David Patterson:為什么要有 RISC-V

文章出處:【微信號:pzh_mcu,微信公眾號:痞子衡嵌入式】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RISC-V和ARM有何區別?

FPGA與RISC-V淺談

芯來科技亮相RISC-V Day Tokyo 2025

SOPHGO RISC-V SoC Linux Kernel 社區郵件列表建立,歡迎加入開源社區為RISC-V生態完善添磚加瓦

關于RISC-V芯片的應用學習總結

RISC-V近期市場情況調研

RISC-V的理論與實踐探討

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

RISC-V為何備受歡迎?

RISC-V為何備受歡迎?

評論