什么是幀緩存(frmbuf)

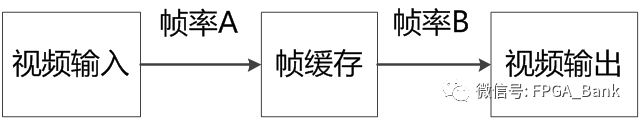

在視頻處理系統中,將輸入的圖像以幀為單位儲存到存儲器(DDR)中,再根據輸出時序需求,讀取圖像并輸出,達到幀率變換、暫停顯示的目的。

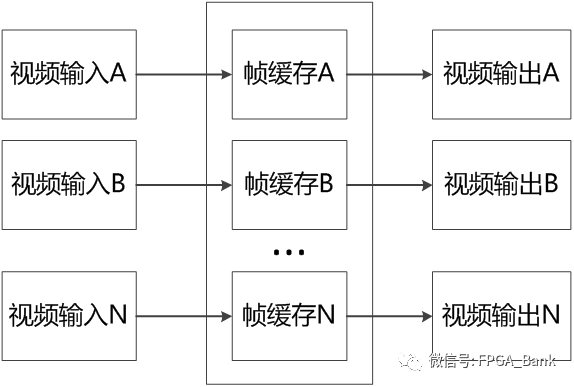

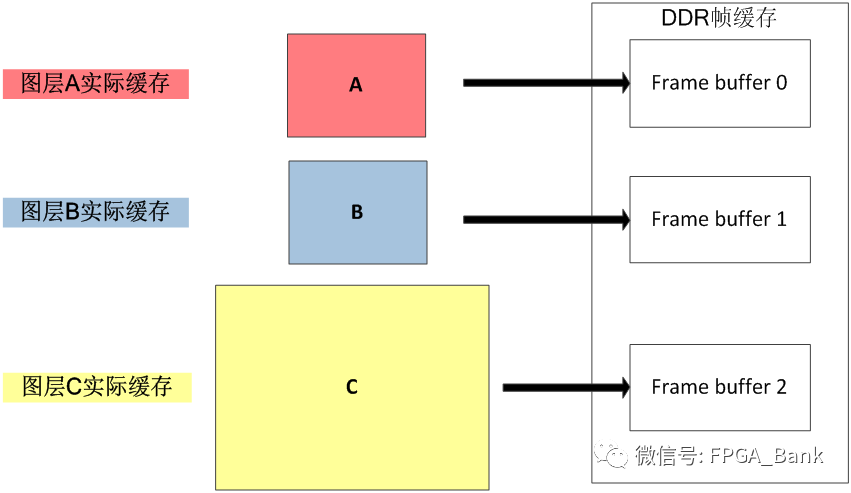

在大部分應用中,視頻輸入輸出的數量通常都不止一組,也就是需要多個幀緩存進行視頻的存儲;

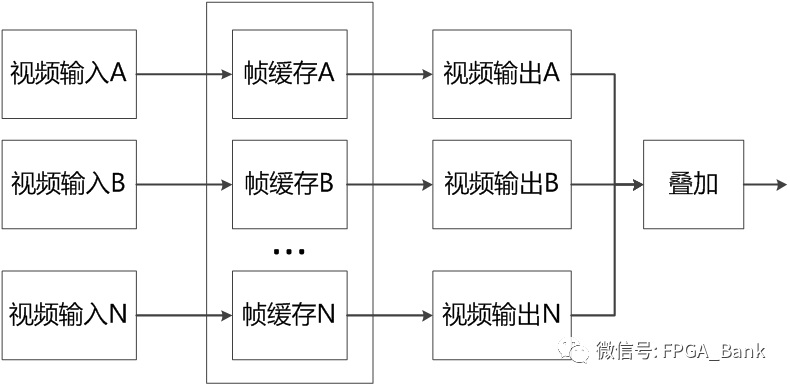

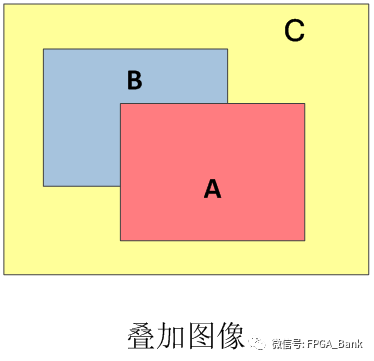

如果一個系統中存在多路視頻輸入,而只有一路視頻輸出,那么通常在幀緩存后還要將多路視頻疊加在一起才可以進行輸出;

常用的幀緩存設計

在常規的視頻處理平臺中,為了實現多路視頻的任意疊加,會將輸入到系統中的所有視頻都緩存到DDR中,進行疊加時,將所有圖層的完整視頻從DDR讀出,再根據層疊關系進行疊加;

優點:

操作簡單

更改疊加位置時可以立刻響應

可拓展透明疊加功能

缺點:

每一個圖層都緩存完整的視頻,占用的DDR帶寬較大,尤其 是在多圖層系統中。

以FPGA實現存儲4K@60輸入,4K@60輸出的視頻為例:RGB444 24BIT像素

寫有效帶寬:3840*2160*24*60大約為12Gbit

讀有效帶寬:3840*2160*24*60大約為12Gbit

總的需要占用DDR帶寬為24Gbit。

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21966瀏覽量

614136 -

存儲器

+關注

關注

38文章

7636瀏覽量

166417 -

DDR

+關注

關注

11文章

731瀏覽量

66395 -

RGB

+關注

關注

4文章

803瀏覽量

59593

原文標題:在FPGA上關于DDR的幀緩存介紹

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA的幀同步系統設計方案

基于FPGA與的VHDL語言驅動時序發生器與數據緩存器的一體化設計

LOTO示波器軟件PC緩存(波形錄制與回放)功能

視頻相鄰幀相減,怎么解決圖片緩存問題

【AC620 FPGA試用申請】以太網傳圖幀緩存設計

【AC620 FPGA試用體驗】+以太網傳圖幀緩存系統設計 附工程源碼(結項)

FPGA的圖像緩存部分電路是怎么寫的

幀差法FPGA實現原理

關于內存可緩存性的疑問怎么解釋

如何完成基于FPGA技術的驅動時序發生器與數據緩存器的一體化設計?

幀同步系統的FPGA設計

基于FPGA的高速圖形幀存設計

簡述OpenGL幀緩沖區多線(FBO)基本概念

LOTO示波器軟件PC緩存(波形錄制與回放)功能

什么是幀緩存?在FPGA上關于DDR的幀緩存介紹

什么是幀緩存?在FPGA上關于DDR的幀緩存介紹

評論