Standard cell,標準單元,或者簡稱cell,可以說是數字芯片后端最基本的概念之一了,甚至可能沒有接觸過后端的同學也有所耳聞?

那么,它到底是什么呢?我們為何要設定標準單元呢,以及這些cell是怎么應用到我們的后端設計中的呢?我就來以我個人的理解闡述一下這幾個問題。

首先,在芯片設計最早期,門電路不多,晶體管都靠手畫在圖紙上,所有芯片都是一些邏輯簡單的全定制芯片的時代,是不存在什么標準單元的概念的。那時的工程師們只需要把一個一個的晶體管擺好,電路就可以正常工作了。

但是隨著集成化越來越高,所有的門電路都靠一個個手畫變得非常不現實,一個非常樸素的想法就是把一些用過很多次的電路打包,就比如最基本的與或非門,我們要用的時候直接調用這個包就行了,就像復制粘貼一樣,這就非常方便了。

比如一個二輸入與門,我只要設計好它的電路,畫出它的版圖,提取出來它的各項參數,就可以無限次的在整個芯片上復制了。

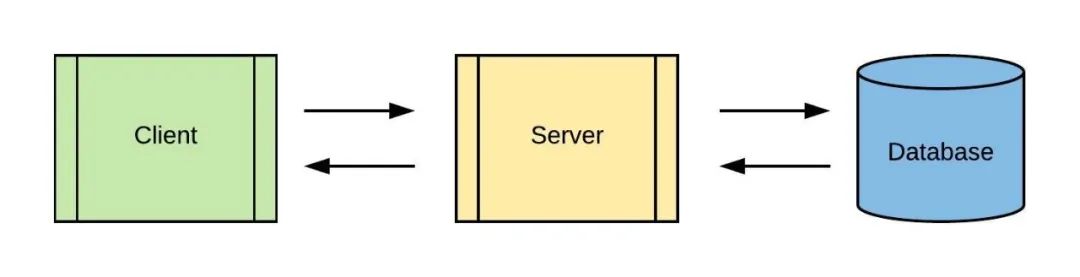

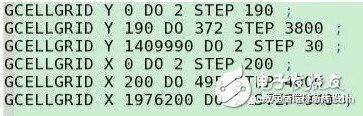

而后,更進一步,我們可以把整個芯片所有可重用的部分都打包起來,為了方便我們擺放和連線,我們會制定一些規范化的rule,比如我們規定每個包要有固定的高度,稱為row,寬度可以以一個CPP(柵極間距)的距離變化,稱為site。這樣就成為了一個std cell。

Std cell可以大大簡化我們的設計復雜度,它的意義,就像蓋樓房的磚頭,構成生物的細胞,畫畫的顏料一樣。

如果對于任何一個邏輯門都要求后端從頭晶體管開始設計,那是真的無法想象的。目前所有的芯片已經全部采用了這種設計方式。

但是,不可避免地,它會有一些資源的浪費,因為每一個cell都是有統一的設計規則,必然不能針對性的在一些小的方面進行優化。

舉個例子,在芯片的某個地方可以把pin出在cell左側比較好route,但是這種cell設計的都是在右側。當然,類似這樣的影響在大型design中可以忽略了。

設計std cell是一件非常復雜的事,我感覺不亞于設計一款芯片的復雜程度。首先是電路的設計,schematic design。有一些具有相對復雜邏輯功能的cell,它的邏輯電路如何設計,如何兼顧PPA地進行設計,其實是很難的,設計結束后還要進行許多的驗證之類。而后layout工程師要設計畫出cell的版圖。

我們后端設計一般繞線層十幾層頂天了,版圖工程師要面對的是數不清的各種各樣的層,有metal,有oxide,有poly,有n區有p區,應有盡有,還要考慮盡可能出pin M1或者M2出,低一點,給我們APR預留更多的繞線資源。

而后還要有專門的工程師來進行cell 參數的提取,一般就是指power和timing的提取。Power應該主要就是leakage,timing就很麻煩了,需要在各個corner下,每個corner出一套它的各項參數。

舉個例子,一個cell的delay信息,基本需要在各個PVT條件下,測出各個引腳在各種邏輯狀態下,input transition和output load各種情形下,cell的delay值。

更別提一些OCV的信息,還有POCV的lvf信息了。最終所有這一切做好后,就可以生成cell的LIB文件了。結合cell的LEF文件(物理信息),我們后端就可以愉快的用這些cell搭積木啦。

我們后端在用的時候,這些cell就是一個一個的黑匣子,看不見內部,只能看到它的大小和出pin的信息。讀入網表文件后,相應的cell就出現在我們的GUI界面了。對了,前端在綜合的時候也需要讀cell的lib。

他們拿到的RTL代碼不會指定一個與門要用哪種cell,比如我們目前有兩種不同的與門cell,邏輯功能一樣,但是有一些別的差異,綜合工具就會全面考慮這一塊電路,選用相應的cell作為那一段verilog代碼里表示的與門。先寫這么多吧,文中提到的各種名詞之后我可能都會寫一寫,希望對大家有所幫助。

-

晶體管

+關注

關注

77文章

9975瀏覽量

140567 -

門電路

+關注

關注

7文章

200瀏覽量

40582 -

RTL

+關注

關注

1文章

388瀏覽量

60622 -

數字芯片

+關注

關注

1文章

111瀏覽量

18703 -

Layout設計

+關注

關注

1文章

14瀏覽量

1675

發布評論請先 登錄

求一份tsmc 7nm standard cell library

ESP32能應用到治具中嗎

AR工業應用|AR應用到工業場景到底是什么樣的效果呢?可用于AR巡檢AR電力AR遠程協助|effiar分享

人臉識別技術如何應用到汽車領域

IP 數據表: 1.8V Standard Cell for TSMC 28nm HPC+

IP 數據表: 3.0V Standard Cell for TSMC 40nm LP

IP 數據表: 1.8V Standard Cell for TSMC 28nm HPC+

IP 數據表: 3.0V Standard Cell for TSMC 40nm LP

如何將Kafka使用到我們的后端設計中

Standard cell是怎么應用到我們的后端設計中的呢?

Standard cell是怎么應用到我們的后端設計中的呢?

評論