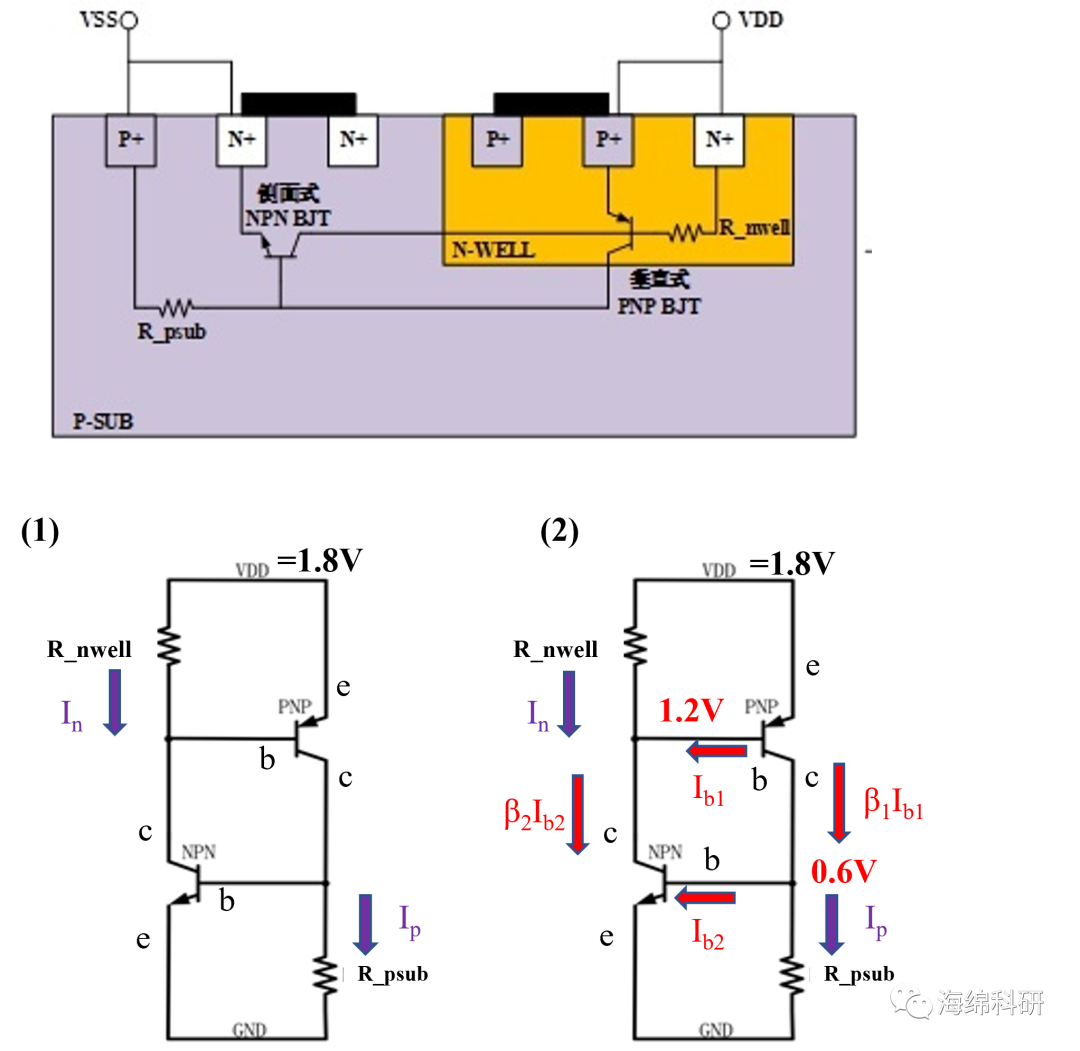

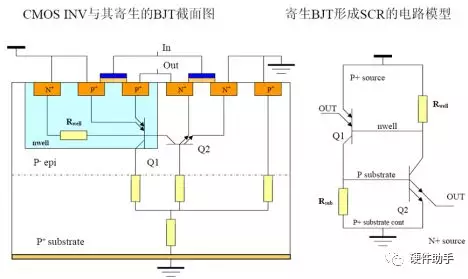

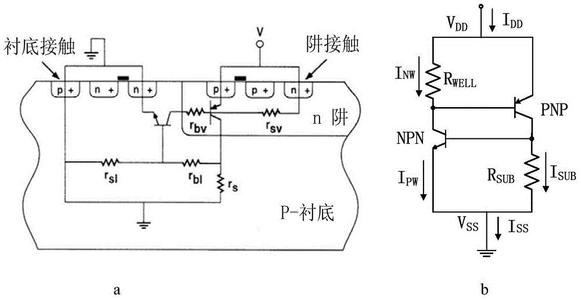

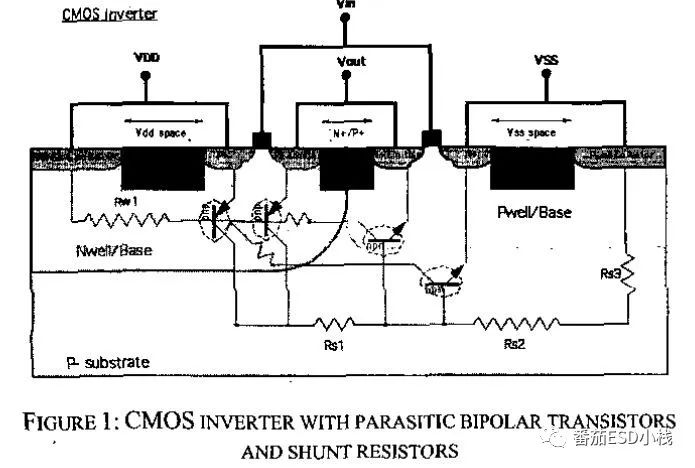

一、閂鎖效應(yīng):實(shí)際上是由于CMOS電路中基極和集電極相互連接的兩個(gè)BJT管子(下圖中,側(cè)面式NPN和垂直式PNP)的回路放大作用形成的,在兩個(gè)管子的電流放大系數(shù)均大于1時(shí),電流在這兩個(gè)管子構(gòu)成的回路中不停地被放大,從而導(dǎo)致管子承受的電流過大而燒毀芯片的一種現(xiàn)象。

二、閂鎖效應(yīng)的原理分析:

狀態(tài)一:假設(shè)在N阱或者Psub中由于外界的原因產(chǎn)生了載流子注入,電流分別為In和Ip, 且InR_nwell=0.6,IpR_psub=0.6(假設(shè)PN結(jié)的導(dǎo)通電壓<0.6)。

狀態(tài)二:在所設(shè)壓降下,PNP的基極電位為1.2V, 集電極電位為0.6V, NPN的基極電位為0.6V, 集電極電位為1.2V,此時(shí)PNP和NPN的發(fā)射結(jié)都正偏, 集電結(jié)都反偏。從而兩個(gè)BJT管子可進(jìn)行電流放大,PNP產(chǎn)生了基極電流Ib1, 則集電極電流IC1=β1Ib1, NPN產(chǎn)生了基極電流Ib2, 則集電極電流IC2=β2Ib2。

在近似狀態(tài)下,Ib1=β2Ib2,Ib2=β1Ib1,因此在后面的循環(huán)中,NPN的集電極電流作為PNP新的基極電流進(jìn)行電流放大,PNP的集電極電流作為NPN新的基極電流進(jìn)行放大。多次循環(huán)之后,電流會(huì)被持續(xù)放大。

三、閂鎖效應(yīng)的抑制方法(部分方法):

1.拉開NMOS和PMOS的間距:破壞電流循環(huán)中的一環(huán),使側(cè)面式NPN BJT管子的基區(qū)變厚,載流子的收集變的困難,很難進(jìn)行電流的放大。

2.使用Guard ring,襯底電位接出的部分采用環(huán)形繞線: 降低VDD和Vss的導(dǎo)通電阻,也即降低Rwell和Rsub的阻值,防止BJT的基極和集電極電位相等,破壞BJT導(dǎo)通的條件。

3.Substrate contact和well contact應(yīng)盡量靠近source: 縮短了Rwell和Rsub的電阻的長(zhǎng)度,減小了其電阻值。

-

CMOS電路

+關(guān)注

關(guān)注

0文章

49瀏覽量

11759 -

VDD

+關(guān)注

關(guān)注

1文章

316瀏覽量

34774 -

閂鎖效應(yīng)

+關(guān)注

關(guān)注

1文章

33瀏覽量

9493 -

PNP管

+關(guān)注

關(guān)注

1文章

28瀏覽量

7824 -

基極電流

+關(guān)注

關(guān)注

1文章

32瀏覽量

3362

發(fā)布評(píng)論請(qǐng)先 登錄

CMOS的閂鎖效應(yīng):Latch up的原理分析

芯片設(shè)計(jì)都不可避免的考慮要素—閂鎖效應(yīng)latch up

閂鎖效應(yīng)的工作原理

什么是閂鎖效應(yīng)?

寄生電路的效應(yīng):Latch-Up(鎖定)

靜電放電/過度電性應(yīng)力/閂鎖試驗(yàn) (ESD/EOS/Latch-up)

ESD/Latch-Up Considerations wi

Latch-Up White Paper

Latch-Up白皮書

USB Type-C應(yīng)用中選錯(cuò)TVS造成的高度Latch-up風(fēng)險(xiǎn)

IC工藝和版圖設(shè)計(jì)第八章Latch-up和GuardRing設(shè)計(jì)

避免電路中閂鎖效應(yīng)的3個(gè)實(shí)用方法!

淺談Latch-up(一)

淺談Latch-up(二)

芯片失效機(jī)理之閂鎖效應(yīng)

閂鎖效應(yīng)(Latch-up)原理及其抑制方法解析

閂鎖效應(yīng)(Latch-up)原理及其抑制方法解析

評(píng)論