二.Latch-up測(cè)試流程。

目前通用的Latch-up測(cè)試標(biāo)準(zhǔn)是 JESD78E 。該標(biāo)準(zhǔn)中將Latch-up測(cè)試分為兩種: 1.電流測(cè)試 I-test ,用于測(cè)試非電源管腳;2.電壓測(cè)試 V-test 用于測(cè)試電源管腳。其中I-test又有正向注入/負(fù)向抽取兩種,正向注入電流會(huì)使得端口電壓升高,負(fù)向抽取電流會(huì)使得端口電壓降低。

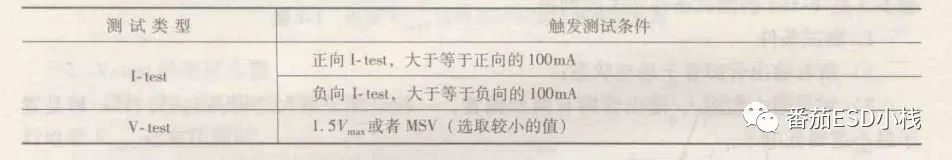

表一.測(cè)試閂鎖效應(yīng)的分類(lèi)。(圖源《CMOS集成電路閂鎖效應(yīng)》)

表一為L(zhǎng)atch-up的測(cè)試條件,其中MSV表示(Maximum Stress Voltage)最大允許工作電壓。

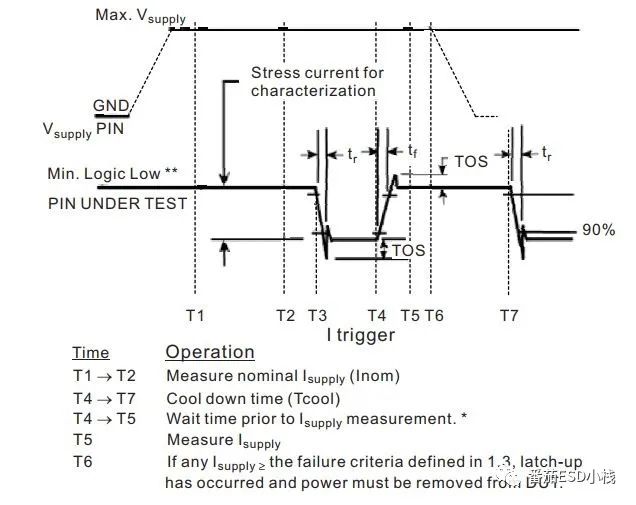

2.1 V-test的測(cè)試流程

- 對(duì)所有的輸出引腳懸空,輸入引腳置于高電平偏置,測(cè)量VDD到GND的漏電流In。

- 對(duì)待測(cè)管腳施加V-test源。

- 去除觸發(fā)源后將被測(cè)管腳復(fù)原,測(cè)量漏電流Isupply,進(jìn)行失效判斷。(如果In<25mA,失效標(biāo)準(zhǔn)為In+25mA,如果In>25mA,失效標(biāo)準(zhǔn)為>1.4*In)

- 如果沒(méi)有發(fā)生Latch-up,將所有輸入管腳,都置于低電平偏置,重復(fù)實(shí)驗(yàn)。

- 重復(fù)2,3,直到每個(gè)電源Vsupply管腳(或管腳組合)都通過(guò)測(cè)試。

圖一.V-test激勵(lì)波形。

V-test測(cè)試模擬的是電源浪涌是否會(huì)造成PN結(jié)擊穿,形成雪崩擊穿電流,從而造成寄生SCR的開(kāi)啟。

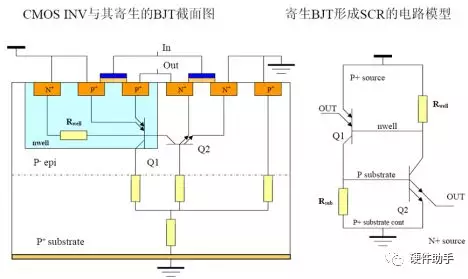

2.2 I-test的測(cè)試流程

- 不接受測(cè)試的輸出管腳懸空。對(duì)于輸入管腳,偏置于最大邏輯高電平。電源管腳置于最大工作電壓。

- 測(cè)量VDD到GND的漏電流In。

- 對(duì)待測(cè)管腳施加I-test源。

- 去除觸發(fā)源后,將被測(cè)管腳恢復(fù)到施加觸發(fā)源之前的狀態(tài),并測(cè)量每個(gè)電源管腳的漏電流Isupply,進(jìn)行失效判斷。(如果In<25mA,失效標(biāo)準(zhǔn)為In+25mA,如果In>25mA,失效標(biāo)準(zhǔn)為>1.4*In)

- 如果沒(méi)有發(fā)生Latch-up,對(duì)所有待測(cè)管腳,重復(fù)實(shí)驗(yàn)。

- 將非待測(cè)管腳置于懸空態(tài)。將輸入管腳置于最小邏輯低電平。電源管腳置于最大工作電壓。重復(fù)上述實(shí)驗(yàn)。

圖二.I-test正向激勵(lì)波形。

圖三.I-test負(fù)向激勵(lì)波形。

I-test測(cè)試模擬浪涌電壓出現(xiàn)在非電源管腳,浪涌電壓高于VDD或低于GND。該電路中寄生SCR能否開(kāi)啟。

2.3 無(wú)源器件相連的特殊管腳

這類(lèi)管腳都只進(jìn)行I-test,具體情況請(qǐng)參照《CMOS集成電路閂鎖效應(yīng)》。

2.4 特殊功能管腳

某些芯片會(huì)具有特殊的功能管腳,例如LDO,PWM,BOOT,PHASE,HB,VCC等,這些芯片的管腳能為其他芯片或器件提供偏置。而針對(duì)這類(lèi)管腳,使用I-test還是V-test需要根據(jù)情況確定。

2.5 多電壓域芯片

BCD工藝或者BiCMOS工藝能實(shí)現(xiàn)高壓-低壓多工作電壓芯片,而這種芯片因?yàn)楣ぷ麟妷翰煌琕-test激勵(lì)值不能統(tǒng)一按1.5*Vmax算。

圖四.多電壓域Latch-up測(cè)試。(實(shí)例取自德儀Latch-up白皮書(shū))

如圖所示,該芯片存在5V,12V,60V多個(gè)VDD。針對(duì)該芯片的V-test需要不同的激勵(lì), VDD 5V需要1.5Vmax或MSV;VDD 12V需要1.2Vmax或MSV;VDD 60V需要1.1Vmax或MSV 。

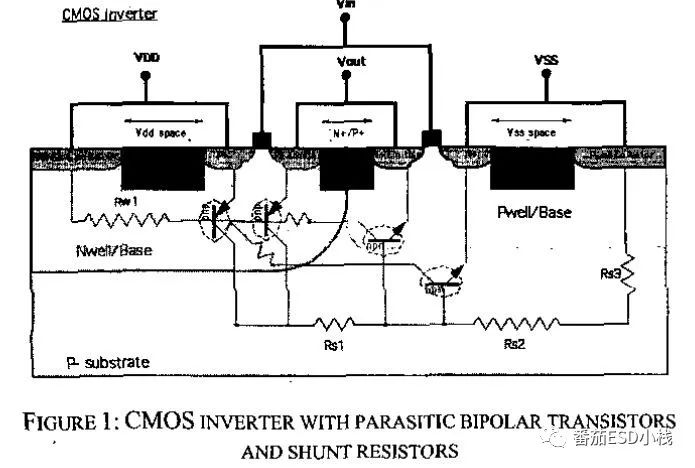

三.Latch-up防護(hù)設(shè)計(jì)。

Latch-up防護(hù)的核心就是預(yù)防電路中寄生SCR的開(kāi)啟。而圍繞這一目標(biāo)具體有兩個(gè)實(shí)現(xiàn)方向:

一.減少阱電阻Rn和Rp,降低寄生三極管的基級(jí)電壓。

具體的版圖設(shè)計(jì)規(guī)則:

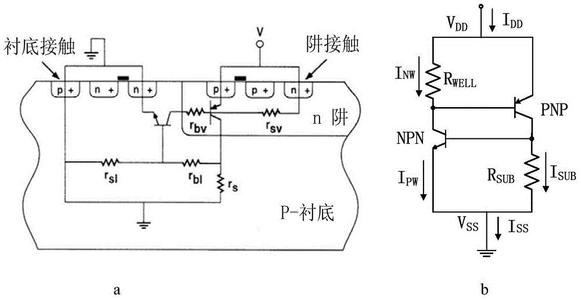

1.減少Bulk與Soure/Drain端的間距,減少N-WeLL/P-WeLL的阱電阻。

增大阱接觸區(qū)的面積和接觸孔數(shù)量,因?yàn)橼褰佑|區(qū)是高摻雜濃度的有源區(qū),能大幅度改善阱電流分布,降低阱電阻。

2.使用環(huán)狀阱接觸有源區(qū)。環(huán)狀設(shè)計(jì)能確保有源區(qū)與接觸孔分布均勻,避免電流集中流向某一區(qū)域造成的局部電壓過(guò)高。

二.減少βn和βp,降低寄生三極管的放大倍數(shù),削弱寄生三極管的正反饋耦合作用。

具體的版圖設(shè)計(jì)規(guī)則:

1.增大NMOS/PMOS有源區(qū)與N-WeLL/P-WeLL的距離。通過(guò)增加間距,拉寬寄生三極管的基區(qū)寬度,減小其放大倍數(shù)。

2.增加額外保護(hù)環(huán)。保護(hù)環(huán)能為寄生三極管增加額外的集電極/射電極,而新添加的寄生三極管,(NPN:NMOS_Drain/P_Sub/N_Guard)與(PNP:PMOS_Drain/N_WeLL/P_Guard)更易觸發(fā),且不存在相互耦合作用。換句話說(shuō)起到了對(duì)外部注入載流子的收集作用。

圖五.CMOS保護(hù)環(huán)示意圖。

3.IO電路與核心電路的隔離,IO電路所承受的風(fēng)險(xiǎn)遠(yuǎn)高于內(nèi)部電路。所以IO單元最好與內(nèi)部電路間隔一段距離,確保ESD/Latch-up/EOS等不會(huì)引起內(nèi)部核心電路的損壞。

其實(shí)Latch-up的防護(hù)相對(duì)于ESD來(lái)說(shuō)較為簡(jiǎn)單, 只要版圖工程師注意間距與保護(hù)環(huán)的問(wèn)題,絕大多數(shù)Latch-up失效都能避免(目前大部分工藝都已經(jīng)把latch-up rule 寫(xiě)入 DRC中,只要按圖索驥即可) 。但是模擬IC要面臨的Latch-up的情況更加復(fù)雜,所以這里介紹些 非常規(guī)設(shè)計(jì)方案 。

1.利用工藝優(yōu)勢(shì),Epi(外延層工藝);DTI(深槽隔離);SOI(絕緣體上硅);NBL埋層,這些工藝都能有效改善Latch-up問(wèn)題。

2.利用Deep N-WeLL 進(jìn)行隔離,深N阱的隔離作用更加有效,也能有效緩解Latch-up。

3.浮阱設(shè)計(jì)(一種特殊設(shè)計(jì),會(huì)造成閾值電壓和漏電流浮動(dòng),主要應(yīng)用在ESD與Latch-up,以后會(huì)講案例)

4.輸出級(jí)在端口掛載電阻,I-test時(shí)能分擔(dān)部分壓降,但是會(huì)降低輸出級(jí)的負(fù)載能力。

-

三極管

+關(guān)注

關(guān)注

145文章

3651瀏覽量

123855 -

SCR

+關(guān)注

關(guān)注

2文章

151瀏覽量

44757 -

VDD

+關(guān)注

關(guān)注

1文章

316瀏覽量

34731 -

電源浪涌

+關(guān)注

關(guān)注

0文章

12瀏覽量

5942 -

PMOS管

+關(guān)注

關(guān)注

0文章

84瀏覽量

6981

發(fā)布評(píng)論請(qǐng)先 登錄

CMOS的閂鎖效應(yīng):Latch up的原理分析

芯片設(shè)計(jì)都不可避免的考慮要素—閂鎖效應(yīng)latch up

Latch UP

寄生電路的效應(yīng):Latch-Up(鎖定)

靜電放電/過(guò)度電性應(yīng)力/閂鎖試驗(yàn) (ESD/EOS/Latch-up)

LIS3DH加速度計(jì)自我測(cè)試失敗

TC1413/TC1413N pdf datasheet

ESD/Latch-Up Considerations wi

Latch-Up White Paper

Latch-Up白皮書(shū)

高壓閉鎖雙SPST開(kāi)關(guān)的adg5421/adg5423數(shù)據(jù)表

ADG5401:高伏特式Latch up,單片機(jī)SPST交換機(jī)

USB Type-C應(yīng)用中選錯(cuò)TVS造成的高度Latch-up風(fēng)險(xiǎn)

IC工藝和版圖設(shè)計(jì)第八章Latch-up和GuardRing設(shè)計(jì)

淺談Latch-up(一)

淺談Latch-up(二)

淺談Latch-up(二)

評(píng)論