圍繞 3D異構(gòu)集成(3DHI:heterogeneous integration )的活動正在升溫,原因是政府的支持不斷增加、需要向系統(tǒng)中添加更多功能和計算元素,以及人們普遍認(rèn)識到,除了將所有內(nèi)容都封裝到單個 SoC 中之外,還有更好的前進(jìn)道路。相同的進(jìn)程節(jié)點(diǎn)。

在過去的幾年里,芯片設(shè)計的前沿發(fā)生了巨大的變化。國際競爭正在推動對在岸上或友好地點(diǎn)設(shè)計、制造和封裝的更先進(jìn)芯片的投資。DARPA 微系統(tǒng)技術(shù)辦公室剛剛宣布了其下一代微電子制造 ( NGMM ) 計劃,旨在通過建立國內(nèi)開放式原型設(shè)計和試驗(yàn)線中心來推進(jìn)最先進(jìn)的 3DHI 微電子技術(shù),該中心可供美國用戶使用學(xué)術(shù)界、政府和工業(yè)界。熟悉該計劃的人士表示,它正在刺激整個半導(dǎo)體生態(tài)系統(tǒng)建立新的合作伙伴關(guān)系。

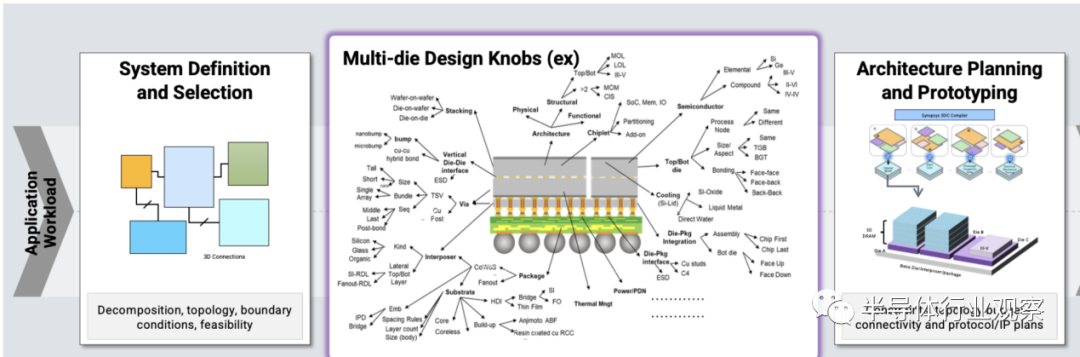

這只是最終將影響整個芯片行業(yè)的復(fù)雜、多層次轉(zhuǎn)變的一個方面。全球的設(shè)計團(tuán)隊(duì)才剛剛開始理解半導(dǎo)體設(shè)計的新未來,這需要深入了解 3D 異構(gòu)設(shè)計中的權(quán)衡和不斷增加的可用選項(xiàng)。

“您嘗試進(jìn)入 3DHI 的原因是因?yàn)槟幸恍?PPA 目標(biāo),或者說您想要擁有的成本優(yōu)勢,”Synopsys 產(chǎn)品管理高級總監(jiān) Shekhar Kapoor說道。“重點(diǎn)是什么是最優(yōu)化的設(shè)計。它從前面開始。說“我要分解”很容易。但你如何決定呢?如果這樣做,整個 IC 設(shè)計范式很快就會轉(zhuǎn)變?yōu)橄到y(tǒng)設(shè)計范式。在這個層面上,通過軟件/硬件設(shè)計,您將處理哪些工作負(fù)載?您需要什么小芯片?那里沒有小芯片的市場。即使您使用從其他地方可用的子系統(tǒng),它如何適合您所考慮的總體范圍?”

成本仍然是每個人最關(guān)心的問題,但在系統(tǒng)環(huán)境中存在更大的靈活性。“成本始終很重要,” Cadence定制 IC 和 PCB 部門產(chǎn)品管理小組總監(jiān) John Park 說道。“但在過去,封裝的目的就是成本最低。人們現(xiàn)在愿意為封裝多付一點(diǎn)錢,尤其是大批量的產(chǎn)品。”

3DHI 還為外形尺寸的更大靈活性打開了大門,這反過來又可以對整體設(shè)計產(chǎn)生重大影響。

“例如,如果您要將某些東西放入智能手機(jī)中,則需要更薄、更輕的外形,”Park 指出。“如果它是放在架子上的東西,也許你不需要相同類型的配置文件。如果存在內(nèi)存帶寬問題,您必須找出最佳內(nèi)存以及將其組合在一起的最佳 DRAM 策略。有很多不同的選擇,包裝仍然是狂野的西部。有些人會認(rèn)為包裝的選擇太多,但產(chǎn)品有很多不同。如果你要在衛(wèi)星中放置一些東西,那么它必須非常堅固,并且必須能夠持續(xù) 50 年并且更加可靠。這取決于你正在設(shè)計什么,你的最終產(chǎn)品是什么,然后通常會得出成本,以及外形尺寸、尺寸、重量和功率,以及隨之而來的所有其他因素。”

西門子 EDA產(chǎn)品營銷經(jīng)理 Keith Felton將其分為兩個領(lǐng)域。“首先是設(shè)備之間的機(jī)械集成,”他說。“它們會與基板、封裝或其他芯片/小芯片連接嗎?是否需要微凸塊,還是需要直接或混合鍵合?封裝平臺技術(shù)將決定其中的一些,就像您互連的芯片/小芯片一樣。”

第二個領(lǐng)域是通信協(xié)議——UCIe、BoW、AIB 等。“如果涉及 HBM,您將需要一個硅中介層或橋作為 PHY 之間的機(jī)械接口,這將部分決定機(jī)械集成技術(shù),”Felton說。“如果您的架構(gòu)需要直接芯片到芯片集成(晶圓上芯片或晶圓上晶圓),那么很可能需要直接或混合鍵合。集成將影響芯片/小芯片的設(shè)計和引腳輸出,因此使用支持參數(shù)化、自生成引腳區(qū)域的設(shè)計工具可以讓設(shè)計人員/架構(gòu)師以最小的努力或成本探索多種集成場景。”

架構(gòu)選擇很重要

與過去不同的是,許多設(shè)計決策都是連續(xù)且孤立的,3DHI 需要更廣泛地了解所有部分如何組合在一起。設(shè)計工程師必須成為系統(tǒng)工程師,他們必須處理各種需要與具有不同專業(yè)知識的工程師合作的問題,例如機(jī)械工程或軟件專業(yè)知識。

“如果你把它分解成太多的小部分,不僅封裝的集成真的很難做到,而且這些互連也會帶來開銷——額外的功率開銷,以及增加的一點(diǎn)延遲,”是德科技高速數(shù)字仿真技術(shù)產(chǎn)品經(jīng)理 Stephen Slater說。“你必須根據(jù)重要的功能來挑選它。”

Slater指出,開發(fā)大型 ASIC 的芯片制造商知道自己的良率是多少,也知道自己的目標(biāo)是什么。改變的是,他們現(xiàn)在必須弄清楚要分解哪些部分,以及他們愿意犧牲哪些部分來增加額外的 PHY 和復(fù)雜的高級封裝所需的功率。

“(行業(yè))清楚的一件事是,沒有其他出路,”他說。“確實(shí)只有這個辦法了。已經(jīng)有人在向墻壁開槍了。它們已經(jīng)達(dá)到了巨大的標(biāo)線尺寸。他們不能做得更大。這就是前進(jìn)的方向。對于其他人來說,轉(zhuǎn)折點(diǎn)將是在他們未來的 ASIC 中,他們擔(dān)心收益率會是多少。從那時起他們就開始考慮分手。”

但 3DHI 增加了一個全新的復(fù)雜性軸。數(shù)據(jù)將如何流經(jīng)該系統(tǒng)(該系統(tǒng)可能是使用不同工藝技術(shù)開發(fā)的 2D 和 3D 元素的組合)?還有很多事情會出錯,從機(jī)械問題到片上網(wǎng)絡(luò)死鎖(deadlocks)。

Arteris產(chǎn)品管理和戰(zhàn)略營銷高級總監(jiān) Guillaume Boillet 表示:“這些死鎖是可怕的小錯誤,它們會阻止數(shù)據(jù)包流動并導(dǎo)致整個系統(tǒng)停止運(yùn)行。”他指出,這些死鎖有兩種類型:拓?fù)渌梨i和協(xié)議死鎖( topology and protocol deadlocks)。“雖然拓?fù)渌梨i特征在小芯片中通常是基本的,但只需要一個端口就可以形成環(huán)。

如果兩個不同的供應(yīng)商對規(guī)范的解釋存在分歧,那么它很可能會出現(xiàn)錯誤。在協(xié)議死鎖方面,人們正在努力簡化跨小芯片的數(shù)據(jù)流的性質(zhì)。盡管如此,新生的規(guī)范仍然很復(fù)雜,基于文本,因此可以進(jìn)行解釋。正如我們過去所看到的,每次橋接協(xié)議時,都存在未涵蓋極端情況的風(fēng)險。”

在宏觀層面上,Cadence的Park 相信每個人對于 3DHI 都有或多或少相同的目標(biāo)。但確定優(yōu)先級可能很棘手。“如果你想節(jié)省成本,那么成本就成為了你的目標(biāo)。如果您希望獲得最高性能,那么性能會優(yōu)先于它。熱量開始發(fā)揮作用。如果您在服務(wù)器場中使用可以進(jìn)行液體冷卻的設(shè)備,請全力以赴地提高性能。如果你要在智能手機(jī)中放入某些東西,最好不要太熱,以免在觸摸手機(jī)時燙傷你的手。”

隨著選擇數(shù)量的增加,封裝的權(quán)衡變得更加混亂。

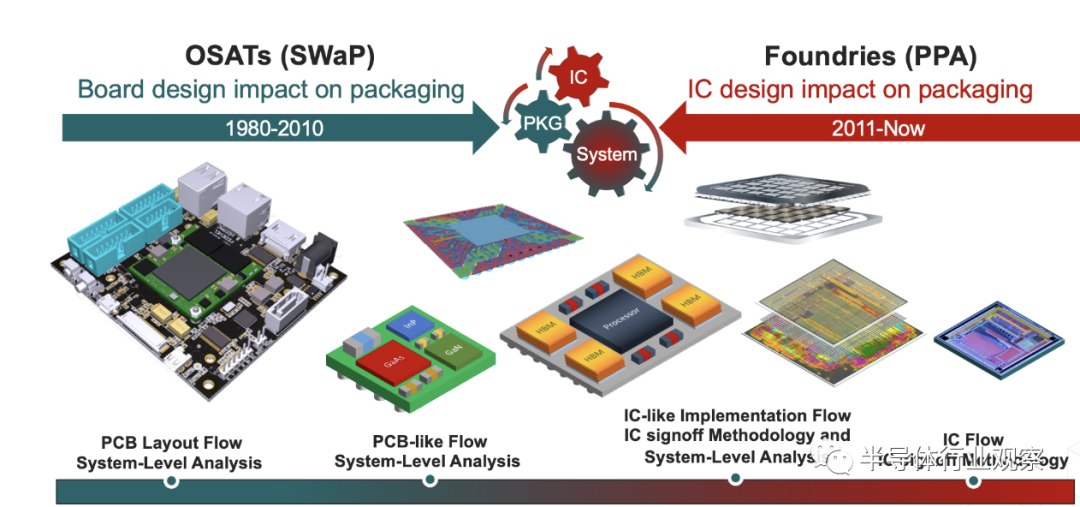

“在過去的半導(dǎo)體時代,每隔幾年我們就會得到一個新節(jié)點(diǎn),就是這樣,”Park說。“封裝在不斷發(fā)展——尤其是現(xiàn)在晶圓廠已經(jīng)進(jìn)入世界各地。因此,我們每年可能會獲得六到十幾種新的封裝技術(shù)。隨著代工廠和現(xiàn)在的 OSAT 不斷增加其封裝選項(xiàng)組合,這是一個不斷發(fā)展的事情。它曾經(jīng)是相當(dāng)有限的。它主要是基于層壓板的基板,但現(xiàn)在有了將原廠和 3D 堆疊,您就有了所有這些不同的選擇。有了中介層,我會變成玻璃嗎?我要選擇硅嗎?我應(yīng)該使用薄膜 RDL 中介層嗎?薄膜層壓板?每個封裝層都會增加成本和復(fù)雜性,具體取決于您計劃做什么。如果我今天能給你一些選擇,明天它就會改變,因?yàn)橛腥藭氤隽硪环N新方法。你有代工廠,有 OSAT,然后是這些封裝技術(shù)公司——像 Deca 這樣的公司,推出了一種新的封裝方式。”

封裝對 3DHI 系統(tǒng)中設(shè)備之間接口的技術(shù)規(guī)范有直接影響。

“如果你只是談?wù)撐锢硪_間距,如果我有超密集、高帶寬類型的設(shè)計,我通常需要使用硅類型的基板,”Park 解釋道。“這意味著如果我采用硅基板(又名高級封裝),我可以采用 45 微米或 35 微米的凸塊間距。如果我繼續(xù)使用層壓板,則間距為 125 微米。因此,封裝決定了引腳的密度,這當(dāng)然會影響其他因素,例如帶寬。”

這里發(fā)揮作用的其他考慮因素包括通信接口,它指的是 UCIe、BoW、AIB 等。

“有了這些通信接口,事情就變得一樣了,”Park 說。“UCIe 有標(biāo)準(zhǔn)封裝(間距約為 130 微米)和高級封裝(間距更像是 40 微米)。然后它會變得更加復(fù)雜,因?yàn)槟阌袠颍⑶遗c橋連接的芯片部分可以具有非常小的節(jié)距,而位于層壓板其余部分上的部分必須具有更大的節(jié)距。因此,您會看到這些多間距芯片和小芯片開始采用它們所采用的封裝技術(shù)。就是這樣確定的。對于層壓板,我們只能做到這么小,而對于硅,我們可以做得更小,這樣我們就可以將引腳放置得更近。”

探索選項(xiàng)

模擬對于理解所有這些細(xì)節(jié)至關(guān)重要。Keysight 的 Slater 指出,對于高速數(shù)字,必須徹底模擬與 UCIe 的高速互連。射頻微波也是如此。

“在射頻微波領(lǐng)域,我們看到某些公司談?wù)撋漕l小芯片的未來前景,”Slater說。“雖然這可能是以后的發(fā)展,但您在射頻微波市場中確實(shí)看到的一件事是,在一個模塊中,您有不同的芯片,不同的基板技術(shù)被組裝在一起使用。因此,異構(gòu)集成在射頻模塊設(shè)計中已經(jīng)出現(xiàn)多年。現(xiàn)在有新的方法能夠以更簡化的方式堆疊各個基板技術(shù)。曾幾何時,你必須按層次結(jié)構(gòu)來做這件事。您必須將一項(xiàng)技術(shù)集成到另一項(xiàng)技術(shù)中,然后集成第三種技術(shù)。現(xiàn)在,我們可以將所有單獨(dú)的技術(shù)組合成一項(xiàng),從而使設(shè)計層次結(jié)構(gòu)扁平化,并使設(shè)計變得更加容易。既然您正在談?wù)撍羞@些不同的接口和所有這些不同的層,從一種技術(shù)連接到另一種技術(shù),您需要能夠跟蹤信號并分析信號路徑在所有這些邊界上的行為方式”。

勞動力問題

隨著整合而來的是勞動力問題。如今,芯片、封裝、驗(yàn)證和測試工程師通常處于責(zé)任和專業(yè)知識的孤島中。這需要改變。

“連續(xù)的‘跨界’方法不適合跨學(xué)科的協(xié)同設(shè)計和協(xié)同優(yōu)化,”西門子的Felton說。“參與 HI 設(shè)計的設(shè)計師和設(shè)計團(tuán)隊(duì)需要能夠更早地了解集成和架構(gòu)選擇的影響,并在設(shè)計進(jìn)入詳細(xì)實(shí)施之前做出決策和權(quán)衡。這通常稱為“左移”,需要將設(shè)計方法更改為imec 定義的系統(tǒng)技術(shù)協(xié)同優(yōu)化 (STCO)。當(dāng)然,勞動力教育/賦能是未來勞動力的關(guān)鍵,美國政府正在通過 NGMM、Cornerstone 等項(xiàng)目解決這一問題。”

芯片公司成功的基礎(chǔ)之一是設(shè)計團(tuán)隊(duì)的長壽和凝聚力。這對于先進(jìn)封裝尤其重要。

“如果我去航空航天和國防客戶那里,他們就去過那里,這就是他們所知道的,這就是他們做事的方式,”Park說。“你去一家大型商業(yè)公司,都是一樣的。他們一直都在那里。他們就是這樣做事的。我很少看到有人離開航空航天和國防領(lǐng)域并決定加入這家制造手機(jī)芯片的公司。人們通常會留在自己關(guān)注的領(lǐng)域。設(shè)計這些東西的專業(yè)知識不只是一個人的。

但現(xiàn)在,隨著系統(tǒng)和 IC 的融合,這意味著需要更多的人員。您請信號完整性專家來看看,“如果您將這個小芯片從中介層移到層壓板上,是否仍能提供我想要的帶寬?” 或者,你讓熱學(xué)人員進(jìn)來問,“如果我將這兩件事疊加在一起,從熱學(xué)角度來看這可行嗎?” 現(xiàn)在這是一個巨大的團(tuán)隊(duì)努力。您無法將芯片設(shè)計和封裝設(shè)計者分開。他們都與設(shè)計和驗(yàn)證工程師一起負(fù)責(zé)封裝、布局、散熱、信號完整性、電磁學(xué)、布局布線、簽核——所有這些不同的人都需要聚集在一起。”

代工廠在 3DHI 中的作用

3DHI 的基礎(chǔ)是半導(dǎo)體代工廠作為整個項(xiàng)目的推動者。

“沒有代工廠,你就無法進(jìn)行異構(gòu)分離,”Park 說。“它們是所有正在發(fā)生的事情的推動者,從 3D 堆疊到異構(gòu)集成,再到超高密度 RDL。這是因?yàn)榇S已經(jīng)認(rèn)識到整個世界正在走向多芯片、多芯片——這就是未來。因此,他們現(xiàn)在需要做后端并集成所有這些晶圓,而不僅僅是設(shè)計這些晶圓。這意味著他們現(xiàn)在正在與 OSAT 競爭,但 OSAT 和代工廠之間的競爭總是好的。”

例如,臺積電的 3DBlox 和三星的 CODE 是巨大的推動者,特別是對于剛接觸封裝設(shè)計的人來說。

“這是這組文件。將這些讀入您的工具中,它就會為您的設(shè)計建立整個 3D 平面圖,”Park 說。“順便說一句,我們保證它建立的 3D 平面圖可以按照這種方式制造。這是代工廠帶來的巨大推動力。鑄造廠帶來了正式的設(shè)計結(jié)構(gòu),而不是非常非正式的包裝世界。為了提高產(chǎn)量、降低價格,鑄造廠將這種正式感帶入了包裝中。其中一些開始滲透到包裝中,因此我們可以開始制定更正式的 OSAT 設(shè)計流程,這對行業(yè)來說都是好事。”

西門子的 Felton 指出,代工廠、OSAT 和基板供應(yīng)商可以在減少 HI 采用障礙方面發(fā)揮重要作用。“第一步是幫助客戶確保 DRC/PDK 的簽署和流程合規(guī)性。下一個領(lǐng)域是提供設(shè)計工具支持,例如設(shè)計模板、技術(shù)塊、使用標(biāo)準(zhǔn)的裝配規(guī)范。除此之外,一些 OSAT 和基板供應(yīng)商正在為其客戶提供增值服務(wù),例如脫氣和阻抗匹配,這減輕了客戶可能面臨的所需工作量和技能。”

Chiplet 問題

3DHI 仍然被許多人認(rèn)為是狂野的西部,而 Chiplet 是這個尚未被馴服的世界中不斷增長的一部分。

Expedera營銷副總裁 Paul Karazuba 表示:“當(dāng)我們談?wù)搧碜远鄠€供應(yīng)商的小芯片時——AMD 或英特爾的小芯片,情況就不同了。” “這只是制造設(shè)計的選擇。這幾乎不是您在不同小芯片供應(yīng)商那里面臨的供應(yīng)鏈問題。”

雖然商業(yè)小芯片正在取得進(jìn)展,但互連標(biāo)準(zhǔn)仍然不存在。

“UCIe 一年前引起了很大的轟動,”卡拉祖巴說。“今天我不一定會看到同樣多的噪音。這可能只是人們正在開發(fā)它的一個因素。UCIe 提供了很多承諾,并且確實(shí)提供了很多承諾。我們需要完成這件事。”

但小芯片仍然存在一些業(yè)務(wù)問題。

“誰為設(shè)備提供保修?這一切將如何處理?是否會有通用的信賴標(biāo)準(zhǔn)?我們?nèi)绾螠y試這些小芯片是否會有通用標(biāo)準(zhǔn)?實(shí)際上,這可能會通過多芯片模塊外部的名稱來設(shè)置,因?yàn)槲覀冃枰獮榻M裝的小芯片提供一個更好的名稱,”Karazuba 說。“盒子外面的名字很可能就是決定這一切的人,但這些如何相互作用仍然是一個懸而未決的問題。

對于像“實(shí)際上如何物理連接所有這些”這樣簡單的問題,當(dāng)今封裝單片硅上的互連在不同位置、不同節(jié)點(diǎn)等方面仍然有很大不同。因此,仍有大量工作需要完成必須要做。但半導(dǎo)體行業(yè) 70 年來一直擅長的一件事就是解決極其復(fù)雜的問題,并讓事情看起來如此簡單,而實(shí)際上并非如此。”

審核編輯:劉清

-

soc

+關(guān)注

關(guān)注

38文章

4385瀏覽量

222639 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1085瀏覽量

55635 -

3D芯片

+關(guān)注

關(guān)注

0文章

52瀏覽量

18785 -

ASIC芯片

+關(guān)注

關(guān)注

2文章

92瀏覽量

24274 -

chiplet

+關(guān)注

關(guān)注

6文章

459瀏覽量

12988

原文標(biāo)題:3D芯片,怎么辦?

文章出處:【微信號:晶揚(yáng)電子,微信公眾號:晶揚(yáng)電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

英倫科技裸眼3D便攜屏有哪些特點(diǎn)?

SciChart 3D for WPF圖表庫

騰訊混元3D AI創(chuàng)作引擎正式發(fā)布

騰訊混元3D AI創(chuàng)作引擎正式上線

DMD芯片在3D打印中的創(chuàng)新應(yīng)用

3D集成電路的結(jié)構(gòu)和優(yōu)勢

3D封裝熱設(shè)計:挑戰(zhàn)與機(jī)遇并存

3D芯片,怎么辦?

3D芯片,怎么辦?

評論