電子發燒友網報道(文/周凱揚)對于任何先進晶圓廠來說,逐漸放緩的制造工藝進步已經開始對其業務造成部分影響。即便是頭部客戶,也會追求相對成熟的工藝來減少設計和制造成本。為了不讓芯片性能停滯不前,絕大多數廠商會選擇異構集成的方式,借助先進封裝技術實現“超越摩爾”。諸如臺積電、英特爾等廠商,也都紛紛推出了3DFabric、Foveros之類的技術,而三星也不甘落后,一并追求突破半導體技術的極限。

為了進一步發揮其先進封裝技術優勢,三星于去年年底在其半導體業務部門內成立了先進封裝(AVP)業務團隊。作為一家同時具備內存、邏輯代工和封裝業務的廠商,三星在異構集成上已經有了多年的經驗,尤其是邏輯與內存的異構集成。

I-Cube

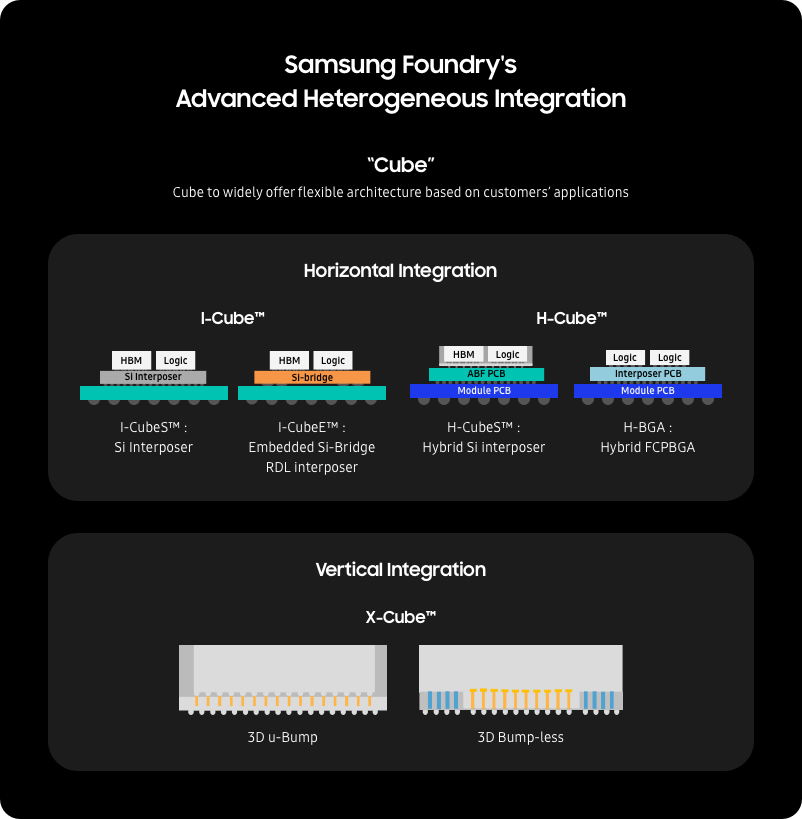

以絕大多數服務器芯片面臨的帶寬問題為例,三星針對不同的帶寬需求,提供了完備的解決方案。比如針對需要1TB/s的超大帶寬場景,三星提供了邏輯電路垂直堆疊的架構。而針對需要超大內存帶寬的場景,比如196GB/s到1TB/s的帶寬范圍內,三星則提供了邏輯電路與HBM堆疊至硅中介層上的方案,I-CubeS。

且根據HBM die的配置分布,三星已經推出了I-Cube2、I-Cube4、I-Cube8三大方案,更為復雜的I-Cube12也已經在研發過程中,預計明年第四季度成功驗證,2025年實現量產。這也是越來越多服務器、AI芯片所選的方案,I-Cube與HBM3的搭配提供了相對GDDR6更高的容量和帶寬。

三星Cube異構集成技術 / 三星

除此之外,三星也在研究HBM與邏輯電路直接垂直堆疊的方案,這類HBM無需緩存die,而是將緩存die集成到邏輯die中,進一步提高能效降低延遲。有趣的是,最近韓媒也爆出消息,SK海力士將與英偉達聯合研究GPU直接堆疊HBM4的設計,不過其最終封裝可能會由臺積電來接手。

針對60-196GB/s內存帶寬區間的應用,比如頭戴AR/VR等設備,三星的計劃是進一步提高其能效和降低延遲。為此,三星正在進行LLW DRAM這一低延遲寬IO產品的研發,用于替代傳統的LPDDR內存。其異構集成結構是將邏輯電路和LLW內存垂直堆疊在重布線層(RDL)上,根據三星給出的數據,相比傳統的FBGA封裝LPDDR內存,其I/O數、帶寬都將成倍增長,而相比硅中介層的方案又可以節省20%的封裝成本。

X-Cube

至于全3D的邏輯異構集成方案X-Cube,則是通過微凸塊或更先進的銅鍵合技術,將兩塊垂直堆疊的邏輯裸片連接起來。其實早在HBM的垂直堆疊上,三星就已經用上了微凸塊連接技術,且自2016年就實現了大規模量產。

然而面對更為復雜的邏輯die垂直堆疊,則需要對其設計進一步改進,從而避免電源完整性、信號完整性以及熱設計上帶來的新問題。所以三星也在研究相關的集成硅電容、散熱增強設計等,來解決這些異構集成實現過程中的頑疾。

三星代工業務的發展負責人Moonsoo Kang表示,他們預計將在明年開始量產微凸塊類型的X-Cube產品,而2026年才會開始量產銅鍵合的X-Cube產品。可以看出,在臺積電和英特爾廠商都已經規劃好下一代先進封裝路線圖的前提下,三星也在加快步伐推進新技術的落地,這樣才能給其半導體業務帶來更多的競爭優勢。

寫在最后

與依然在緩步推進的邏輯工藝不同,異構集成這類先進封裝技術最終是起到降低設計成本,提高芯片設計效率并優化PPA的目的,更像是對摩爾定律的一個橫向擴展。而作為晶圓廠,在鉆研這類技術的同時,也必須與EDA、Chiplet、PCB等領域的廠商達成深入合作,才有可能把這類業務推向更多的芯片設計公司。

-

晶圓廠

+關注

關注

7文章

636瀏覽量

38328

發布評論請先 登錄

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

IEDM 2024先進工藝探討(三):2D材料技術的進展及所遇挑戰

人工智能應用中的異構集成技術

Rapidus計劃建設1.4nm工藝第二晶圓廠

薄板拼焊激光焊接工藝

晶合集成28納米邏輯工藝通過驗證

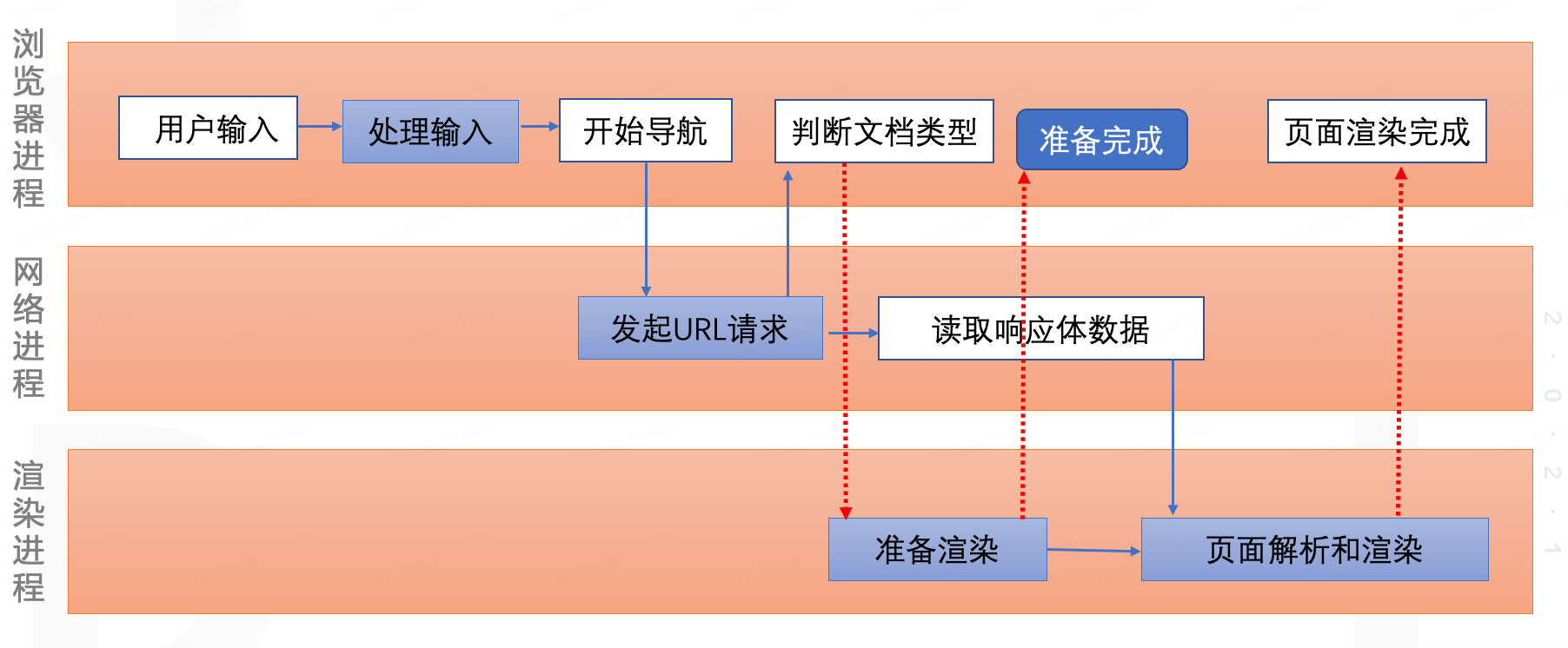

不只是前端,后端、產品和測試也需要了解的瀏覽器知識(二)

晶圓廠拼的不只是先進邏輯工藝節點,異構集成技術不可小覷

晶圓廠拼的不只是先進邏輯工藝節點,異構集成技術不可小覷

評論