一、Nand Flash接口定義解析

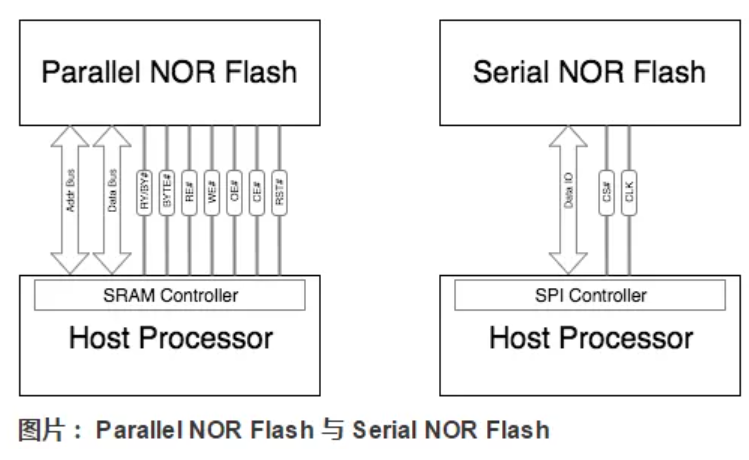

Nand Flash因其具有容量大、成本低、壽命長的特點,被廣泛的用作數據存儲的解決方案。然而NandFlash的讀寫控制較為復雜,Nand Flash的接口控制器大多是基于PC機或ARM處理器為架構進行開發的,存在操作不方便的問題。

FPGA實現Nand Flash接口的優點有很多。首先,FPGA可以實現Nand Flash的高速讀寫,因為FPGA可以通過并行處理來提高數據傳輸速度。其次,FPGA可以實現Nand Flash的高可靠性,因為FPGA可以通過ECC校驗來檢測和糾正數據傳輸中的錯誤。此外,FPGA可以實現Nand Flash的低功耗,因為FPGA可以通過動態電壓調節技術來降低功耗。最后,FPGA可以實現Nand Flash的高靈活性,因為FPGA可以通過重新編程來適應不同的應用場景。

在Nand Flash控制器中,接口的設計直接影響Nand Flash控制器訪問存儲顆粒的速度。目前業界有兩種主流的接口標準ONFI(Open Nand Flash Interface)與Toggle。ONFI是Intel和Micron等公司主導的開放的Nand Flash接口標準,這里主要針對ONFI標準進行描述。

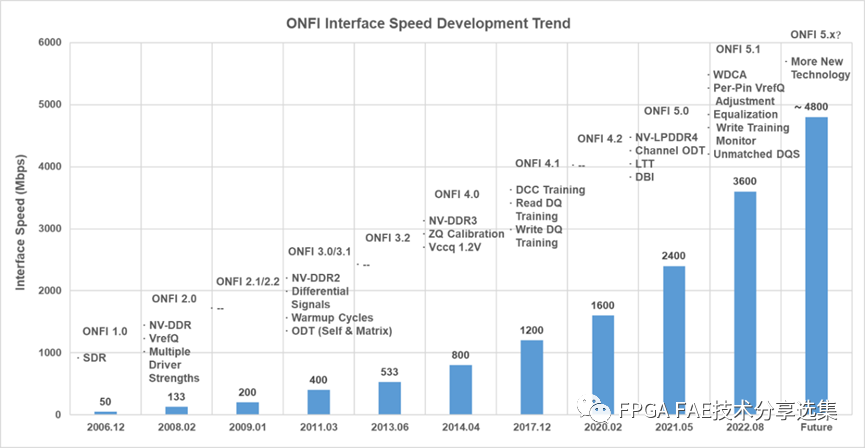

圖1、ONFI標準發展

如圖1所示,ONFI目前支持5種不同的數據接口類型:SDR/NV-DDR/NV-DDR2/NV-DDR3和NV-LPDDR4。SDR是傳統的NAND接口,使用RE_n鎖存讀數據,WE_n鎖存寫數據,沒有時鐘。NV-DDR是雙數據率(Double Data Rate-DDR)接口,含有用來鎖存命令和地址的時鐘,和一個用來鎖存數據的數據選通信號。

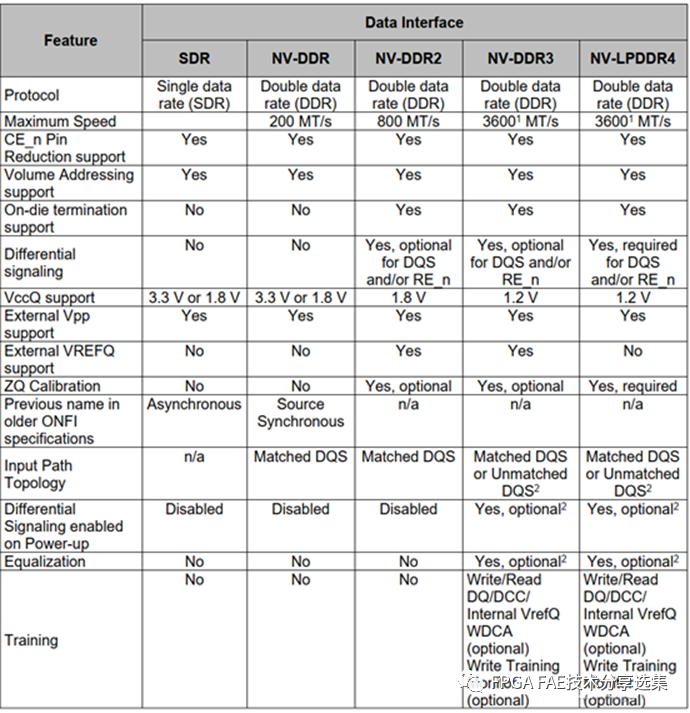

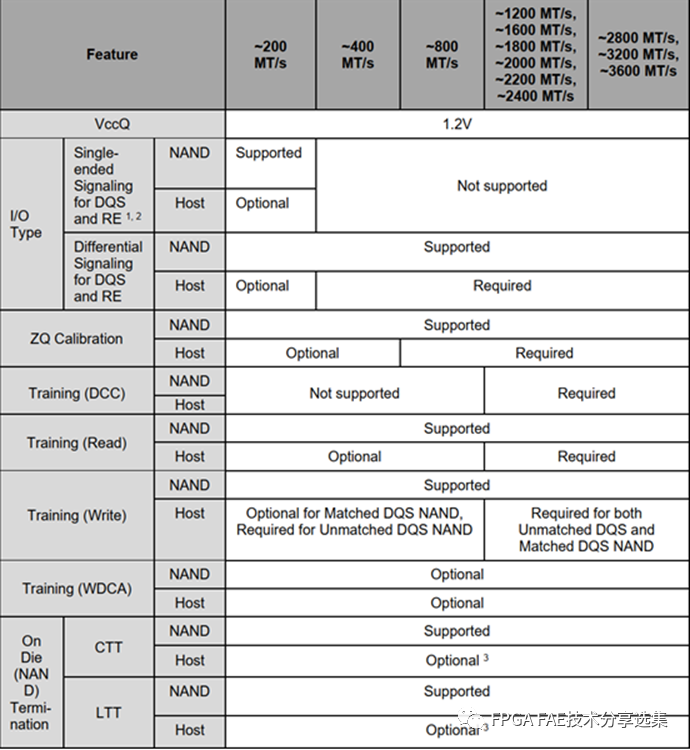

NV-DDR2是雙數據率接口,含有額外的擴展速度(scaling speed)的功能,像On-Dietermination以及差分信號。NV-DDR3接口包含所有NV-DDR2的特性,但操作在VccQ=1.2V。數據接口包含的特性如下圖2所示。

圖2 、ONFI數據接口

如果上電時VccQ=1.8V或3.3V,則device 應該操作在SDR接口timing mode 0。如果 Host 在參數page中判定NV-DDR 和NV-DDR2都被支持,則host可以通過Feature Address為01h的SetFeature命令,來選擇其中一個接口以及支持的timing mode。參見ONFI 5.1 5.31.1。

如果上電時VccQ=1.2V,則 device 應操作在NV-DDR3接口timing mode 0。如果host 在參數page中判明了支持的NV-DDR3timing mode,則host可以通過將CE_n轉為高來使能支持的timing mode,并將接口速度改變為期望的timing mode。當host 將CE_n 拉低后,新的timingmode會生效。參見ONFI 5.15.31.1。

二、ONFI的接口信號

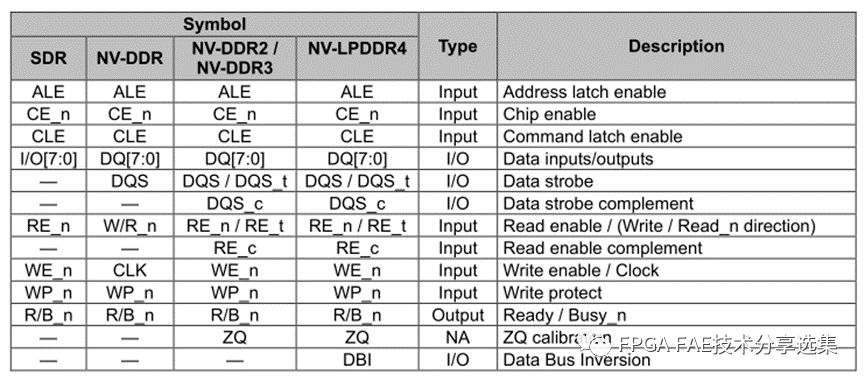

圖4、Signal Assignment based on Data Interface Type

如圖4所示,ONFI標準發展過程中的接口SDR/NV-DDR/NV-DDR2/NV-DDR3/NV-LPDDR4,其接口信號也有了相應的調整。

對于NV-DDR/NV-DDR2/NV-DDR3和NV-LPDDR4接口,與 SDR 接口相比,其共同的變化有:

a、I/O總線重命名為DQ總線

b、新加了一個名為DQS(DQ Strobe)的DQ 數據總線選通信號。DQS是雙向信號,用于數據傳輸。DQS不能用于命令或地址周期。對于從host到device的數據傳輸(寫),DQS的鎖存沿對齊到有效數據窗口的中間;對于從device到host的數據傳輸(讀),DQS的鎖存沿對齊到DQ總線的轉換沿。當操作在SDR接口時,DQS應該被host拉高,被device忽略。

對于 NV-DDR 接口,與SDR接口相比,主要變化有:

a、WE_n變成時鐘信號(CLK)。CLK應該被使能并且具有有效的時鐘周期,不論命令周期,地址周期和數據周期什么時候發生。在CE_n為低期間,CLK應保持相同的頻率;參見2.9.1。

b、RE_n變成寫/讀方向信號(W/R_n)。該信號表示誰擁有DQ總線和DQS信號。Host應該僅在ALE和CLE被鎖存到0時才能轉換W/R_n;參見4.20.2.6中W/R_n要求。

對于NV-DDR2和NV-DDR3接口,與SDR接口相比,主要變化有:

c、RE_n 可作為單端信號(single-ended)或者作為一個互補信號對(RE_t,RE_c)使用

d、增加了名為DQS(DQ strobe)的DQ數據總線選通信號。DQS可作為單端信號或者作為一個互補信號對(DQS_t,DQS_c)使用。

對于NV-LPDDR4數據接口,與SDR數據接口相比,變化如下:

a、RE_n必須用作互補信號對(RE_t、RE_c)。

b、增加了一個用于DQ數據總線的選通信號,稱為DQS(DQ選通)。DQS必須用作互補信號對(DQS_t、DQS_c)。

c、添加了一個用于DQ數據總線的可選數據總線反相信號,稱為DBI_n。DBI_ n指定DQ信號是否被反轉。DBI_n被視為DQ,因此AC參數和接口訓練等規范應適用于DBI。

三、基于AMD FPGA的Nand Flash接口讀寫實現

基于上述ONFI的協議標準,使用AMD FPGA進行Nand Flash的接口設計有如下幾個優點:

由于Nand Flash的接口速率比較高,AMD FPGA的IO口性能通過很多代產品的迭代,IO口性能比較穩定,兼容性較好;

可以使用AMD MPSOC進行設計,通過PS端的程序編寫,可以方便地配合PL端進行ONFI標準的接口設計,執行效率高,并且設計比較簡單成熟;

在進行ONFI標準升級時,可以通過修改接口PHY部分的硬核邏輯(OSERDES/ISERDES)的配置,就可以提升接口的帶寬,可靠性和穩定性都很好。

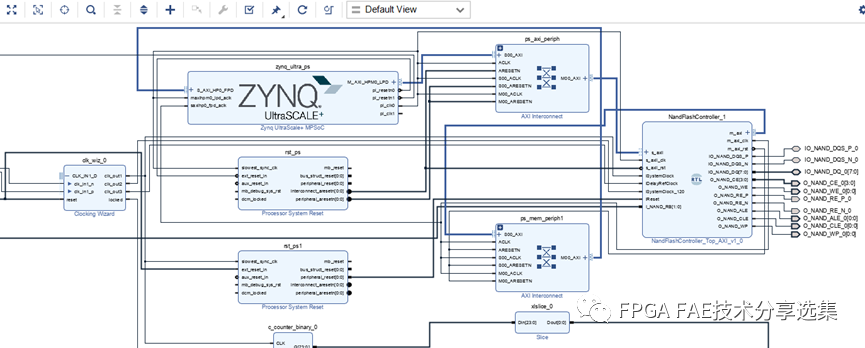

如圖5所示,使用AMD 的MPSOC可以方便地通過如下類似的BD配置,只需要PS使用簡單函數把NandFlash當作普通外設即可進行讀寫,實現數據的配置和讀寫Nand Flash。如下圖所示。圖中僅展示了Nand Flash的單個通道的接口BD配置。

由于篇幅有限,不對Nand Flash芯片的各個命令不同模式的時序信號進行介紹,默認大家是了解的。

圖5、MPSOC讀寫Flash的簡單BD配置

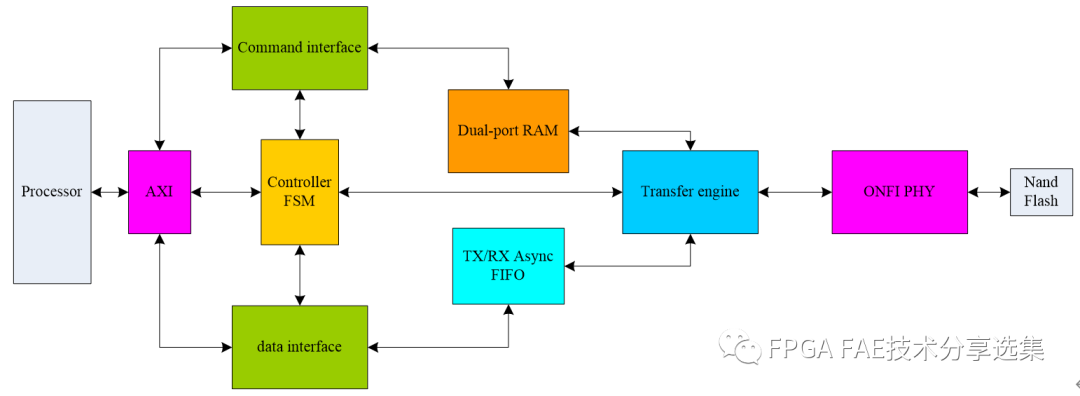

而其中有關Nand Flash Controller的架構建議如下圖6所示。

圖6、ONFI的Nand Flash Controller實現

Nand Flash控制器硬件系統中, 各個模塊的功能描述如下:

1) 、AXI總線接口模塊模塊

AXI總線接口模塊接收來自PS端或者CPU端發送的命令以及數據信息, 然后把相應的設備狀態的值, 通過狀態寄存器返回給PS或CPU。它是PS與Nand Flash控制器進行數據、命令等交互的橋梁。

2) 、控制器狀態機模塊

控制器固件對Nand Flash芯片的各種操作由狀態機完成, 狀態機包含Nand Flash控制器運行的各種狀態, 每一個命令碼操作由Nand Flash控制器的各種狀態有序組合而成, 共同完成對Nand Flash存儲芯片的一次操作。

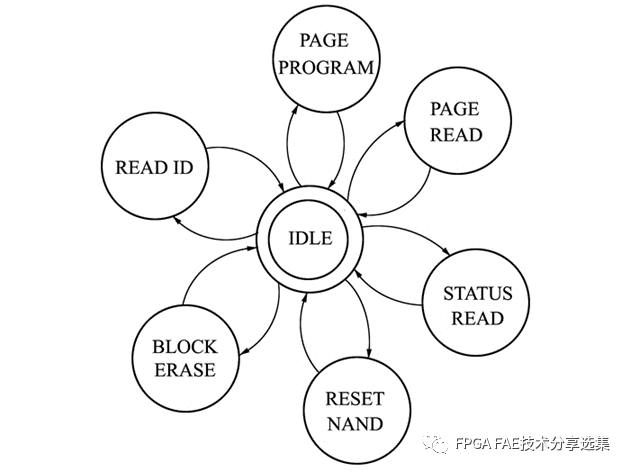

圖7、控制器狀態機

Nand Flash控制器的功能實現由控制器狀態機模塊完成。系統沒有操作時, 控制器處于IDLE狀態, 命令代碼被寫入命令寄存器,確定下一步要執行的命令后,Nand Flash控制器轉移到某個相應的子狀態序列, 完成對存儲器的指定操作。

在控制器狀態機中, 程序將執行不同功能的控制。每個獨立的過程由一個子狀態機來實現, 通過系統的時鐘來控制所有的狀態轉換。每個子狀態操作完成需要的步驟和時鐘個數可能不盡相同, 程序則通過維護一個專用寄存器進行協調, 以確保滿足Nand Flash器件的時間控制要求。

3) 、命令接口模塊

命令接口用于進行命令的識別和判斷,Processor側可以封裝好不同opcode的命令,方便軟件進行操作。比如,Select Way0命令,可以設置opcode為6'h20,address為{24'd0,8'b1}。

4) 、數據接口模塊

數據接口主要是有關控制器的用戶側數據的輸入和輸出接口實現(基于AXI接口),比如iWriteData、iWriteLast、iWriteValid、iWriteKeep、WriteReady、oReadData、oReadLast、oReadValid、oReadKeep、iReadReady等。

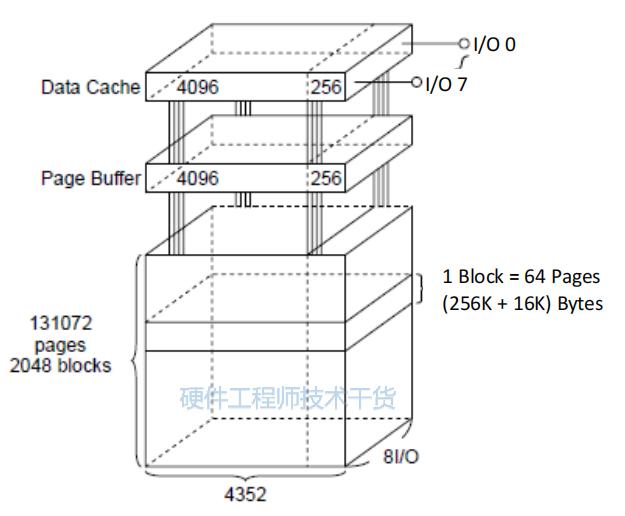

5) 、緩存模塊

緩存模塊包括RAM和異步FIFO模塊,模塊用于緩存命令和數據的雙端口RAM,由多個不同RAM和FIFO組成。

6) 、發送引擎模塊

根據ONFI的手冊,識別Command Interface的不同命令來拼好時隙,保證其通過PHY出去的時候,是符合對應模式下的對應命令的時序的。

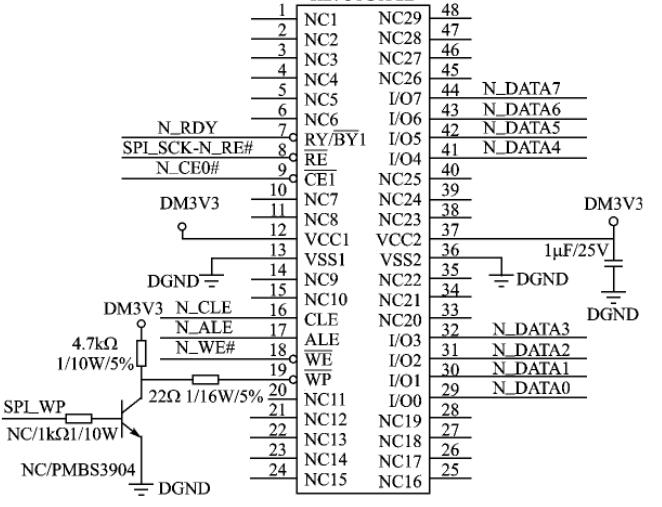

7) 、PHY接口模塊

PHY接口模塊需要使用ISERDES/OSERDES來實現,需要根據用戶側的時鐘頻率來決定接口的帶寬。通常需要向上兼容(為了兼容不同模式下的時序要求),需要兼容老的慢速模式(比如NV-DDR/NV-DDR2等),其信號是上述圖中的DQDQSCEWE等信號。

四、Nand Flash接口功能測試流程和實測結果

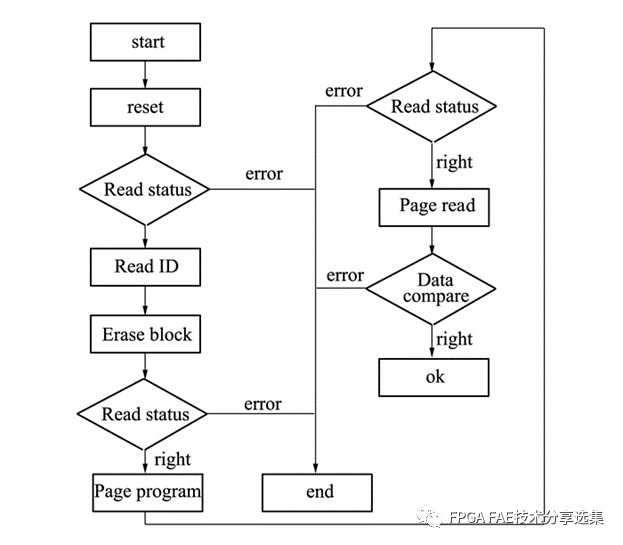

對本文所設計實現的Nand Flash控制器的功能, 在EDA軟件環境下進行了仿真驗證, 其測試流程如圖 8所示。

圖8、接口測試流程

在圖 5所示的仿真驗證過程中, 需對Nand Flash芯片進行一系列交互操作, 如讀ID、擦除、讀設備、頁編程、頁讀取、ECC校驗、I/O讀等, 且每次操作完成后, 都要讀設備狀態并判斷操作是否成功, 只有操作正常完成才繼續進行下一步的操作, 否則退出測試過程。

實際測試的結果是,按照上述方案,已經實現過ONFI2.1(NV-DDR2)的實際測試,暫未進行NV-DDR3接口的實際測試。實測MPSOC使用ZU19EG器件,NandFlash芯片選用MT29F64G08AECABH1。NandFlash芯片工作在mode 5狀態(8192 Bytesper Page)的實測條件下,實現了48 MB/s的寫入速度和93 MB/s 讀出速度。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21941瀏覽量

613322 -

amd

+關注

關注

25文章

5555瀏覽量

135753 -

控制器

+關注

關注

114文章

16918瀏覽量

182652 -

FlaSh

+關注

關注

10文章

1660瀏覽量

150887 -

接口

+關注

關注

33文章

8918瀏覽量

153118

原文標題:AMD FPGA實現Nand Flash接口讀寫方案

文章出處:【微信號:Comtech FPGA,微信公眾號:Comtech FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

標準NAND FLASH控制器/超高速NAND FLASH陣列控制器

SPARTAN 3 FPGA的Nand Flash接口優點是什么

nand flash 接口切換

基于FPGA的SD卡的數據讀寫實現(SD NAND FLASH)

NAND FLASH在WINCENET系統中的應用設計

NAND Flash 的存儲結構以及NAND Flash的接口控制設計

FPGA MCU FSMC通信接口——NAND Flash模式

NOR Flash和NAND FLASH的區別是什么

NAND Flash接口簡單介紹

NAND Flash 原理深度解析(下)

Nand Flash接口定義解析 基于AMD FPGA的Nand Flash接口讀寫實現

Nand Flash接口定義解析 基于AMD FPGA的Nand Flash接口讀寫實現

評論