1 VCO需要注意什么

常規(guī)LCVCO由電感、電容、負(fù)阻、偏置組成,每個(gè)模塊有很多種實(shí)現(xiàn)方式,下面給介紹一下各模塊設(shè)計(jì)時(shí)的注意事項(xiàng)。

1.1 電感

電感有平面螺旋結(jié)構(gòu)和堆疊結(jié)構(gòu)。主要技術(shù)指標(biāo)有品質(zhì)因子(Q)、自諧振頻率(F)、感值(L)。電感下面要加shielding,兩側(cè)要加isolation wall以提高Q值。Q值的提高主要從增大感值和減小串聯(lián)電阻角度考慮,F(xiàn)值的提高主要從減小寄生電容角度考慮,L值可以從結(jié)構(gòu)、線圈匝數(shù)角度考慮。

1.2 電容

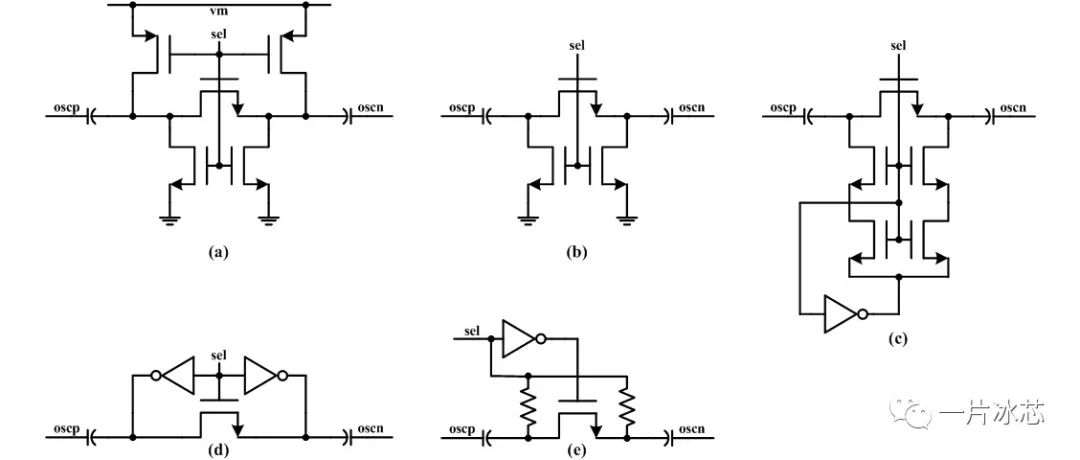

LCVCO通常需要電容陣列和varactor電容來實(shí)現(xiàn)較大的頻率覆蓋范圍,電容陣列和varactor電容的尺寸、結(jié)構(gòu)也有很多需要考慮的地方。圖1給出了幾種實(shí)用的單開關(guān)電容陣列結(jié)構(gòu),限于篇幅不再介紹每種結(jié)構(gòu)的優(yōu)缺點(diǎn)。

Fig1. 單開關(guān)電容陣列結(jié)構(gòu)

1.3 負(fù)阻

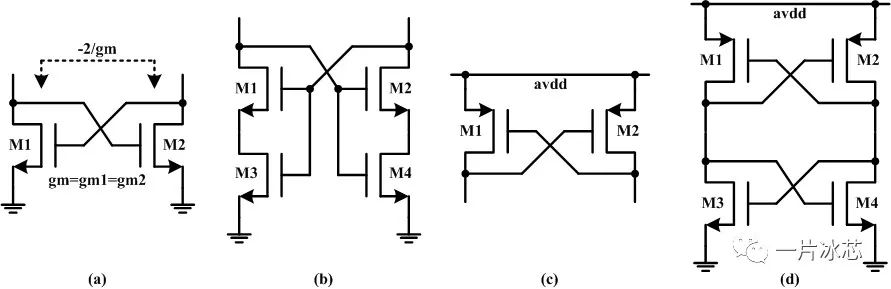

負(fù)阻有nmos-only(a), nmos-stack(b), pmos-only(c), cmos(d),結(jié)構(gòu),如圖2所示,其中nmos-only適用于高頻,cmos結(jié)構(gòu)適用于低功耗。

Fig2. 常見負(fù)阻結(jié)構(gòu)

1.4 偏置

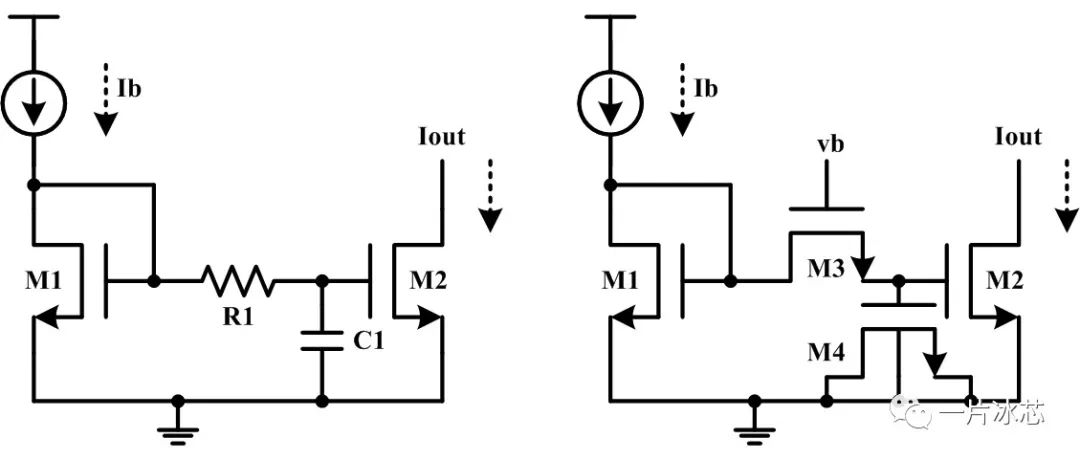

偏置電路需要濾波濾除來自基準(zhǔn)、耦合及本身的噪聲,圖3所示為兩種不同結(jié)構(gòu)的偏置噪聲濾波器,R1(倒比管M3)和C1(M4)的時(shí)間常數(shù)決定噪聲帶寬,噪聲帶寬至少要小于PLL環(huán)路帶寬,因?yàn)镻LL可以抑制VCO的帶內(nèi)噪聲。

相同RC時(shí)間常數(shù)下,右側(cè)結(jié)構(gòu)消耗更小的面積。相同RC常數(shù)下,當(dāng)M3等效電阻較大,M4等效電容較小時(shí)消耗面積最小。當(dāng)截止頻率為5kHz(R1=1MΩ,C1=30pF)時(shí)偏置建立時(shí)間需要200us,這會(huì)嚴(yán)重影響PLL的鎖定時(shí)間。為減小面積,M4采用MOS電容并在上面疊MOM電容的方式。

Fig3. 不同結(jié)構(gòu)的偏置濾波器

1.5 常見LCVCO結(jié)構(gòu)

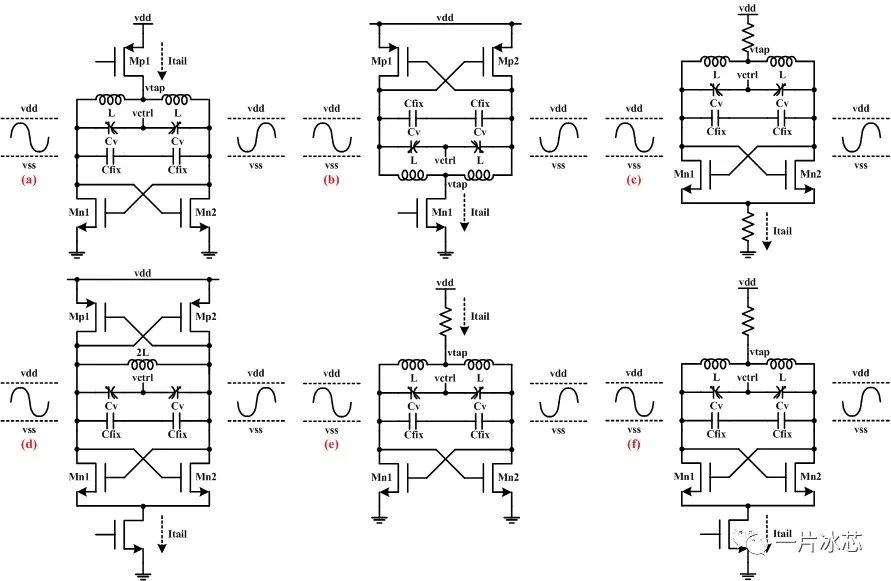

由電感、電容、負(fù)阻、偏置的不同組合可得到圖4所示不同結(jié)構(gòu)的LCVCO,同樣限于篇幅不再介紹每種結(jié)構(gòu)的優(yōu)缺點(diǎn)。

Fig4. 常見LCVCO結(jié)構(gòu)

2****Transformerbased VCO

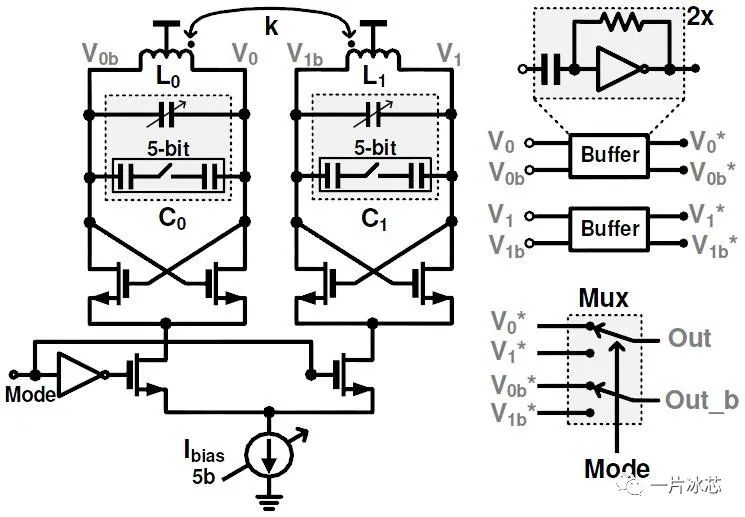

圖5給出了一種Transformer based VCO^[1]^,該結(jié)構(gòu)中的電容、負(fù)阻、偏置跟第一章的結(jié)構(gòu)類似,主要區(qū)別是將第一章中的電感換成了變壓器。合理設(shè)置C0和C1的比值(1.8)及模式0/1的選擇可覆蓋7~18.3GHz,18.3GHz的相位噪聲為-100dBc/Hz @ 1MHz。

該結(jié)構(gòu)將開關(guān)串聯(lián)在負(fù)阻管交流地,避免讓電感串聯(lián)一個(gè)電阻,提高了電感的Q值。輸出通過AC-coupled self-biased inverter結(jié)構(gòu)減小DC失調(diào)的同時(shí)實(shí)現(xiàn)滿擺幅放大。

Fig5. Transformer based VCO

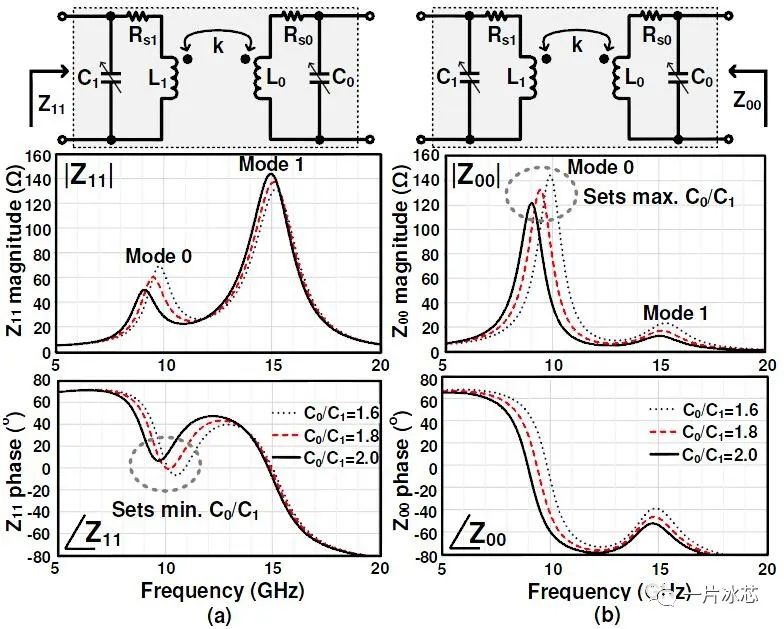

Z11和Z00的幅頻和相頻特性如圖6所示。圖中可以看出當(dāng)C0/C1足夠大(大于1.8)時(shí),Z11相位只有一個(gè)過0點(diǎn),因此,設(shè)置C0/C1大于1.8可以使Z11只有一個(gè)諧振點(diǎn)。隨著C0/C1比值不斷增大,Z00的幅度不斷降低,因此,功耗限制了C0/C1的最大值。在頻率調(diào)節(jié)過程中(粗調(diào)和細(xì)調(diào))要時(shí)刻保持C0/C1的比值在1.8左右,以免諧振到諧波。

Fig6. (a) Z11 and (b) Z00 of a lossy transformer for different C0/C1

圖7給出了Transformer的背景照片及結(jié)構(gòu),L0通過頂層金屬與次頂層串聯(lián)的方式增大L0感值,從而實(shí)現(xiàn)L0=L1。VCO面積僅為120 x 270 um^2^,最大功耗僅為4.4 mW。

Fig7. Chip micrograph and layout details

-

CMOS

+關(guān)注

關(guān)注

58文章

5978瀏覽量

238003 -

濾波器

+關(guān)注

關(guān)注

162文章

8058瀏覽量

180886 -

VCO

+關(guān)注

關(guān)注

13文章

311瀏覽量

69957 -

偏置電路

+關(guān)注

關(guān)注

10文章

99瀏覽量

31093 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6705

發(fā)布評(píng)論請(qǐng)先 登錄

一款1.9~5.7 GHz寬帶低噪聲BiCMOS LC VCO設(shè)計(jì)

求一種基于FPGA芯片的高速智能節(jié)點(diǎn)的硬件結(jié)構(gòu)和軟件設(shè)計(jì)

介紹一種基于FIFO結(jié)構(gòu)的優(yōu)化端點(diǎn)設(shè)計(jì)方案

求大佬介紹一種基于H.264的嵌入式技視頻監(jiān)控結(jié)構(gòu)和系統(tǒng)工作原理

一種新型的網(wǎng)格安全體系結(jié)構(gòu)

一種基于FPGA實(shí)現(xiàn)的FFT結(jié)構(gòu)

一種VLD結(jié)構(gòu)VDMOS終端設(shè)計(jì)

詳解一種簡單而有效的Transformer提升技術(shù)

一種新結(jié)構(gòu)線性調(diào)節(jié)器的新應(yīng)用

一種自適應(yīng)網(wǎng)頁結(jié)構(gòu)化信息提取方法

Transformer結(jié)構(gòu)及其應(yīng)用詳解

大模型基礎(chǔ)Transformer結(jié)構(gòu)的原理解析

一種基于Transformer結(jié)構(gòu)的VCO介紹

一種基于Transformer結(jié)構(gòu)的VCO介紹

評(píng)論