前言

目前域控項目有的采用S32G這類多核異構(gòu)的芯片,轉(zhuǎn)載一篇分析下多核異構(gòu)中A核與M核通信過程的文章。

正文

一、 硬件層通信實現(xiàn)原理

二、驅(qū)動層Virtio下RPMsg通信實現(xiàn)

三、應(yīng)用層雙核通信實現(xiàn)方式

現(xiàn)在越來越多的產(chǎn)品具有M core和A core的異構(gòu)架構(gòu),既能達(dá)到M核的實時要求,又能滿足A核的生態(tài)和算力。比如NXP的i.MX8系列、瑞薩的RZ/G2L系列以及TI的AM62x系列等等。雖然這些處理器的品牌及性能有所不同,但多核通信原理基本一致,都是基于寄存器和中斷傳遞消息,基于共享內(nèi)存?zhèn)鬏敂?shù)據(jù)。

通信過程整體架構(gòu)說明

一、 硬件層通信實現(xiàn)原理

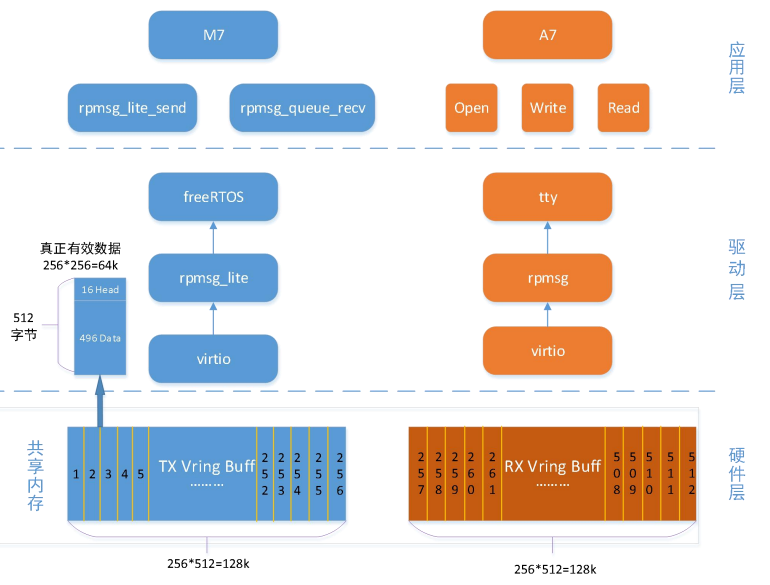

通過物理內(nèi)存DDR分配,將硬件層分為了兩部分:TXVring Buffer(發(fā)送虛擬環(huán)狀緩沖區(qū))和RXVring Buffer(接收虛擬環(huán)狀緩沖區(qū));其中M核從TXVring區(qū)發(fā)送數(shù)據(jù),從RXVring區(qū)讀取接收數(shù)據(jù),A核反之。

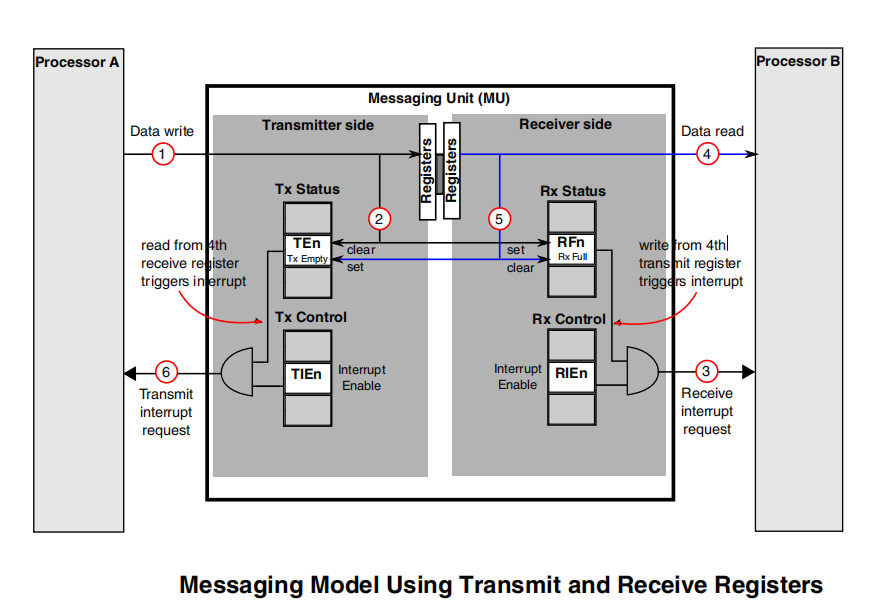

處理器支持消息傳遞單元(MessagingUnit,簡稱MU)功能模塊,通過MU傳遞消息進(jìn)行通信和協(xié)調(diào),M核和A核之間通過寄存器中斷的方式傳遞命令,最多支持4組MU雙向傳遞消息,既可通過中斷告知對方數(shù)據(jù)傳遞的狀態(tài),也可發(fā)送最多4字節(jié)數(shù)據(jù),還可在低功耗模式下喚醒對方,是保證雙核通信實時性的重要手段。

下面看下完成了1次從CoreA向CoreB 傳遞消息的具體過程:

寄存器輸入輸出通信模型

(1)CoreA寫入數(shù)據(jù);

(2)MU將Tx 空位清0,Rx滿位置1;

(3)產(chǎn)生接收中斷請求,通知CoreB接收狀態(tài)寄存器中的接收器滿,可以讀取數(shù)據(jù);

(4)CoreB響應(yīng)中斷,讀取數(shù)據(jù);

(5)CoreB讀完數(shù)據(jù)后,MU將Rx滿位清0,Tx空位置1;

(6)狀態(tài)寄存器向CoreA生成發(fā)送中斷請求,告知CoreB讀完數(shù)據(jù),發(fā)送寄存器空。

二、驅(qū)動層Virtio下RPMsg通信實現(xiàn)

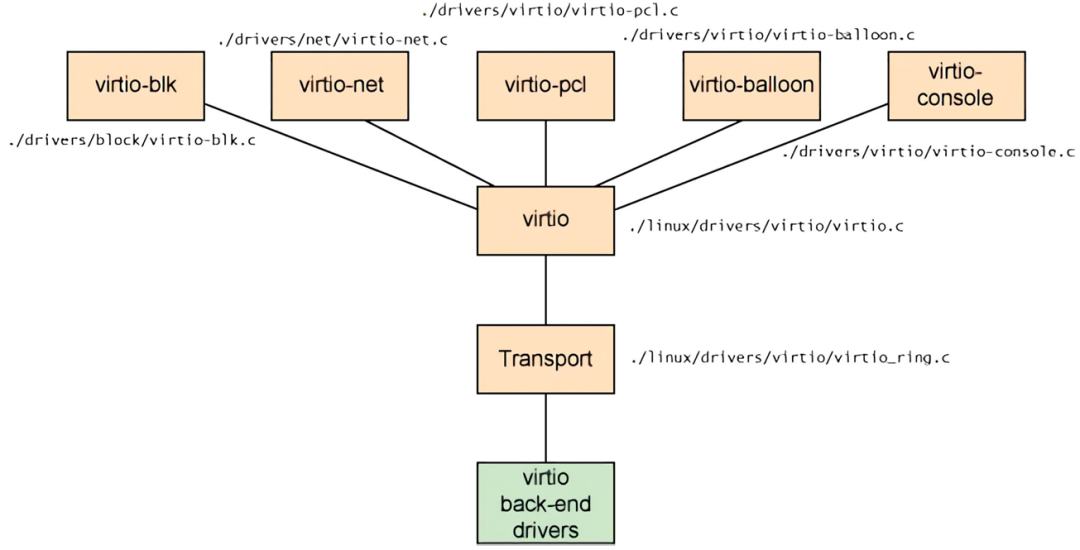

virtio 是一個通用的 I/O 虛擬化框架,位于設(shè)備之上的抽象層,負(fù)責(zé)前后端之間的通知機(jī)制和控制流程,為異構(gòu)多核間數(shù)據(jù)通信提供了層的實現(xiàn)。hypervisor 通過他模擬出一系列的虛擬化設(shè)備,例如:virtio-net、virtio-blk等,并使得這些設(shè)備在虛擬機(jī)內(nèi)部通過 api 調(diào)用的方式變得可用。它包含4個部分:前端驅(qū)動、后端驅(qū)動、 vring 及通信間統(tǒng)一的接口。與其他的模擬 I/O 方式對比, virtio 減少了虛擬機(jī)的退出和數(shù)據(jù)拷貝,能夠極大地提高 I/O 性能。計算機(jī)中存在不同的總線標(biāo)準(zhǔn),而 virtio 采用的是 pci 總線(當(dāng)然也可以用其他總線來實現(xiàn))。每一個 virtio 設(shè)備就是一個 pci 設(shè)備。

virtio前端驅(qū)動

virtio 前端驅(qū)動位于 Linux 內(nèi)核中,運(yùn)行在虛擬機(jī) VM,針對不同類型的設(shè)備有不同類型的驅(qū)動程序,包括virtio-net、virtio-blk、virtio-pci等,這些驅(qū)動程序與后端驅(qū)動交互的接口都是統(tǒng)一的。

virtio層

virtio層實現(xiàn)虛擬隊列接口,作為前后端通信的橋梁,不同類型的設(shè)備使用的虛擬隊列數(shù)量不同,例如 virtio-net 使用兩個虛擬隊列,一個用于接收,一個用于發(fā)送;virtio-blk 驅(qū)動僅使用一個虛擬隊列。虛擬隊列實際上被實現(xiàn)為跨越客戶機(jī)操作系統(tǒng)和 hypervisor 的銜接點,可以通過任意方式實現(xiàn),前提是客戶機(jī)操作系統(tǒng)和 virtio 后端程序都遵循一定的標(biāo)準(zhǔn),以相互匹配的方式實現(xiàn)它。

virtio-ring層

virtio-ring 是虛擬隊列的具體實現(xiàn),其中實現(xiàn)了環(huán)形緩沖區(qū)(ring buffer),用于保存前端驅(qū)動和后端處理程序執(zhí)行的信息,并且它可以一次性保存前端驅(qū)動的多次I/O請求,并且交由后端驅(qū)動去批量處理,最后實際調(diào)用宿主機(jī)中設(shè)備驅(qū)動實現(xiàn)物理上的I/O操作,這樣做就可以根據(jù)約定實現(xiàn)批量處理而不是客戶機(jī)中每次I/O請求都需要處理一次,從而提高客戶機(jī)與 hypervisor 信息交換的效率。

virtio后端驅(qū)動

virtio 后端驅(qū)動位于 qemu ,后端設(shè)備承擔(dān)的主體功能分為兩部分:

virtio后端設(shè)備的模擬;

依據(jù)virtio協(xié)議處理來自虛擬機(jī)端發(fā)送的請求。

在 QEMU 的實現(xiàn)中, virtio 設(shè)備是 QEMU 為虛擬機(jī)模擬的 PCI 設(shè)備,遵循 PCI-SIG 定義的 PCI 規(guī)范,具有配置空間、中斷配置等功能;virtio 后端驅(qū)動運(yùn)行在宿主機(jī)中,用于實現(xiàn) virtio 后端操作硬件設(shè)備,例如向內(nèi)核協(xié)議棧發(fā)送一個數(shù)據(jù)包完成虛擬機(jī)對網(wǎng)絡(luò)數(shù)據(jù)的操作。

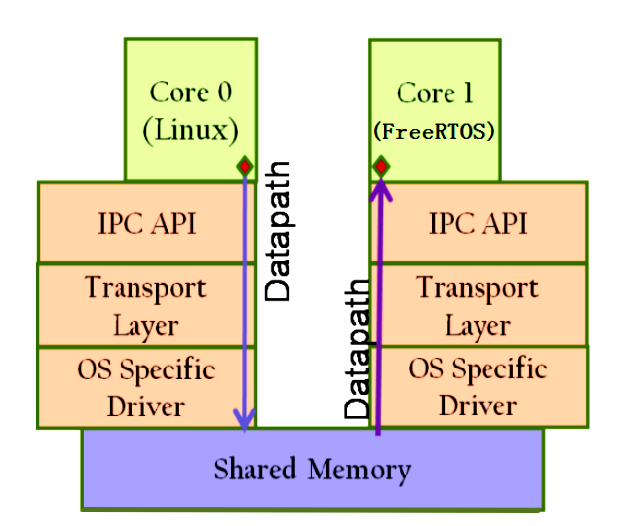

RPMsg消息框架是Linux系統(tǒng)基于Virtio緩存隊列實現(xiàn)的主處理核和協(xié)處理核間進(jìn)行消息通信的框架,當(dāng)客戶端驅(qū)動需要發(fā)送消息時,RPMsg會把消息封裝成Virtio緩存并添加到緩存隊列中以完成消息的發(fā)送,當(dāng)消息總線接收到協(xié)處理器送到的消息時也會合理地派送給客戶驅(qū)動程序進(jìn)行處理。

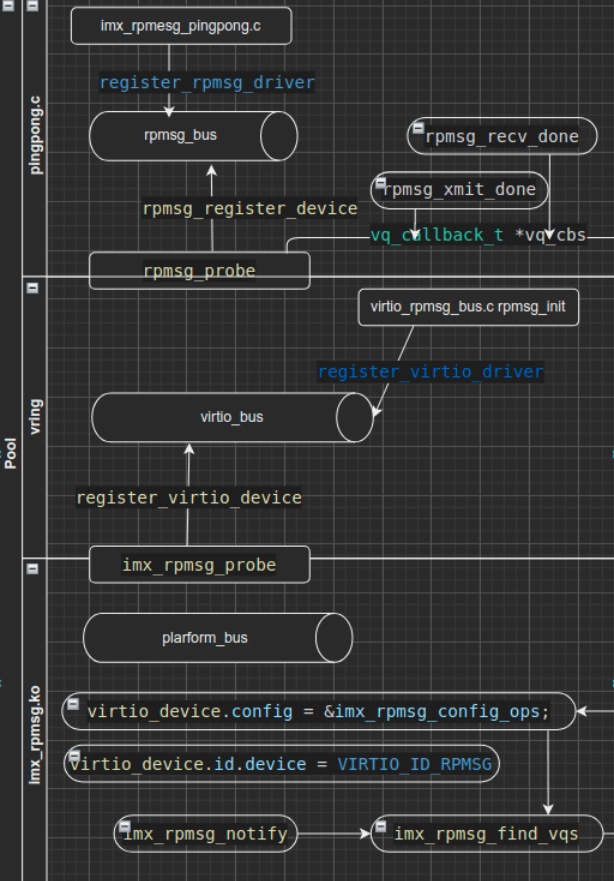

在驅(qū)動層,對A核,Linux采用RPMsg框架+Virtio驅(qū)動模型,將RPMsg封裝為了tty文件供應(yīng)用層調(diào)用;在M核,將Virtio移植,并使用簡化版的RPMsg,因為涉及到互斥鎖和信號量,最終使用FreeRTOS完成過程的封裝,流程框圖如下方所示。

主處理核與協(xié)處理核數(shù)據(jù)傳遞流程圖

(1)Core0向Core1發(fā)送數(shù)據(jù),通過rpmsg_send函數(shù)將數(shù)據(jù)打包至Virtioavail鏈表區(qū);

(2)在avail鏈表尋找共享內(nèi)存中空閑緩存,將數(shù)據(jù)置于共享內(nèi)存中;

(3)通過中斷通知Core1數(shù)據(jù)到來,共享內(nèi)存由avail鏈表區(qū)變至used區(qū);

(4)Core1收到中斷,觸發(fā)rpmsg的接收回調(diào)函數(shù),從used區(qū)獲取數(shù)據(jù)所在的共享內(nèi)存的物理地址,完成數(shù)據(jù)接收;

(5)通過中斷通知Core0數(shù)據(jù)接收完成,共享內(nèi)存緩存由used區(qū)變?yōu)閍vail區(qū),供下次傳輸使用。

三、應(yīng)用層雙核通信實現(xiàn)方式

在應(yīng)用層,對A核可使用open、write和read函數(shù)對 /dev下設(shè)備文件進(jìn)行調(diào)用;對M核,可使用rpmsg_lite_remote_init、rpmsg_lite_send和rpmsg_queue_recv函數(shù)進(jìn)行調(diào)用,不做重點闡述。從整體架構(gòu)上看,關(guān)系如下:

審核編輯:湯梓紅

-

處理器

+關(guān)注

關(guān)注

68文章

19795瀏覽量

233414 -

芯片

+關(guān)注

關(guān)注

459文章

52119瀏覽量

435627 -

通信

+關(guān)注

關(guān)注

18文章

6167瀏覽量

137333 -

瑞薩

+關(guān)注

關(guān)注

36文章

22366瀏覽量

87695 -

多核異構(gòu)

+關(guān)注

關(guān)注

0文章

19瀏覽量

5511

原文標(biāo)題:A核與M核異構(gòu)通信過程解析

文章出處:【微信號:汽車電子嵌入式,微信公眾號:汽車電子嵌入式】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

創(chuàng)龍帶您解密TI、Xilinx異構(gòu)多核SoC處理器核間通訊

核間通信(IPC)解決方案

MPU進(jìn)化,多核異構(gòu)處理器有多強(qiáng)?

A核+M核通信過程解析

多核異構(gòu)-雙核高速率CAN-FD評測

多核異構(gòu)-M核程序的啟動、編寫和仿真

多核異構(gòu)處理器對共享外設(shè)和資源的調(diào)配方法

S32G274有沒有M核和A核共享的PFE相關(guān)的例程或文檔?

Arm+RISC-V雙核異構(gòu)前景如何?

專用M4F+四核A53,異構(gòu)多核AM62x讓工業(yè)控制“更實時、更安全”

專用R5F+雙核A53,異構(gòu)多核AM64x讓工控“更實時”

嵌入式異構(gòu)多核的片上通信架構(gòu)設(shè)計

基于SystemC的異構(gòu)多核通信模塊設(shè)計

基于SystemC的異構(gòu)多核通信模塊設(shè)計

MPU進(jìn)化,多核異構(gòu)處理器有多強(qiáng)?A核與M核通信過程解析

多核異構(gòu)中A核與M核通信過程

多核異構(gòu)中A核與M核通信過程

評論