”前面的文章介紹邏輯算術(shù)運(yùn)算芯片(SN74181)實(shí)現(xiàn)4位的邏輯和算術(shù)運(yùn)算,用兩個(gè)芯片級(jí)連實(shí)現(xiàn)8位運(yùn)算。目標(biāo)是逐步實(shí)現(xiàn)一個(gè)簡(jiǎn)單的8位CPU的芯片邏輯”

01實(shí)驗(yàn)內(nèi)容

1.1 實(shí)驗(yàn)內(nèi)容

研究邏輯算術(shù)芯片SN74181的進(jìn)位原理,用兩個(gè)芯片級(jí)連實(shí)現(xiàn)8位的ALU(algorithm logic unit / 計(jì)算邏輯單元)。希望從現(xiàn)在開(kāi)始能夠逐步實(shí)現(xiàn)一個(gè)最最簡(jiǎn)單的8位CPU邏輯,具有8位的ALU是第一步。

1.2 知識(shí)點(diǎn)

計(jì)算機(jī)能夠進(jìn)行復(fù)雜的計(jì)算,其核心就是基本的邏輯運(yùn)算(與、或、非等)和算術(shù)計(jì)算(加法等)。

02實(shí)驗(yàn)準(zhǔn)備

2.1 實(shí)驗(yàn)器材

要完成本次實(shí)驗(yàn),我們需要如下的元器件。

2.2 元器件解釋

SN74181芯片:

接前一篇,級(jí)聯(lián)的關(guān)鍵

2.3 芯片級(jí)聯(lián)的工作原理

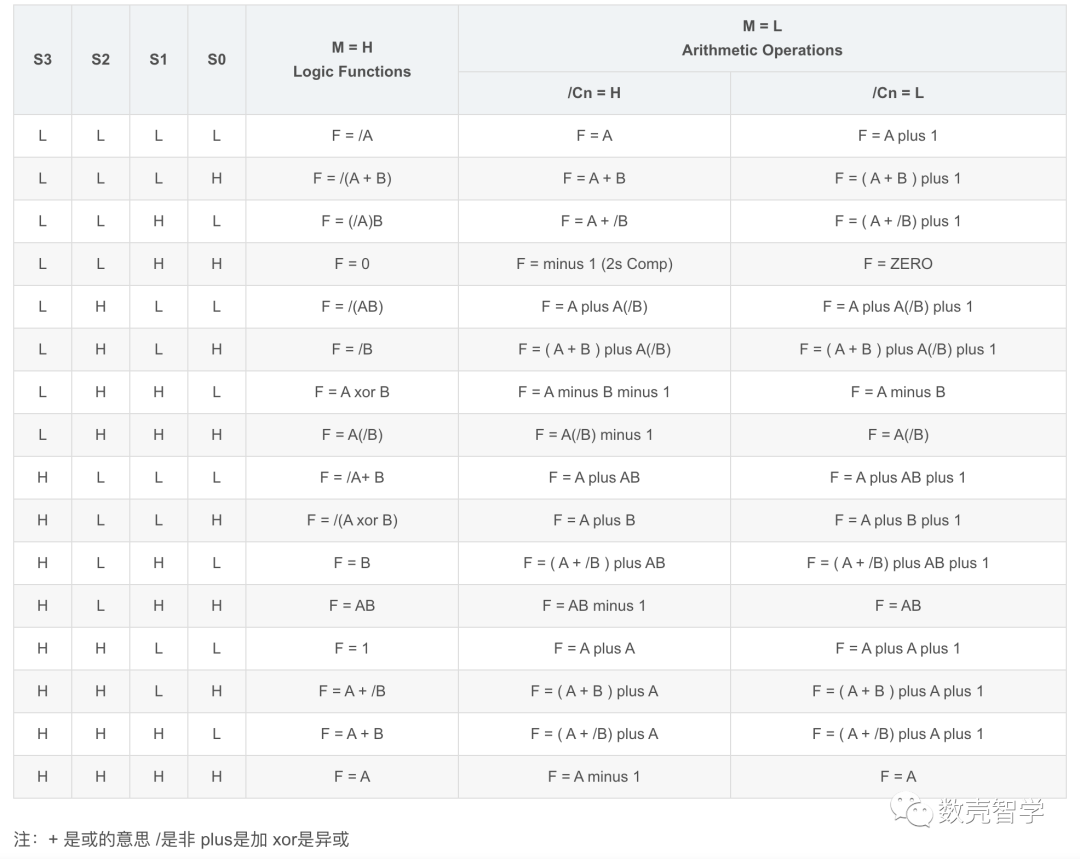

關(guān)鍵是將低4位芯片的Cn+4針腳連接高4位芯片的Cn針腳(如圖2),觀察SN7481芯片的邏輯(如圖1),低4位的Cn+4輸出作為高4位芯片的Cn輸入

低4位芯片設(shè)置M=H Cn=H進(jìn)行算術(shù)運(yùn)算,當(dāng)無(wú)需進(jìn)位時(shí)Cn+4 = H,則高4位芯片進(jìn)行如圖1的“Cn=H"的操作。當(dāng)?shù)?位計(jì)算之后需要進(jìn)位的時(shí)候,Cn+4 = L,則高4位芯片進(jìn)行如圖1的“Cn=L”的操作,實(shí)現(xiàn)高4位+1操作。如此完成8位的算術(shù)運(yùn)算。

圖1 SN74181芯片運(yùn)算邏輯圖

03實(shí)驗(yàn)過(guò)程

3.1 接線(xiàn)

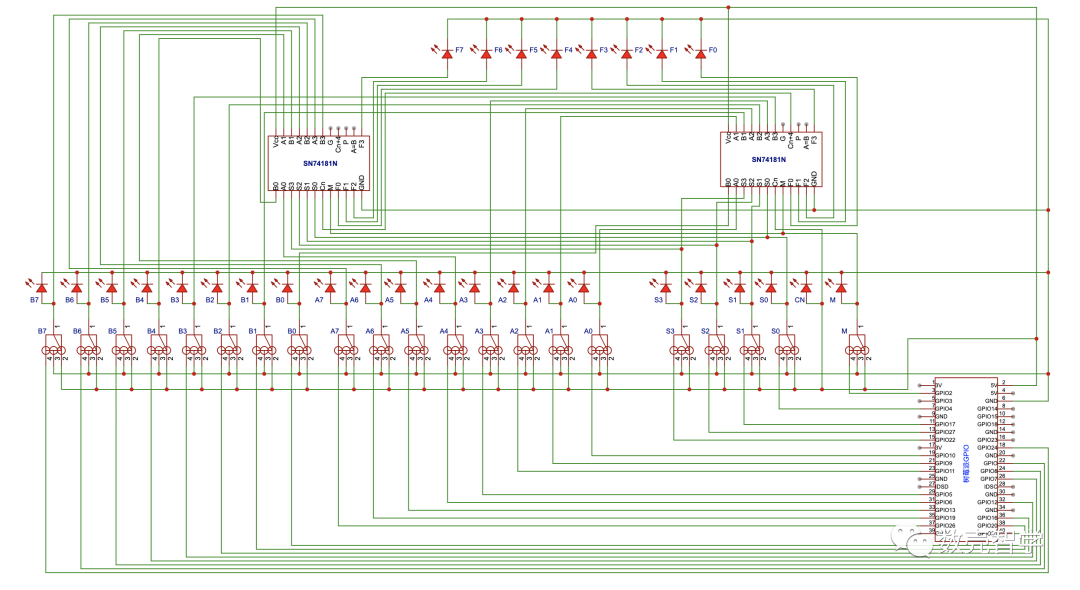

圖2 SN74181芯片級(jí)聯(lián)成8位ALU電路圖

說(shuō)明:

1、通過(guò)開(kāi)關(guān)選擇兩種模式可以測(cè)試芯片,開(kāi)關(guān)全部置4,由樹(shù)莓派GPIO控制針腳電壓;開(kāi)關(guān)置2表示給連接針腳高電壓;開(kāi)關(guān)置3表示給連接針腳低電壓

2、圖中紅色線(xiàn)為關(guān)鍵的連接線(xiàn)

3、請(qǐng)按照上圖進(jìn)行實(shí)際的連線(xiàn),樹(shù)莓派代碼也按照上圖針腳設(shè)置

3.2 實(shí)驗(yàn)步驟

3.3 實(shí)驗(yàn)代碼

04實(shí)驗(yàn)展示

-

芯片

+關(guān)注

關(guān)注

459文章

52192瀏覽量

436232 -

cpu

+關(guān)注

關(guān)注

68文章

11037瀏覽量

216007 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7630瀏覽量

90185 -

ALU

+關(guān)注

關(guān)注

0文章

33瀏覽量

13279

發(fā)布評(píng)論請(qǐng)先 登錄

兩個(gè)4位加法器級(jí)聯(lián)構(gòu)成一個(gè)8位加法器 verilog怎么寫(xiě)啊?!!

使用Robei利用verilog語(yǔ)言做ALU設(shè)計(jì)

8位alu設(shè)計(jì)

兩片4通道AD芯片如何級(jí)聯(lián)實(shí)現(xiàn)8通道的模擬信號(hào)采集

am335x evm外接兩個(gè)8位的nand flash

使用Robei利用verilog語(yǔ)言做ALU設(shè)計(jì)

請(qǐng)問(wèn)這兩個(gè)級(jí)聯(lián)有什么功能可以實(shí)現(xiàn)放大和濾波

如何利用兩個(gè)74HC595實(shí)現(xiàn)三個(gè)引腳實(shí)現(xiàn)數(shù)據(jù)的傳送

FPGA實(shí)現(xiàn)32位ALU軟核設(shè)計(jì)

兩個(gè)74ls164怎么連?74ls164聯(lián)級(jí)應(yīng)用電路

兩個(gè)74LS192級(jí)聯(lián)構(gòu)成兩位十進(jìn)制計(jì)數(shù)器

兩個(gè)74HC595D驅(qū)動(dòng)芯片控制三位數(shù)碼管顯示

用VHDL語(yǔ)言創(chuàng)建一個(gè)8位算術(shù)邏輯單元(ALU)

8位通用總線(xiàn)收發(fā)器和兩個(gè)帶拆分LVTTL端口反饋路徑和3態(tài)輸出的1位總線(xiàn)收發(fā)器SN74VMEH22501A-EP數(shù)據(jù)表

使用兩個(gè)SN74181芯片級(jí)聯(lián)實(shí)現(xiàn)8位ALU

使用兩個(gè)SN74181芯片級(jí)聯(lián)實(shí)現(xiàn)8位ALU

評(píng)論