I2C在小P以前接觸的設計中大多只用到400k的速率,EVB的設計中更經(jīng)常發(fā)現(xiàn)實現(xiàn)不了就降速到100k。現(xiàn)在突然再看看I2C,發(fā)現(xiàn)原來還有更高的速率規(guī)范,最高都已經(jīng)到5M了。

于是乎,小P又要把這兒挖一挖看一看,反正I2C以后也經(jīng)常會用到,不也得懂個所以然。

一、整體介紹

I2C最早是由Philips公司,現(xiàn)NXP公司開發(fā)的一種雙向兩線總線協(xié)議。其由于僅需要兩個引腳即可實現(xiàn)雙向多設備具有巨大的優(yōu)勢。截止至小P寫這篇推文時候,規(guī)范的最新版本已經(jīng)是《UM10204 v7》了。

在不同的應用架構(gòu)中,I2C可用于SMBus(System Management Bus)、PMBus(Power Management Bus)、IPMI(Intelligent Platform Management Interface)、DDC(Display Data Channel)和ATCA(Advanced Telecom Computing Architecture)。I2C往后的進一步演進MIPI I3C總線是可以向下兼容I2C(I3C全名叫Improved Inter-Integrated Circuit,強譯那就是改良型I2C),I3C可以提供更高的速率和更低的功耗。MIPI I3C總線在后續(xù)如果有涉及到的時候,再展開進一步學習了。

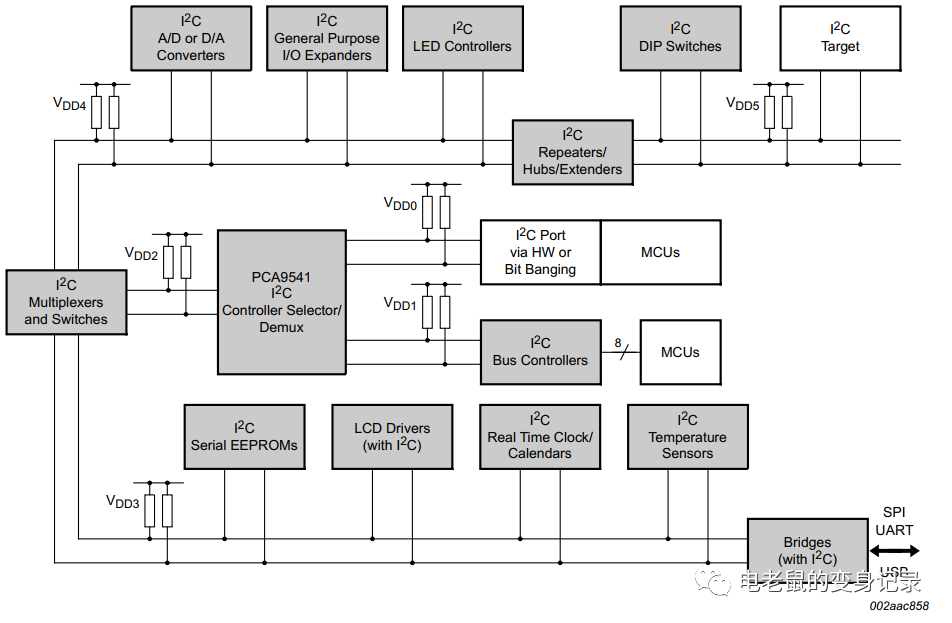

下圖是個典型的I2C總線應用場景。

I2C總線有且僅有兩個網(wǎng)絡走線,串行數(shù)據(jù)線SDA和串行時鐘線SCL。所有的I2C設備均是通過這兩根走線進行互連通信,每個設備均以唯一的地址被識別。大多數(shù)I2C設備可以既作為發(fā)送端也可作為接收端,個別I2C設備如LCD驅(qū)動器等不需要發(fā)送數(shù)據(jù)的設備,可以只用作接收端。

由于I2C總線需要“線與”邏輯用于判斷總線占用情況,因此SDA和SCL的接口必須使用外接上拉的OD驅(qū)動設計。

在只有單個I2C controller的應用場景中,如果SCL時鐘線上沒有會Stretch Clock的設備,那么controller的SCL輸出可以使用推挽(Push-pull)電路。

PS.在V7的規(guī)范里,I2C原來master/slave的描述更新為controller/target,和MIPI I3C規(guī)范保持一致。

二、總線速率

I2C總線按速率分為以下的模式:

| 模式 | 速率 | 方向 |

|---|---|---|

| Standard-mode(Sm) | 100kbit/s | 雙向 |

| Fast-mode(Fm) | 400kbit/s | 雙向 |

| Fast-mode Plus(Fm+) | 1Mbit/s | 雙向 |

| High-speed mode(Hs-mode) | 3.4Mbit/s | 雙向 |

| Ultra Fast-mode(UFm) | 5Mbit/s | 單向 |

可以發(fā)現(xiàn),3.4Mbps以下的速率,I2C總線的傳輸都是雙向的,但是在UFm模式下變成單向傳輸。這種情況可以應用在控制器發(fā)送數(shù)據(jù)給LCD屏幕驅(qū)動,不需要回傳數(shù)據(jù)的場景。

除了UFm模式以外,其他的模式均是和更低速率模式兼容的。

1、Fast-mode/ Standard-mode

(1)SDA和SCL的時序是適配的;

(2)SDA和SCL的INPUT為了消除毛刺,集成了施密特觸發(fā)器(Schmitt trigger);

(3)SDA和SCL的OUTPUT包含下降沿的斜率控制。(其實就是OD門只可通過配置調(diào)整下管的驅(qū)動能力)

2、Fast-mode Plus

(1)總線拓撲與F/S-mode保持一致,速率向下兼容;

(2)Fm+設備可提供比F/S-mode更大的驅(qū)動電流,從而實現(xiàn)更長/更重負載的鏈路。

(3)當總線上僅有Fm+設備時,更強的驅(qū)動能力和更大的上升/下降容忍度,使得可以通過降速實現(xiàn)更重負載電容鏈路應用。最小的LOW和HIGH電平時間需要滿足Fm+要求,上升時間不超過1us和下降時間不超過300ns。通過權(quán)衡總線速度和負載電容,可以提升最大負載電容的承受能力約10倍。

3、High-speed mode

(1)總線拓撲與F/S-mode、Fm+保持一致,速率向下兼容;

(2)為了實現(xiàn)3.4MBbps的通信速率,SCLH的OUTPUT使用了OD下拉+電流源上拉的組合電路,SDAH與其他保持一致;僅在Hs-mode模式下,僅有一個controller的電流源上拉會被使用;

(3)在Hs-mode的多控制器系統(tǒng)中,仲裁和時鐘同步不會使用,這能加速位處理的能力;

(4)Hs-mode controller發(fā)出的SCL波形高低電平時間比是1:2,進而減輕了建立/保持的要求;

(5)Hs-mode controller可以在內(nèi)部集成一個bridge。在Hs-mode傳輸時將F/S-mode設備的SDA、SCL和Hs-mode設備的SDAH(high-speed serial data)、SCLH(high-speed serial clock)斷開。通過這種方式可以減小SDAH和SCLH總線上的負載電容,從而提高上升時間和下降時間;這個在下面的圖示可以非常直觀清晰的看到;

(6)SDAH和SCLH的INPUT集成了施密特觸發(fā)器;

(7)SDAH和SCLH的OUTPUT包含下降沿的斜率控制。

當總線電容>100pF時,Rp可以被替換為外部電流源上拉,從而提高上升時間滿足要求。

Rs電阻作為可選項,用于保護IO接口不被過高毛刺打壞,并且可以優(yōu)化過沖震蕩。

4、Ultra Fast-mode

針對UFm,不過多展開學習了。需要注意的是,UFm模式下的I2C,USDA和USCL均是采用的Push-pull輸出,最高可達到5Mbps。

三、BIT/BYTE

接下來我們著重看下I2C的一些細節(jié)點,

首先就是I2C信號的采樣方式。I2C的數(shù)據(jù)有效性要求SDA數(shù)據(jù)線在SCL時鐘線高電平必須是穩(wěn)定的(也就是在SCL高電平采樣,不是邊沿采樣),SDA數(shù)據(jù)線的電平翻轉(zhuǎn)僅允許在SCL時鐘線低電平時,如下圖。

然后就是I2C總線的數(shù)據(jù)傳輸?shù)拈_始和結(jié)束特征,這個很簡單。就是在SCL時鐘線高電平時,SDA數(shù)據(jù)線下降表示開始,SDA數(shù)據(jù)線上升表示結(jié)束,如下圖。S condition和P condition僅由控制器(也就是原master)發(fā)出,當S condition發(fā)出后,總線則被占用。在P condition發(fā)出一定時間間隔后,總線會被認為釋放。

再接著是I2C的byte格式,這里有很有趣的幾個點,這個就是OD門“線與”邏輯的有趣應用了。詳細的圖示可以看底下的圖:

1、SDA數(shù)據(jù)線上的byte必須是8位長,并且開頭一定是一個MSB(Most Significant Bit,這可不是你們以為嗶嗶)。當transmitter發(fā)送完一個8位的byte后,會將SDA數(shù)據(jù)線釋放到高電平。然后receiver完整接收到這個8位byte后,將會在下一個(第9個)時鐘周期高電平來之前,將SDA數(shù)據(jù)線拉低到低電平(ACK信號)。通過這個方式告訴transmitter我接收到數(shù)據(jù)了。如果沒有成功接收到數(shù)據(jù),或是數(shù)據(jù)不識別,那么在第9個時鐘周期高電平時,receiver需要釋放SDA數(shù)據(jù)線為高電平(NACK)。Controller若接收到NACK,則可以發(fā)出STOP condition結(jié)束數(shù)據(jù)傳輸或repeated START condition進行新的數(shù)據(jù)傳輸。

2、當target設備正在忙,沒空接收數(shù)據(jù)時,target可以將SCL時鐘線拉低,也就是我們說的hold住SCL。這種情況下,controller會進入等待模式。當target忙完了,就可以釋放SCL時鐘線,然后才會進行下一個byte的數(shù)據(jù)發(fā)送和接收。

I2C的數(shù)據(jù)傳輸是基于地址的,所以完整的一個I2C數(shù)據(jù)傳輸是包含7個地址位,1個讀寫位,再接著數(shù)據(jù)位和ACK位,如下圖。在S(START condition)后面緊接著的就是7位Addr和1位RW。

值得注意的是,由于Hs-mode下的SCLH的高低電平周期是1:2,所以Hs-mode的傳輸和F/S- mode有些許差異,下圖可以體現(xiàn)。

其實在學習I2C的時候,會有一個很容易迷惑的點,就是controller和target的關(guān)系,還有就是transmitter和receiver的關(guān)系。規(guī)范中對于這些的定義是如下

如果還是梳理不清楚,那么接下來的這段講解,應該可以進一步幫助理解

1、Controller-transmitter發(fā)送數(shù)據(jù)給targer-receiver。數(shù)據(jù)傳輸?shù)姆较虿恍枰兓瑃arget-receiver在接收到每個byte時需要反饋ACK。

2、Controller讀取target的數(shù)據(jù),先由controller-tranmitter發(fā)送地址和讀位,當target-receiver反饋ACK后,隨即調(diào)整方向。controller-tranmitter變?yōu)閏ontroller-receiver,target-receiver變?yōu)閠arget-tranmitter。第一個ACK信號由target在接收到地址后產(chǎn)生,后續(xù)的ACK均由controller產(chǎn)生。STOP condition(P)是在controller發(fā)出一個not-acknowledge(NACK)后,由controller發(fā)出STOP condition(P)。

3、還有一種混合格式(Combined format),在一次傳輸過程中,地址沒有變化,僅是傳輸方向有變化。那么只需要重發(fā)一次repeated START condition(Sr)和同樣的target地址,但是讀寫位翻轉(zhuǎn)。在controller-receiver發(fā)送repeated START condition前,會發(fā)送NACK。

為了支持更多的設備可以同時掛在I2C總線上,7-bit地址擴展到了10-bit地址。7-bit/10-bit設備可以同時掛在一個I2C總線上。他們的區(qū)別就是,10-bit地址需要占用兩個byte才能完成地址的傳輸。

第一個byte規(guī)定為1111 0XXR/W

第二個byte則定為XXXX XXXX

這10個X組成了10-bit地址,R/W決定了讀寫方向。

寫方向與7-bit地址的模式類似,在完成兩個地址byte發(fā)送后,發(fā)送8位數(shù)據(jù)。

讀方向則和7-bit地址的Combined format有點類似,在完成兩個地址byte發(fā)送后,通過repeated START condition(Sr),再發(fā)送一次一個byte地址后(讀寫位需要配置為1 Read),開始反向讀取數(shù)據(jù)。這個時候不需要發(fā)第二個byte的地址,因為匹配的target設備會記憶其被定位。若讀寫位配置為0 Write,則需要繼續(xù)發(fā)送第二個byte的地址去進行配對。

Hs-mode和F/S-mode的傳輸格式也有少許區(qū)別

四、電氣約束和時序約束(瘋狂的貼圖時間)

1、S-/F-/Fm+設備約束

設備需要滿足其最高速率,但是通過時鐘同步,stretch SCL的低電平的方式,可以實現(xiàn)降速。

2、Hs-mode設備約束

一般意義上的START condition(S)在HS-mode中不存在,而是以repeated START condition(Sr)開頭。地址位、讀寫位、ACK位及數(shù)據(jù)位的時序都是一樣的,但是第一個SCLH的上升時間很特殊地放寬了。由于ACK后的第一個SCLH,上升沿是靠外部上拉電阻提供的驅(qū)動能力(第一個SCLH的時候,內(nèi)部上拉電流源未開通工作)。

通過內(nèi)部依次產(chǎn)生的100ns高電平和200ns低電平,Hs-mode controller滿足外部3.4MHz的時序要求(包含上升/下降時間)。因此,Hs-mode controller可以采用10MHz基頻或倍頻來產(chǎn)生SCLH信號。

對于Hs-mode來說,時序要求也與總線上負載電容相關(guān)。當總線負載電容小于100pF時,總線可能可以運行在最高3.4Mbps速率下。當負載電容持續(xù)增大時,比特率會開始逐步降低。當總線負載電容等于400pF時,則能達到的最高速率應該是1.7Mbps。總線負載電容在100-400pF之間的,則時序參數(shù)需要線性的插值。

SDAH和SCLH的上升/下降時間與其在傳輸線上的最大傳播時間一致,以防止末端開路反射。

I2C的鏈路時序計算一般風險較低。按照3.4MHz計算,一個周期大概是300ns。假定PCB的板材是FR4,DK 4.5,這樣換算下來那么1ns大概是5.57inch走線的時延。且SDA的電平翻轉(zhuǎn)動作是在SCLH低電平期間,也就是200ns這段,可以等效約1000多inch,已經(jīng)遠遠超出可能的應用場景了。

這般梳理下來,小P覺得I2C的基本應用,配合做SI分析已經(jīng)是足夠了。如果說后面遇到需要進一步學習的時候,再補充了。

-

接口

+關(guān)注

關(guān)注

33文章

8924瀏覽量

153153 -

I2C總線

+關(guān)注

關(guān)注

8文章

408瀏覽量

61884 -

總線協(xié)議

+關(guān)注

關(guān)注

0文章

128瀏覽量

15163 -

SDA

+關(guān)注

關(guān)注

0文章

125瀏覽量

28683 -

SCL

+關(guān)注

關(guān)注

1文章

242瀏覽量

17450

發(fā)布評論請先 登錄

STM32學習筆記_I2C詳解(可下載)

I2C總線通信原理 如何設計I2C總線電路

I2C總線的優(yōu)缺點分析

I2C總線與Arduino的接口示例

I2C總線的工作模式介紹

I2C總線協(xié)議詳細解析

I2C總線故障排除技巧

I2C總線與單片機的連接

I2C總線應用實例分析

I2C總線與SPI總線的比較

I2C總線上拉電阻阻值如何確定?

I2C總線學習筆記

I2C總線學習筆記

評論