在為 5G 應用設計電源系統時,設計人員必須考慮此類應用固有的寬頻率范圍,從穩壓器中的中頻到 FPGA

內核中的高時鐘頻率。這種端到端的全雙工設計對于優化電源、電源轉換和配電過程的性能至關重要。

本文重點介紹如何實現高效的供電網絡 (PDN) 設計。PDN 由連接到電壓軌和接地軌的所有組件組成,包括電源和接地層布局、無源元件、IC

以及連接或耦合到主電源軌的任何其他銅質元件。在設計過程中,必須考慮 PDN 中組件的寄生行為,因為這會影響整個系統行為。

旁路和去耦電容是 PDN 中必不可少的元件。因此,PDN 設計中的電容器選擇和放置需要特別考慮,因為電容不足會導致系統不穩定和性能問題。

d耦合和bypass電容器的重要性

旁路電容器用于穩壓器模塊(VRM),通過濾除輸入紋波電流為轉換器提供低阻抗電壓源。它們還可以補償電源耦合到 IC

接地連接產生的開關噪聲產生的潛在接地反彈電壓。

在降壓穩壓器的輸出端,去耦電容的主要目的是保證輸出電壓(V外) 通過降低輸出電壓紋波 (?V

保持恒定外).因此,選擇電容以限制?V外到負載輸入規格設定的幅度,同時還考慮與轉換器負載突然變化引起的電壓變化相關的限制。

bypass電容器的放置策略

旁路電容器是確保降壓轉換器可靠運行的最重要元件。放置IC后,旁路電容器是布局中放置的第一個元件,必須在IC放置后立即布線。由于不正確的布線而導致的額外寄生電感與轉換器的開關相結合,會產生過大的電壓尖峰,這可能導致IC故障。

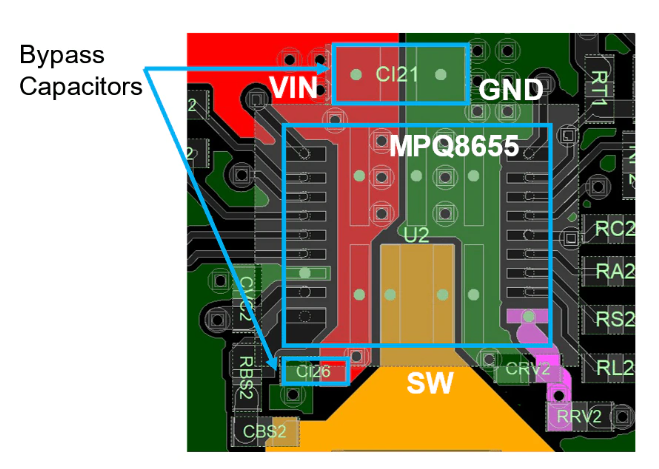

圖1顯示了負載點(PoL)轉換器旁路電容(CI21和CI26)的最佳放置。

旁路電容器環路中產生的寄生電感可分為兩部分:電容器的寄生電感和電感和IC之間的電流路徑布局產生的電感。由于PCB布局幾何形狀產生的電感相對于總電感比固有電容器電感更重要,因此設計工作應重點關注。

為了最小化環路電感,旁路電容應盡可能靠近IC放置。還應使用過孔將電容器的焊盤直接連接到電源 (PWR) 和接地 (GND) 網絡,盡可能靠近 IC 引腳,從而最大限度地減少電流路徑。

選擇d耦合****電容器

所需的去耦電容類型和數量取決于電容在頻域中的行為。去耦電容設計用于最大限度地降低VRM的?V外這是由轉換器的開關操作產生的,以及以高頻向FPGA/ASIC提供瞬時電流,直到電源可以響應。因此,必須考慮整個工作頻譜。

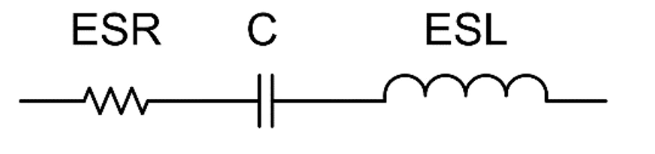

基本電容模型包括三個關鍵要素:電容 (C)、等效串聯電阻 (ESR) 和等效串聯電感 (ESL),如圖 2 所示。

圖2這就是電容器等效電路模型的樣子。來源:單片電源系統

ESR由元件中導電元件的阻抗引起,并決定了諧振頻率處的最小阻抗。ESL由流過電容器的電流的影響產生,并決定諧振頻率。諧振頻率是電容器阻抗曲線中元件開始表現得像電感器的點,阻抗與頻率成比例地增加。

在低頻(高達50 kHz)下,降壓轉換器具有低阻抗。然而,降壓轉換器在高頻下的阻抗主要是感性的。添加到PCB中的每個電容器都會降低給定頻率下的PDN阻抗,這意味著精確的放置和選擇可以實現設定的目標阻抗曲線。因此,通過從檢測點進行測量,可以在給定頻率下滿足目標阻抗。

目標阻抗(Z 目標 ) 可以用公式 1 計算:

Z 目標 = ?V 噪聲 /我 TRANSIENT_MAX (1)

其中 ?V噪聲是最大允許紋波電壓和ITRANSIENT_MAX是轉換器必須提供的最大負載步長。還可以計算所需的輸入和輸出電容。

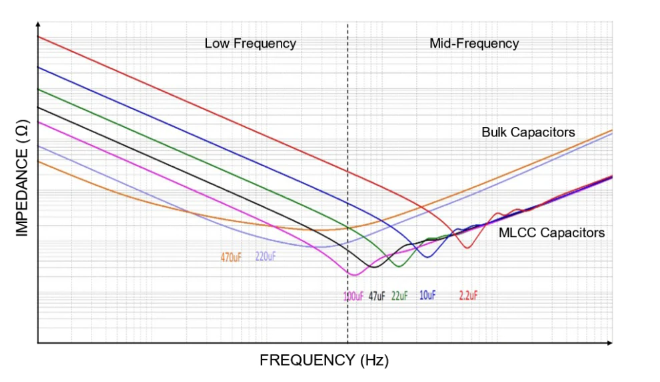

為了將阻抗保持在目標水平以下,必須約束設計并降低寄生電感。大容量電容器在高達 10 MHz 的頻率范圍內降低阻抗,而 MLCC 電容器在中高頻范圍內降低阻抗。

圖3顯示了大容量電容器和MLCC電容器的阻抗頻率特性。

圖3圖中顯示了典型大容量電容器和MLCC電容器的阻抗頻率特性。來源:單片電源系統

d耦合電容器的布局****策略

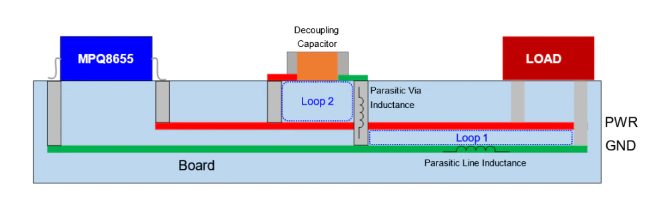

一旦計算和分析了電容,去耦電容在PCB中的最佳位置就很重要。布局幾何形狀、通孔布局和距離主要影響電源層環路電感,從而影響PDN響應。圖4顯示了轉換器、去耦電容和負載產生的電流環路。由于這些回路是結構固有的并且不可避免,因此盡可能減少這些回路至關重要。

圖4電流環路由轉換器、去耦電容和負載產生。來源:單片電源系統

環路1是水平環路分量,由轉換器和去耦電容之間的距離決定。環路 2 是垂直環路組件,由將電容器連接到電源層的通孔高度決定。電源層通常放置在PCB的最內層。

該測試板在雙相操作中使用兩個PoL轉換器,V外0.9 V 和最大輸出電流 (I OUT_MAX ) 的 50 A,這是 ASIC/FPGA 電源軌的通用值。可以使用測試板進行不同場景的仿真,以確定電容器的最佳放置。

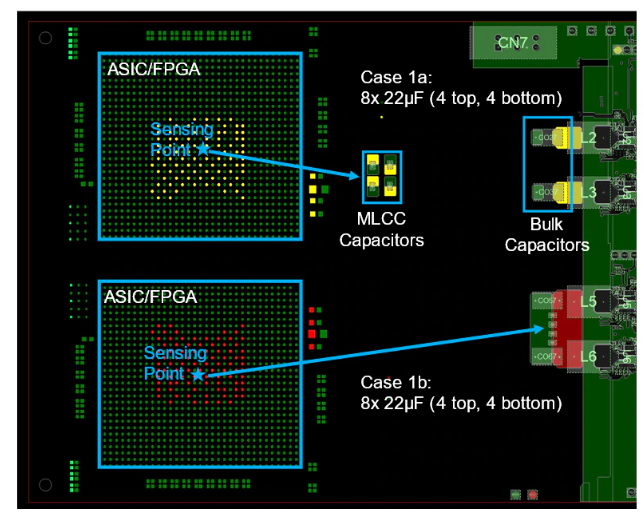

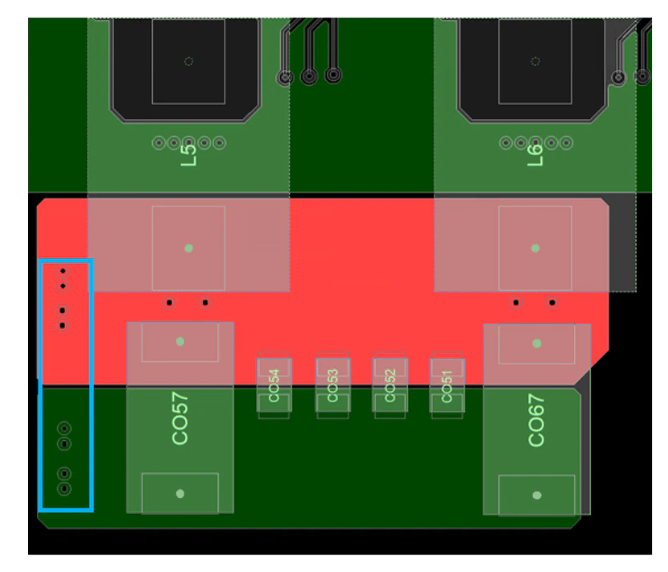

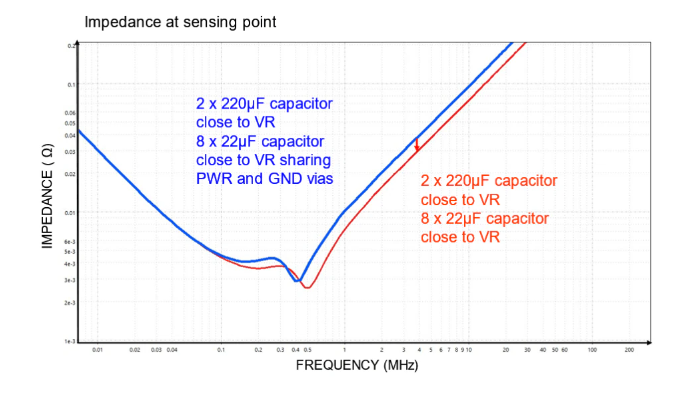

為了評估最佳電容布局,在ASIC/FPGA中心的板級檢測點測量阻抗。使用公式1的分析,可以使用8 x 22 μF MLCC電容和2 x 220 μF大容量電容實現VRM阻抗曲線。為了保持穩壓器的穩定性,大容量電容器緊跟在輸出電感器之后。測試板考慮了22 μF MLCC電容在外殼1a和案例1b下的不同位置(見 圖5 )。

圖5測試板說明了去耦電容的放置。來源:單片電源系統

在情況1a中,MLCC電容器放置在ASIC/FPGA之前,從而減小了環路1的尺寸。在案例1b中,MLCC電容器放置在大容量電容器旁邊,因此MLCC電容器與傳感點之間的距離是案例1a的兩倍。

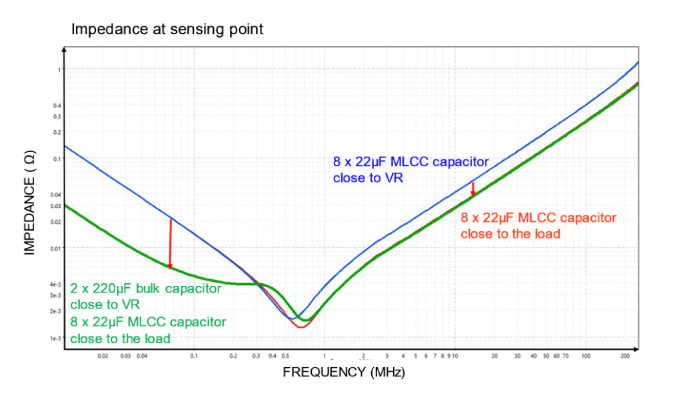

圖6顯示了將大容量電容放置在降壓轉換器附近時的仿真結果,這導致低頻范圍內的阻抗降低(綠色跡線)。將MLCC電容器放置在靠近負載的位置(紅色跡線)可降低高頻范圍內的阻抗,從而使電容器能夠更有效地提供FPGA/ASIC負載所需的瞬時電流階躍。

圖6顯示了回路 1 大小變化的測試結果。來源:單片電源系統

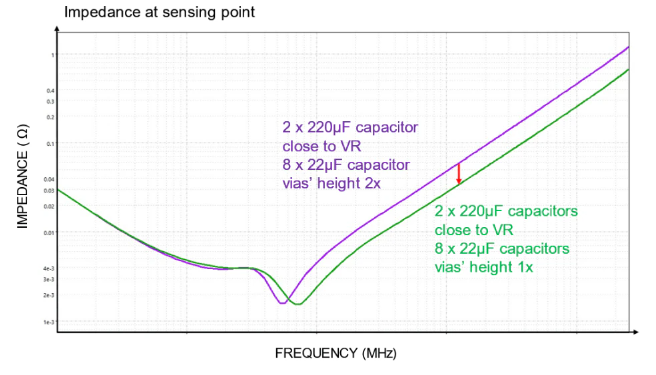

傳統設計指南建議將去耦電容放置在PCB的底部,以減小電路板空間,從而提高功率密度。然而,將電容器放置在電路板底部需要更長的過孔才能到達ASIC/FPGA所在的另一側。這增加了垂直路徑的大小,如圖 4 所示,如環路 2 所示。

通過將過孔高度加倍進行了額外的測試,以分析增加環路 2 尺寸的效果。圖7顯示了環路2尺寸變化的測試結果,其中觀察到類似的趨勢,通孔高度增加導致中高頻范圍內的阻抗增加。

圖7顯示了環路 2 大小變化的測試結果。來源:單片電源系統

最小化去耦電容中的環路電感與電容數量同樣重要。有兩種方法可以實現降低環路電感。第一種方法是減小IC和電容器之間的水平距離。第二種方法是通過將電源層和接地層放置在上層來降低通孔高度。

在小范圍內放置多個元件以減少電路板空間通常會導致電容共享過孔。當電容器共享過孔時,如果不考慮通孔定位和數量,正確選擇和定位的整體改進可能會顯著降低甚至可以忽略不計。因此,通孔布局設計也是降低環路阻抗的關鍵。

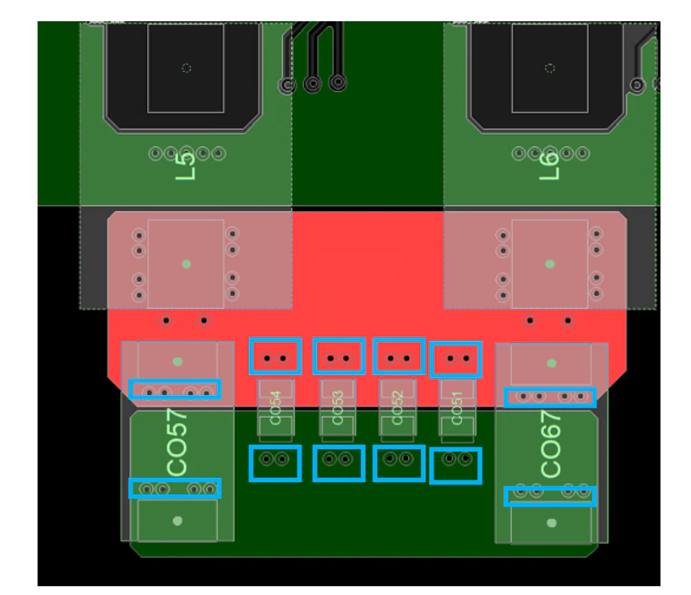

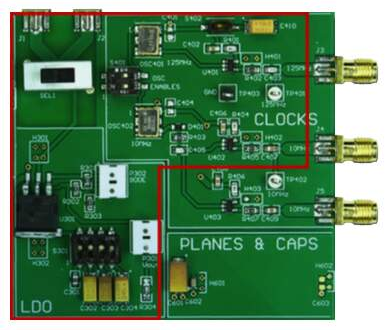

為了分析過孔定位和數量的影響,使用電路板進行了第二次測試,通過放置兩個通用設計建議。在第一個設置中,每個電容都有自己的一組通孔連接到電源和接地層(見 圖8 )。

圖8每個電容器都有自己的一組電源和接地層過孔。來源:單片電源系統

在第二種設置中,所有電容共用一組位于平面一側的過孔(見 圖9 )。

圖9所有電容器共用一組位于平面一側的過孔。來源:單片電源系統

圖10顯示了通孔放置變化的測試結果。將過孔放置在遠離電容的位置會增加環路1的尺寸,從而增加環路電感。因此,過孔共享增加了高頻阻抗。

圖10顯示過孔放置變化的測試結果。來源:單片電源系統

根據后續測試,建議在0805和0603封裝中,大容量電容器至少使用4個電源通孔和4個接地過孔,MLCC電容器至少使用2個電源過孔和2個接地過孔。過孔應盡可能靠近電容器放置。

整個 PDN

在設計 FPGA/ASIC 系統或任何需要高電流和快速負載瞬變的電路時,必須全面考慮 PDN,以優化系統性能。快速負載階躍,例如在FPGA中觀察到的階躍,會在整個電路中產生強大的高頻電流。在如此高的頻率下,PDN 中通常可以忽略的寄生元件可能會突然導致設備故障。設計人員必須注意確保 PDN 的寄生元件最小化。

本文重點介紹如何使用PoL轉換器降低VRM去耦電容中的電流路徑引起的寄生阻抗。為了獲得最佳性能,垂直軸和水平軸上的電流環路應盡可能短。將電流環路放置在盡可能靠近負載的位置,并將電源走線保持在外層,可有效減少通孔長度。

適當的過孔放置也是降低寄生電感的關鍵。因此,建議在盡可能靠近每個電容器焊盤的位置放置多個過孔,以減少過孔的總寄生電感以及流過每個過孔的電流。

-

電源

+關注

關注

185文章

18275瀏覽量

255025 -

轉換器

+關注

關注

27文章

8961瀏覽量

150757 -

電壓

+關注

關注

45文章

5698瀏覽量

117302 -

PDN

+關注

關注

0文章

84瀏覽量

23005 -

供電網絡

+關注

關注

0文章

17瀏覽量

7717

發布評論請先 登錄

DC–DC 轉換器為 GSPS ADC 提供高效輸電網絡

DC–DC轉換器為GSPS ADC提供高效輸電網絡

GSPS ADC搭配DC-DC轉換器,提高輸電網絡效能

通過輸電網絡合探討GSPS ADC性能

如何實現智能電網自動化?

如何利用Cyclone FPGA實現智能電網自動化?

如何優化供電網絡?

智能電網如何實現

電源系統優化——深入解讀優化高速數據轉換器的配電網絡

使用直流壓降分析優化PDN性能

震旦ad330pdn

如何實現高效的供電網絡 (PDN) 設計

如何實現高效的供電網絡 (PDN) 設計

評論