基于芯動(dòng)神州ADSD1299設(shè)計(jì)的可穿戴式腦電采集前端,具有采集精度高、體積小、功耗低、抗干擾性強(qiáng)等特點(diǎn)。采用ADSD1299內(nèi)部集成的可編程放大器(PGA)實(shí)現(xiàn)微弱信號(hào)的放大。為了消除干擾,使用限幅濾波預(yù)處理電路和ADSD1299內(nèi)部集成的偏置驅(qū)動(dòng)放大器。實(shí)驗(yàn)測(cè)試表明,該腦電采集前端設(shè)計(jì)能較好地把微弱的腦電信號(hào)提取出來,并且具有較好的抗干擾能力和實(shí)用價(jià)值。

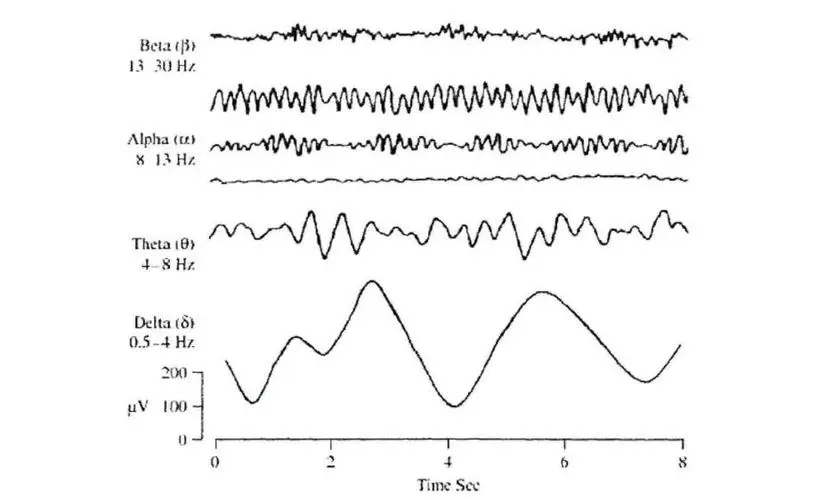

腦電圖(EEG)是由大腦神經(jīng)元活動(dòng)產(chǎn)生的電位合成,它包含了豐富的大腦活動(dòng)信息。腦電圖在腦部疾病的醫(yī)學(xué)診斷、功能恢復(fù)、疲勞駕駛的腦電活動(dòng)監(jiān)測(cè)、腦-機(jī)接口(BCI)以及其他腦科學(xué)研究中都有廣泛應(yīng)用。對(duì)于腦電信號(hào)的研究離不開腦電信號(hào)的采集,而腦電信號(hào)的采集則依賴于腦電采集系統(tǒng)。傳統(tǒng)的腦電采集系統(tǒng)雖然能夠在采集精度上滿足醫(yī)療和研究的需求,但其體積大、操作復(fù)雜、功耗高等缺點(diǎn)限制了其應(yīng)用范圍。因此,設(shè)計(jì)出一種體積小、功耗低、操作方便的腦電信號(hào)采集系統(tǒng)具有重大的實(shí)際意義和應(yīng)用價(jià)值。由于腦電信號(hào)極其微弱,加上人體阻抗的特性、外部和內(nèi)部的干擾等因素,傳統(tǒng)的腦電采集系統(tǒng)需要通過復(fù)雜的放大濾波電路設(shè)計(jì)來滿足腦電信號(hào)采集的需求。然而,這樣的設(shè)計(jì)會(huì)導(dǎo)致電路板體積過大、功耗高,不利于實(shí)現(xiàn)采集系統(tǒng)的便攜化。

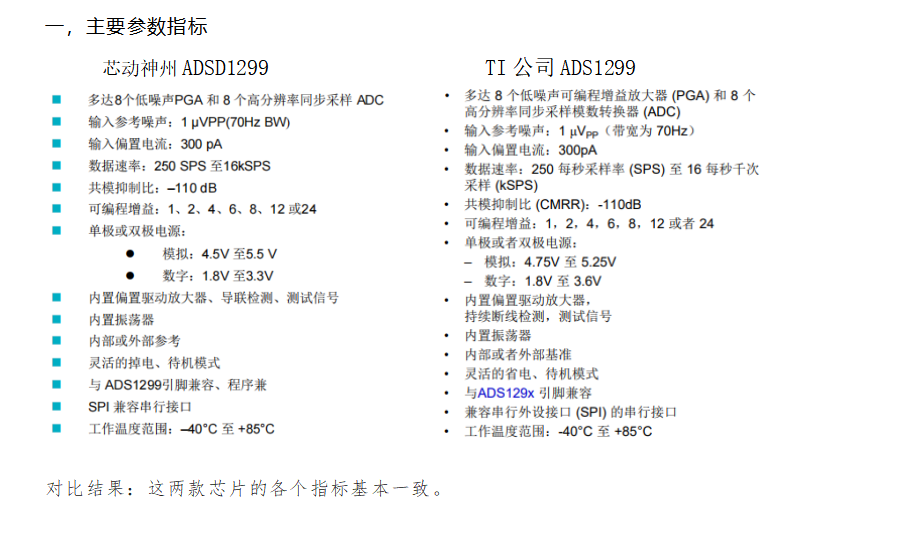

芯動(dòng)神州推出的專門用于腦電信號(hào)采集的模數(shù)轉(zhuǎn)換芯片ADSD1299,以高精度、便攜式、低功耗的腦電采集系統(tǒng)研制為背景,采用該款芯片作為核心器件設(shè)計(jì)出可穿戴式腦電信號(hào)采集系統(tǒng)前端。

可穿戴式腦電采集系統(tǒng)設(shè)計(jì)方案

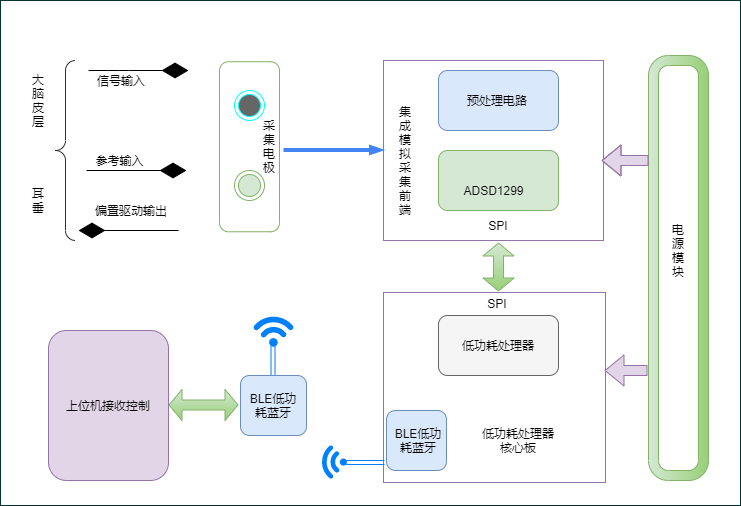

圖1 穿戴式腦電采集系統(tǒng)框圖

可穿戴式腦電信號(hào)采集設(shè)備由若干部分組成,包括腦電導(dǎo)聯(lián)接口、ADSD1299集成模擬采集前端、核心板控制模塊、BLE藍(lán)牙模塊、電源模塊和上位機(jī)部分組成,如圖1所示。

該系統(tǒng)是一個(gè)低功耗的嵌入式處理系統(tǒng),核心板控制模塊通過低功耗藍(lán)牙BLE模塊與上位機(jī)進(jìn)行通信,根據(jù)上位機(jī)的指令控制ADSD1299進(jìn)行腦電信號(hào)的模數(shù)轉(zhuǎn)換,并將轉(zhuǎn)換后的腦電信號(hào)數(shù)據(jù)通過藍(lán)牙發(fā)送到上位機(jī)。該系統(tǒng)解決了傳統(tǒng)腦電采集系統(tǒng)在時(shí)間和空間上的局限性,滿足了腦電采集所需要的便攜式、可移動(dòng)、低功耗以及實(shí)時(shí)性等特點(diǎn)。該系統(tǒng)中模擬前端部分是保障系統(tǒng)整體性能的關(guān)鍵,芯動(dòng)神州的ADSD1299為核心器件,其具有如下突出的特性:

具有8個(gè)低噪聲可編程放大器(PGA,放大倍數(shù)1~24倍可調(diào))與8個(gè)同步采樣模/數(shù)轉(zhuǎn)換器(ADC),模/數(shù)轉(zhuǎn)換速率介于250 S/s~16 kS/s之間,不超過8 kS/s時(shí)其精度為24 bit。

每個(gè)通道的功耗僅有5 mW,共模抑制比(CMRR)高達(dá)-110 dB,直流輸入阻抗高達(dá)1 000 MΩ。

內(nèi)置偏置驅(qū)動(dòng)放大器和持續(xù)斷電檢測(cè)(LEAD-OFFDetection)功能。

這些特性保證了加入很少的元器件即可搭建腦電信號(hào)模擬采集前端。

ADSD1299內(nèi)部結(jié)構(gòu)描述

ADSD1299的輸入端采用差分方式輸入,每個(gè)輸入端都集成有EMI濾波器,能有效地抑制外部射頻干擾。此外,它具有靈活的路由交換器(MUX),可以將任何輸入連接到放大器(PGA)的輸入端。同時(shí),它還集成有持續(xù)斷電檢測(cè)(Lead Off)電路,可以隨時(shí)監(jiān)測(cè)電極是否斷開。內(nèi)部集成了8路并行的PGA和ADC,可以提供很高的采集轉(zhuǎn)換精度。內(nèi)部還集成有偏置驅(qū)動(dòng)放大器,可以有效抑制共模干擾噪聲。采用SPI串行通信方式設(shè)置內(nèi)部控制用寄存器并輸出數(shù)字信號(hào),當(dāng)芯片完成一次采集時(shí),芯片會(huì)拉低引腳來通知處理器可以通過SPI讀取數(shù)據(jù)。

集成模擬前端腦電檢測(cè)電路設(shè)計(jì)

腦電檢測(cè)電路基于芯動(dòng)神州公司推出的集成模擬前端芯片ADSD1299進(jìn)行設(shè)計(jì)。ADSD1299內(nèi)部器件噪聲低于1uV,并且具備腦電采集所需的全部常用功能。并且以通道正常運(yùn)行時(shí)消耗 5 mW 的低功耗特性和高集成度特點(diǎn),能夠大幅度縮小板級(jí)空間,顯著降低整體成本,構(gòu)建可擴(kuò)展的腦電采集系統(tǒng)。針對(duì)腦電信號(hào)微弱(0.5 uV~100 uV)的特性,傳統(tǒng)的采集前端通常由模擬抗混濾波器、多級(jí)放大電路和陷波電路等來提高信號(hào)的信噪比,這也是導(dǎo)致其體積大,不利于實(shí)現(xiàn)便攜式設(shè)計(jì)的主要原因。

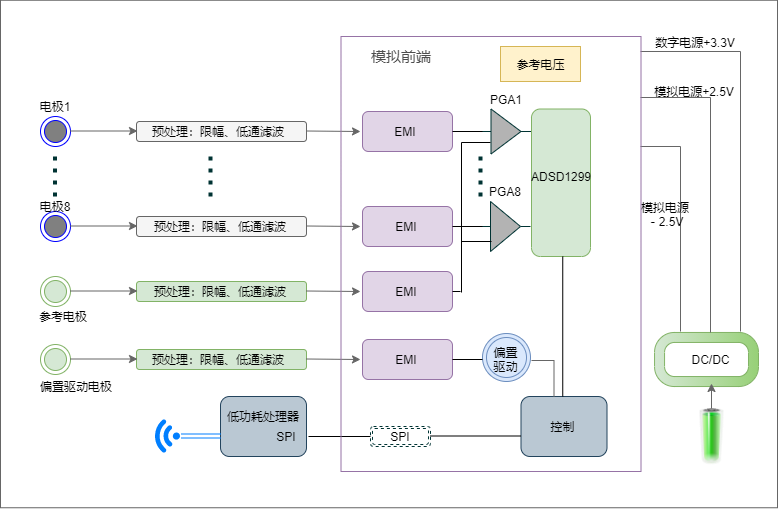

圖2前端電路設(shè)計(jì)結(jié)構(gòu)框圖

由于ADSD1299在采樣頻率不超過8 kHz時(shí)模數(shù)轉(zhuǎn)換精度達(dá)到24位,再結(jié)合其集成的具有高共模抑制比的差分輸入可編程增益放大器(PGA),在前端設(shè)計(jì)的模擬側(cè)只保留了抗混濾波電路。而基線漂移、陷波等處理根據(jù)應(yīng)用需要在數(shù)字側(cè)實(shí)現(xiàn),而且基于過采樣技術(shù)采用二階無源RC濾波電路實(shí)現(xiàn)抗混濾波,大大簡(jiǎn)化前端電路設(shè)計(jì)。其設(shè)計(jì)結(jié)構(gòu)框圖如圖2所示。

ADSD1299為差分輸入,其共模抑制比(CMRR)高達(dá)-110 dB,且其直流輸入阻抗高達(dá)1 000 MΩ,再配合閉環(huán)偏置驅(qū)動(dòng)電路設(shè)計(jì),能夠很好地保證系統(tǒng)的抗干擾要求;ADSD1299內(nèi)部含有8個(gè)低噪聲的可編程增益放大器(PGA)和8個(gè)同步采樣模/數(shù)轉(zhuǎn)換器(ADC),A/D轉(zhuǎn)換精度高達(dá)24 bit,當(dāng)VREF=4.5 V時(shí)其信號(hào)電壓的分辨率為:

VLSB=VREF /(223-1)=0.536uV

如果再將PGA可編程增益控制考慮進(jìn)去則其信號(hào)電壓分辨率可以達(dá)到0.053 6 uV。

預(yù)處理電路設(shè)計(jì)

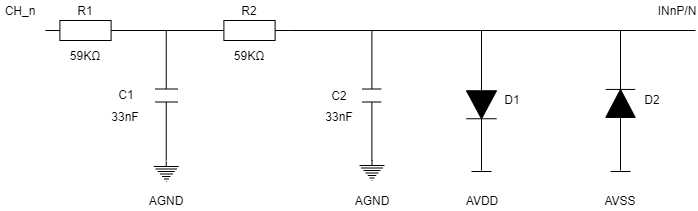

圖3信號(hào)預(yù)處理電路

由于腦電信號(hào)頻率只有0.5~100 Hz,實(shí)驗(yàn)分析的有效范圍一般在0.5~30 Hz,在模數(shù)轉(zhuǎn)換前必須經(jīng)過低通抗混濾波的預(yù)處理。我們針對(duì)每個(gè)通道設(shè)計(jì)了預(yù)處理電路,如圖3所示, 該電路由二階無源RC低通濾波和限幅電路組成。

基準(zhǔn)電壓電路

對(duì)于ADC的基準(zhǔn)電壓選擇,既可以選擇內(nèi)部基準(zhǔn)電壓,也可以選擇外部基準(zhǔn)電壓。為了減小電路規(guī)模,使用ADSD1299內(nèi)部基準(zhǔn)電壓VREF=4.5V,詳細(xì)資料請(qǐng)查看數(shù)據(jù)手冊(cè)。基準(zhǔn)電壓是將VREFN與AVSS連接起來并加上限頻電容由AVSS產(chǎn)生的,限頻電容的作用是使基準(zhǔn)電壓的輸入噪聲不會(huì)對(duì)系統(tǒng)產(chǎn)生干擾,使得頻率帶寬至少限制在10 Hz以內(nèi)。

偏置驅(qū)動(dòng)電路

A=2*ZF/RCM

其中,ZF為:

ZF=RF/(1+s*RF-CF)

通過右腿驅(qū)動(dòng)電路設(shè)計(jì)可以進(jìn)一步抑制腦電信號(hào)的共模噪聲。利用ADSD1299內(nèi)置的偏置驅(qū)動(dòng)放大器加上很少的元器件就可以設(shè)計(jì)出偏置驅(qū)動(dòng)電路,詳細(xì)電路請(qǐng)參考數(shù)據(jù)手冊(cè)。這個(gè)電路是由ADSD1299內(nèi)置偏置驅(qū)動(dòng)放大器以及外圍的REXT、CEXT組成。REXT為反饋電阻。反饋電容CEXT的作用是進(jìn)行相位補(bǔ)償,用來防止自激。選擇BIAS AMP運(yùn)放的正參考端BIASREF為(AVDD+AVSS)/2即系統(tǒng)地AGND,能夠形成一個(gè)閉環(huán)回路結(jié)構(gòu)。該閉環(huán)回路電路實(shí)際上就是一個(gè)對(duì)消驅(qū)動(dòng)電路,共模信號(hào)通過該反饋電路可以在人體上產(chǎn)生一個(gè)極性相反的共模信號(hào),將共模干擾噪聲限制在一個(gè)很窄的范圍內(nèi),該范圍大小取決于該環(huán)路的增益A:

系統(tǒng)軟件設(shè)計(jì)

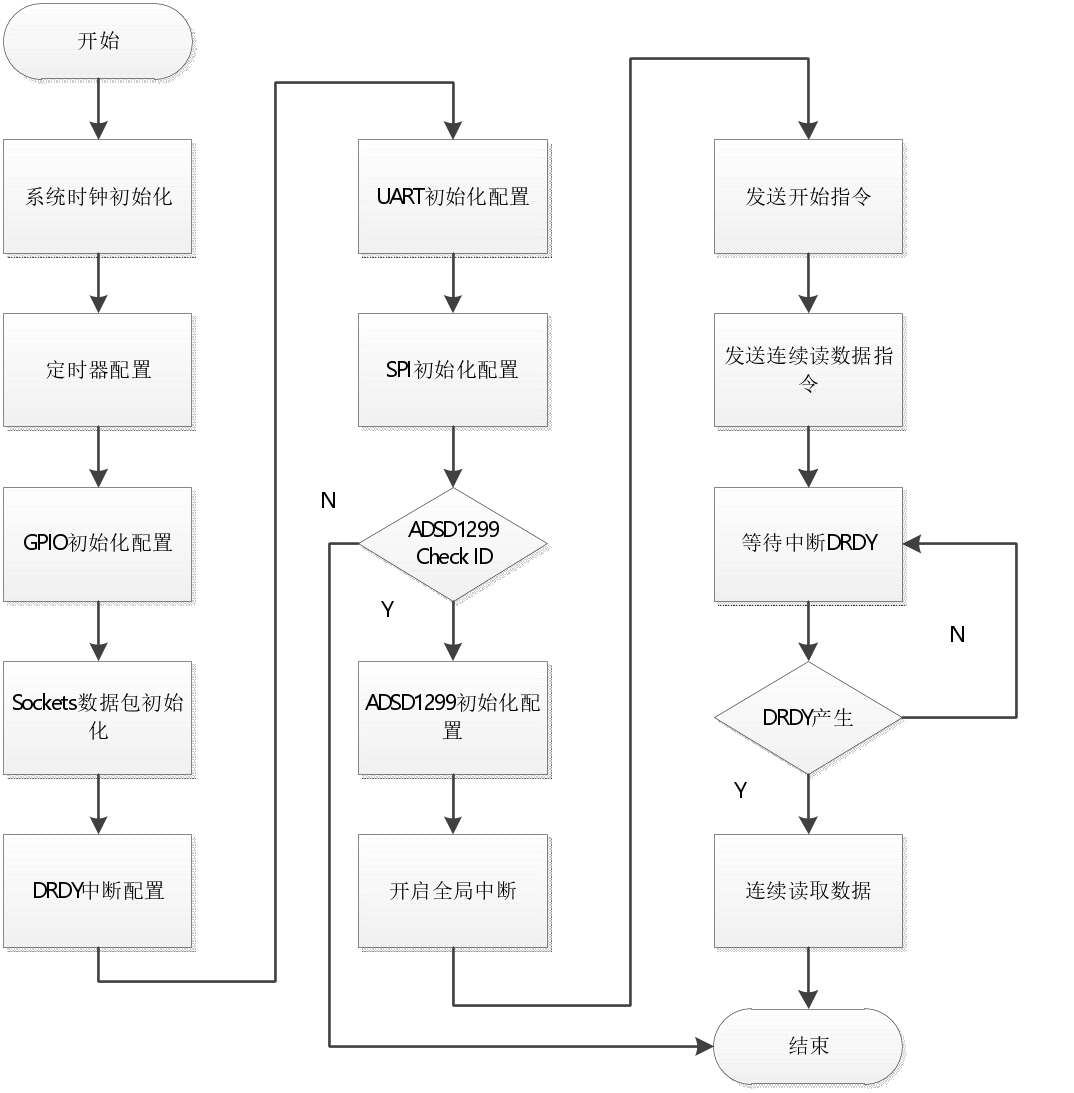

圖4系統(tǒng)軟件流程圖

該系統(tǒng)主要通過低功耗MCU控制器編程實(shí)現(xiàn),圖4為系統(tǒng)的軟件程序流程圖,設(shè)備上電以后,主程序?qū)ο到y(tǒng)時(shí)鐘、外設(shè)模塊所需的GPIO端口、UART、SPI接口進(jìn)行初始化設(shè)置,設(shè)置腦電數(shù)據(jù)包格式,并對(duì)數(shù)據(jù)包進(jìn)行初始化。初始化完成后開始校驗(yàn)ADSD1299是否工作正常,ID正確后對(duì)ADSD1299進(jìn)行初始化配置,包括ADSD1299的內(nèi)部功能寄存器和時(shí)鐘源配置等;以上配置完成后則開啟全局中斷,發(fā)送開始連續(xù)讀數(shù)據(jù)操作指令;中斷產(chǎn)生則通過SPI連續(xù)讀取8通道腦電數(shù)據(jù);通過串口將數(shù)據(jù)發(fā)送給藍(lán)牙模塊,藍(lán)牙模塊進(jìn)行無線數(shù)據(jù)傳輸發(fā)送給 PC 端上位機(jī)進(jìn)行接收。

ADSD1299芯片設(shè)計(jì)優(yōu)勢(shì)

EEG信號(hào)采集是一種強(qiáng)噪聲背景下的微弱信號(hào)的采集,這對(duì)于EEG信號(hào)的采集前端電路設(shè)計(jì)提出了很高的技術(shù)要求。利用芯動(dòng)神州的ADSD1299芯片內(nèi)部集成的各種特有EEG功能可以大幅簡(jiǎn)化采集前端設(shè)計(jì)的電路規(guī)模。為設(shè)計(jì)出新一代的便攜式、低功耗、高性能的實(shí)時(shí)穿戴式腦電采集系統(tǒng)提供了有力的技術(shù)支持。

-

芯片

+關(guān)注

關(guān)注

459文章

52471瀏覽量

440479 -

電路板

+關(guān)注

關(guān)注

140文章

5130瀏覽量

102563 -

穿戴式

+關(guān)注

關(guān)注

0文章

25瀏覽量

10214

原文標(biāo)題:芯動(dòng)神州發(fā)布ADSD1299助攻穿戴式腦電采集系統(tǒng)

文章出處:【微信號(hào):ickey360,微信公眾號(hào):芯三板】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

使用ADS1299進(jìn)行腦電信號(hào)采集時(shí)采集不到腦電信號(hào),怎么解決?

使用16片ADS1299做128路腦電采集, 腦電帽上有128個(gè)電極+1參考電極, 電極如何接入到ADS1299呢?

ADS1299EEGFE-PDK采集腦電方法是怎樣的呢?

兩片ADS1299在同一個(gè)頭上采集腦電時(shí),能各自獨(dú)立工作嗎?

用ADS1299做32導(dǎo)的腦電,需要4片ADS1299,請(qǐng)問4片ADS1299應(yīng)該是級(jí)聯(lián)還是菊花鏈?

請(qǐng)問ADS1299適用于腦電系統(tǒng)嗎?

ADS1299在實(shí)際測(cè)量中采集的腦電中還是有很強(qiáng)的共模50Hz干擾,為什么?

基于ads1299做一個(gè)腦電采集設(shè)備的話,電極帽上需要有參考電極嗎?

【藍(lán)牙4.1申請(qǐng)】基于藍(lán)牙的頭戴式腦電采集模塊

【HC-02V1.1藍(lán)牙串口模塊申請(qǐng)】便攜式腦電設(shè)備

TI ADS1299的國(guó)產(chǎn)替代方案-ADSD1299芯片

芯動(dòng)神州ADSD1299芯片完全pin to pin兼容TI的ADS1299,功能兼容ADS1298

芯動(dòng)神州八通道同步采樣ADC在電池化成測(cè)試設(shè)備中的應(yīng)用

芯動(dòng)神州發(fā)布ADSD1299助攻穿戴式腦電采集系統(tǒng)

芯動(dòng)神州發(fā)布ADSD1299助攻穿戴式腦電采集系統(tǒng)

評(píng)論