在數(shù)字 IC 設(shè)計(jì)中,有時(shí)候需要從一組輸入數(shù)據(jù)中挑出某一個(gè)數(shù)據(jù)出來(lái),比如,輸入有 ** “** A、B、C、D” 四個(gè)數(shù)據(jù),我們需要在特定的條件和特定的時(shí)刻輸出特定的數(shù)據(jù),如何輸出特定的數(shù)據(jù)就是 ** “選擇開(kāi)關(guān)” ** ;又或者,可以理解成多個(gè)通道輸入映射到 單個(gè)通道輸出 ;于是, 數(shù)據(jù)選擇器(Data Selector) 或 多路開(kāi)關(guān)(Multiplexer) 的數(shù)字邏輯電路就應(yīng)運(yùn)而生。

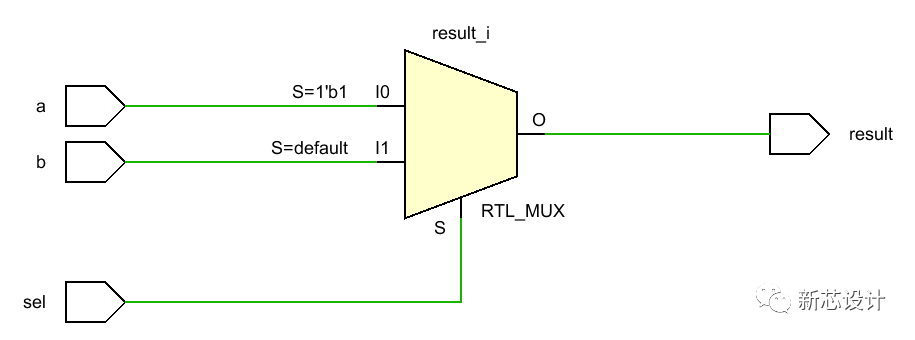

基于 2 選 1 的數(shù)據(jù)選擇器的 Verilog 代碼和 RTL 電路

module Multiplexer( // MUX

input wire a , // 輸入數(shù)據(jù)信號(hào)

input wire b , // 輸入數(shù)據(jù)信號(hào)

input wire sel , // 輸入控制信號(hào)

output result // 輸出數(shù)據(jù)信號(hào)_已選擇

);

assign result = sel ? a : b;

endmodule

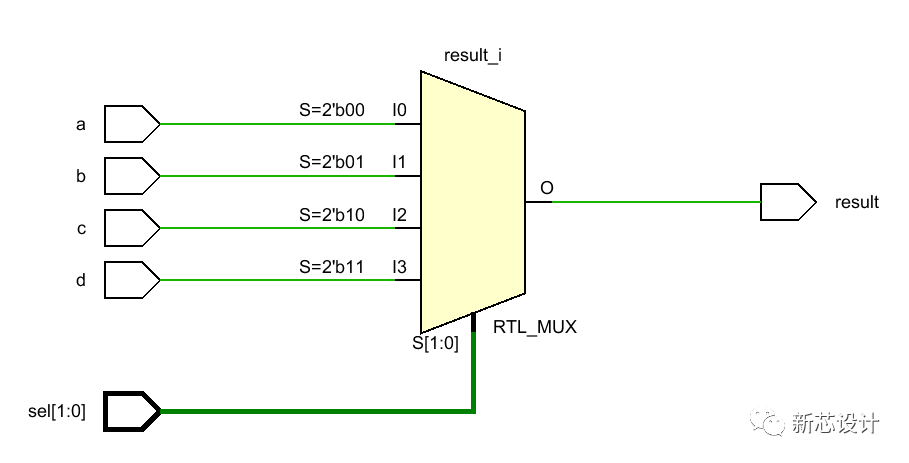

基于 4 選 1 的數(shù)據(jù)選擇器的 Verilog 代碼和 RTL 電路

module Multiplexer( // MUX

input wire a , // 輸入數(shù)據(jù)信號(hào)

input wire b , // 輸入數(shù)據(jù)信號(hào)

input wire c , // 輸入數(shù)據(jù)信號(hào)

input wire d , // 輸入數(shù)據(jù)信號(hào)

input wire [1:0] sel , // 輸入控制信號(hào)

output reg result // 輸出數(shù)據(jù)信號(hào)_已選擇

);

always @(sel, a, b, c, d) begin

case (sel)

2'b00: result <= a;

2'b01: result <= b;

2'b10: result <= c;

2'b11: result <= d;

endcase

end

endmodule

代碼詳解

基于 2 選 1 的數(shù)據(jù)選擇器的設(shè)計(jì)代碼,非常簡(jiǎn)單明了,主要是輸入數(shù)據(jù) a 和 b,然后通過(guò) sel 信號(hào)來(lái)決定輸出是 a 還是 b。倘若 sel 拉高 (1) ,那么就輸出 ** “a”** ,反之,倘若 sel 拉低 (0) ,那么就輸出 ** “b”** 。

基于 4 選 1 的數(shù)據(jù)選擇器的設(shè)計(jì)是基于 查找表 LUT(Look Up Table) (查找表在 FPGA 中非常重要,軟件思維可以理解為 “索引”,它是 FPGA 芯片架構(gòu)的重要組成部分,合理利用查找表,能夠使你的 FPGA 硬件工程達(dá)到一定程度的優(yōu)化設(shè)計(jì))的方式實(shí)現(xiàn)的一個(gè)電路。

數(shù)據(jù)選擇器在實(shí)際生活中應(yīng)用廣泛。比如,在實(shí)際中對(duì)選手進(jìn)行挑選,比如在歌手舞臺(tái)對(duì) “啊三” 編號(hào)為 “a”,對(duì) “啊四” 編號(hào)為 “b”。然后 “sel” 這個(gè)選擇信號(hào)就交給 “裁判”,倘若 “啊三” 唱歌功底勝出,那么就輸出 “a”,反之那么就輸出 “b”,非常的形象!!!

所以還是那句話,數(shù)字電路模塊沒(méi)有哪一個(gè)模塊是平白無(wú)故添加出來(lái)的,每一個(gè)數(shù)字電路的小模塊在實(shí)際生活中都有著非常重要的應(yīng)用。所有的復(fù)雜的模塊,都是由這些小模塊構(gòu)成的。 計(jì)算機(jī)再?gòu)?qiáng)大、AI 再智能,都離不開(kāi)最基本的電路設(shè)計(jì)單元。

因此,學(xué)好數(shù)字電路的基礎(chǔ)知識(shí)之后,才能翱翔于數(shù)字電路的世界中,如果基礎(chǔ)知識(shí)都學(xué)不好的話,那么更復(fù)雜的就更不用說(shuō)了。

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1346瀏覽量

105219 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81557 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12766 -

數(shù)據(jù)選擇器

+關(guān)注

關(guān)注

2文章

116瀏覽量

16582 -

FPGA芯片

+關(guān)注

關(guān)注

3文章

248瀏覽量

40207

發(fā)布評(píng)論請(qǐng)先 登錄

組合邏輯電路PPT電子教案

數(shù)據(jù)選擇器

【下載】《數(shù)字邏輯電路的ASIC設(shè)計(jì)》

請(qǐng)問(wèn)怎樣去設(shè)計(jì)多輸入時(shí)序邏輯電路?

熟悉中規(guī)模集成電路數(shù)據(jù)選擇器的工作原理和邏輯功能

組合邏輯電路設(shè)計(jì)實(shí)驗(yàn)

數(shù)字邏輯電路設(shè)計(jì)課程

數(shù)據(jù)選擇器

數(shù)據(jù)選擇器的定義及功能

數(shù)據(jù)選擇器的數(shù)字邏輯電路設(shè)計(jì)

數(shù)據(jù)選擇器的數(shù)字邏輯電路設(shè)計(jì)

評(píng)論