DAC模塊作為CKS32F4xx系列的一個(gè)常用外設(shè),可以將數(shù)字信號(hào)轉(zhuǎn)換成模擬信號(hào),最高分辨率可達(dá)12位,且兩個(gè)獨(dú)立DAC輸出通道轉(zhuǎn)換互不影響,各個(gè)通道均能使用DMA功能,可由軟硬件觸發(fā)。因此,為了實(shí)現(xiàn)DAC輸出正弦波,擬采用一定的時(shí)間向DAC的數(shù)據(jù)寄存器寫入數(shù)據(jù),隨后進(jìn)行數(shù)模轉(zhuǎn)換輸出不同的電壓,最后在時(shí)間軸上顯示出波形。同時(shí)為了不占用CPU資源,配置DMA建立傳輸通道,以便數(shù)據(jù)快速的從內(nèi)存搬移到外設(shè)。且在DAC初始化時(shí),可以設(shè)置成定時(shí)器觸發(fā),待定時(shí)器溢出就會(huì)觸發(fā)DAC工作,所以只要修改定時(shí)器的定時(shí)時(shí)間,就可改變正弦波周期。

DAC簡述

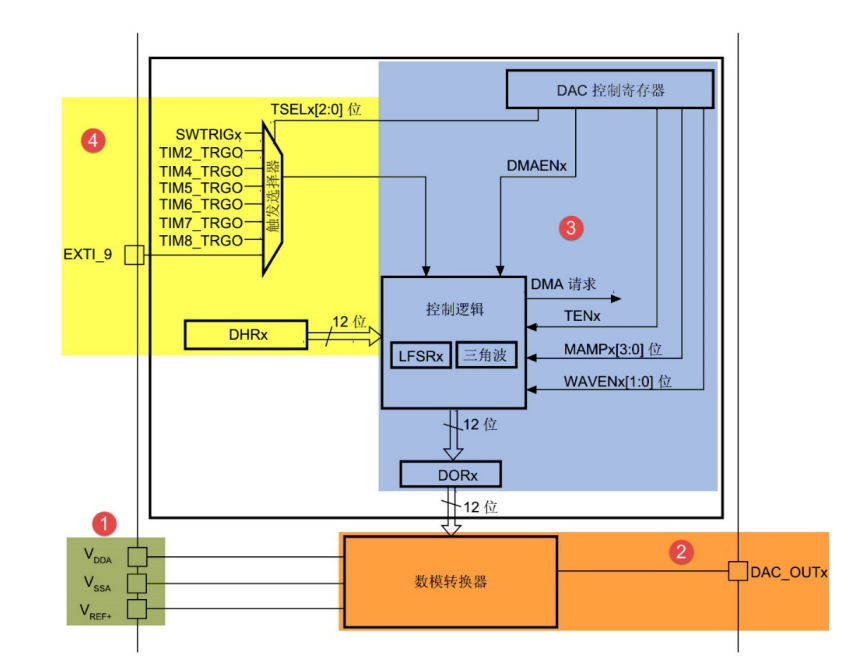

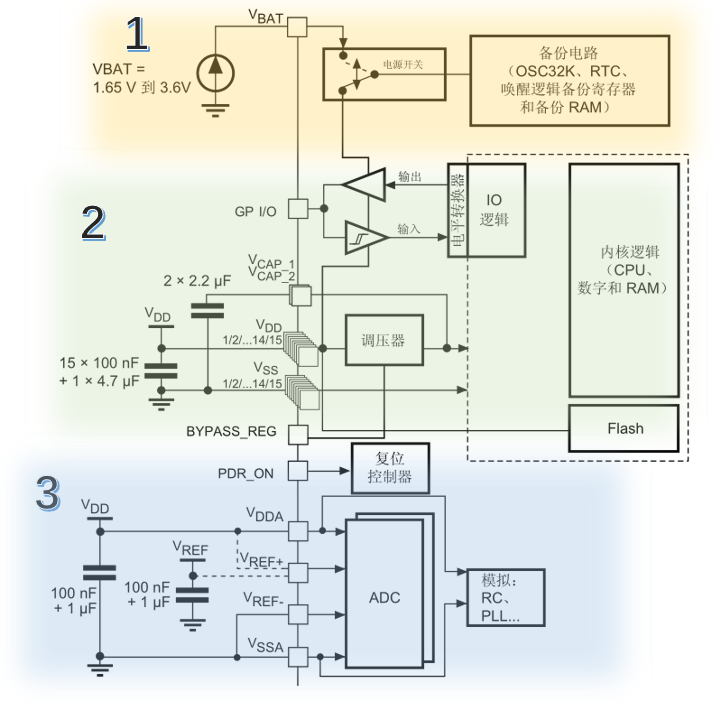

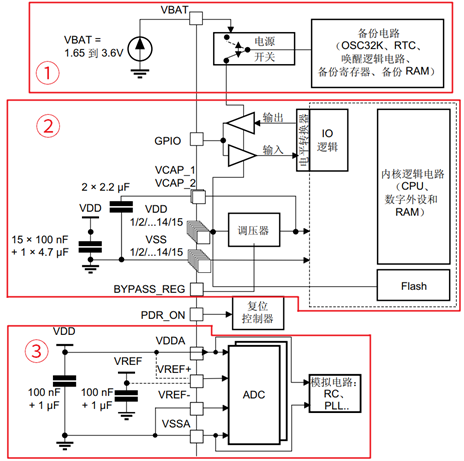

①:DAC將VREF+引腳作為參考電壓,在實(shí)際使用時(shí)將VSSA接地,同時(shí)把VREF+和VDDA接3.3V,DAC即可獲得0~3.3V的輸出電壓。

②:數(shù)模轉(zhuǎn)換器以VREF+作為參考電源,將DAC的數(shù)據(jù)寄存器“DORx”的數(shù)字編碼轉(zhuǎn)換成模擬信號(hào)并由右側(cè)的“DAC_OUTx”通道輸出。在CKS32有2個(gè)這樣的DAC部件,其中PA4對(duì)應(yīng)通道1,PA5對(duì)應(yīng)通道2。

③:控制邏輯可以控制數(shù)據(jù)寄存器“DORx”加入一些偽噪聲信號(hào)或配置產(chǎn)生三角波信號(hào)。

④:使用DAC時(shí),數(shù)據(jù)會(huì)被先寫入到DHRx寄存器,隨后DAC會(huì)根據(jù)觸發(fā)配置進(jìn)行處理,最后將數(shù)據(jù)傳輸至DORx。DAC的觸發(fā)源有三種,分別為:外部中斷源觸發(fā)、定時(shí)器觸發(fā)和軟件控制觸發(fā)。

對(duì)于單DAC通道x的三種數(shù)據(jù)格式

8位數(shù)據(jù)右對(duì)齊:

用戶須將數(shù)據(jù)寫入寄存器DAC_DHR8Rx[7:0]位(實(shí)際是存入寄存器DHRx[11:4]位)。

12位數(shù)據(jù)左對(duì)齊:

用戶須將數(shù)據(jù)寫入寄存器DAC_DHR12Lx[15:4]位(實(shí)際是存入寄存器DHRx[11:0]位)。

12位數(shù)據(jù)右對(duì)齊:

用戶須將數(shù)據(jù)寫入寄存器DAC_DHR12Rx[11:0]位(實(shí)際是存入寄存器DHRx[11:0]位)。

數(shù)字輸入經(jīng)過DAC被線性地轉(zhuǎn)換為模擬電壓輸出,任一DAC通道引腳上的輸出電壓滿足下面的關(guān)系:

本案例中選擇DAC的通道1,并采用12位的右對(duì)齊方式,通過查閱《CKS32F4xx參考手冊》DAC和DMA章節(jié)可知,DAC1對(duì)應(yīng)DMA1控制器通道7數(shù)據(jù)流5。

總的來說,DAC的輸出是由DORx寄存器直接控制的,而用戶寫的數(shù)據(jù)是要寫入DHRx寄存器,然后通過DHRx間接操作DORx,最終實(shí)現(xiàn)DAC的輸出。

DAC輸出正弦波配置

本文采用DAC1+TIM2+DMA1的方式,通過TIM2觸發(fā)DAC1轉(zhuǎn)換,轉(zhuǎn)換完成后通過DMA1輸出,主要步驟如下:

①由Matlab計(jì)算一個(gè)周期的正弦波數(shù)組;

②根據(jù)一個(gè)正弦波周期內(nèi)點(diǎn)數(shù)和所需正弦波頻率確定定時(shí)器觸發(fā)間隔;

③初始化DAC1輸出管腳和工作模式;

④配置觸發(fā)DAC1用的定時(shí)器2;

⑤配置DMA1自主搬運(yùn)正弦波數(shù)組。

待上述配置完成后,將PA4引腳接到示波器上,即可顯示正弦波。以下是DAC的詳細(xì)配置。

(1)正弦波數(shù)組生成

以下代碼用于生成正弦波波形表:

for(i=0;i<100;i++)

{

????Sine12bit[i]=2048*sin(1.0*i/(100-?1)*2*PI)+2048;

}

從上述函數(shù)可以看出,正弦波的幅度被控制在0~4096之間,一個(gè)周期被平均分成100份,即100個(gè)點(diǎn)代表一個(gè)周期的波形,數(shù)組Sine12bit里面是100個(gè)采樣點(diǎn)。

constuint16_tSine12bit[100]={

0x0800,0x0881,0x0901,0x0980,0x09FD,0x0A79,0x0AF2,0x0B68,0x0BDA,0x0C49,0x0CB3,0x0D19,0x0D79,0x0DD4,0x0E29,0x0E78,0x0EC0,0x0F02,0x0F3C,0x0F6F,0x0F9B,0x0FBF,0x0FDB,0x0FEF,0x0FFB,0x0FFF,0x0FFB,0x0FEF,0x0FDB,0x0FBF,0x0F9B,0x0F6F,0x0F3C,0x0F02,0x0EC0,0x0E78,0x0E29,0x0DD4,0x0D79,0x0D19,0x0CB3,0x0C49,0x0BDA,0x0B68,0x0AF2,0x0A79,0x09FD,0x0980,0x0901,0x0881,0x0800,0x077F,0x06FF,0x0680,0x0603,0x0587,0x050E,0x0498,0x0426,0x03B7,0x034D,0x02E7,0x0287,0x022C,0x01D7,0x0188,0x0140,0x00FE,0x00C4,0x0091,0x0065,0x0041,0x0025,0x0011,0x0005,0x0001,0x0005,0x0011,0x0025,0x0041,0x0065,0x0091,0x00C4,0x00FE,0x0140,0x0188,0x01D7,0x022C,0x0287,0x02E7,0x034D,0x03B7,0x0426,0x0498,0x050E,0x0587,0x0603,0x0680,0x06FF,0x077F};

(2)GPIO和DAC模式配置

該部分為輸出引腳配置和DAC通道1配置,代碼如下:

voidDAC1_GPIO_Init(void)

{

GPIO_InitTypeDefGPIO_InitStructure;

DAC_InitTypeDefDAC_InitStructure;

/*EnableGPIOAclock*/

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA,ENABLE);/*EnableDACclock*/RCC_APB1PeriphClockCmd(RCC_APB1Periph_DAC,ENABLE);/*ConfiguretheDACPintoAnalogmode:DAC_OUT1--PA4*/GPIO_InitStructure.GPIO_Pin=GPIO_Pin_4;GPIO_InitStructure.GPIO_Mode=GPIO_Mode_AIN;

GPIO_InitStructure.GPIO_PuPd=GPIO_PuPd_NOPULL;

GPIO_InitStructure.GPIO_Speed=GPIO_Speed_100MHz;

GPIO_InitStructure.GPIO_OType=GPIO_OType_PP;

GPIO_Init(GPIOA, GPIO_InitStructure);

/*ConfigureDACChannel_1*/

DAC_InitStructure.DAC_Trigger=DAC_Trigger_T2_TRGO;

DAC_InitStructure.DAC_WaveGeneration=DAC_WaveGeneration_None;DAC_InitStructure.DAC_OutputBuffer=DAC_OutputBuffer_Disable;DAC_InitStructure.DAC_LFSRUnmask_TriangleAmplitude=DAC_LFSRUnmask_Bit0;DAC_Init(DAC_Channel_1, DAC_InitStructure);

DAC_Cmd(DAC_Channel_1,ENABLE);//EnableDACChannel_1.

DAC_DMACmd(DAC_Channel_1,ENABLE);//EnableDACchannel_1DMArequest.

}

在DAC1_GPIO_Init函數(shù)中,實(shí)現(xiàn)了相應(yīng)GPIO引腳(PA4)的初始化和DAC工作模式配置。其中為了避免寄生的干擾和額外的功耗,應(yīng)將PA4引腳設(shè)置成模擬輸入模式(AIN),如此方可正常工作。

而對(duì)DAC工作模式進(jìn)行配置時(shí),可查看CKS官方提供的DAC_InitTypeDef結(jié)構(gòu)體,該結(jié)構(gòu)體中主要包含了DAC_CR寄存器的各寄存器配置。如下是DAC_InitTypeDef結(jié)構(gòu)體成員簡述:

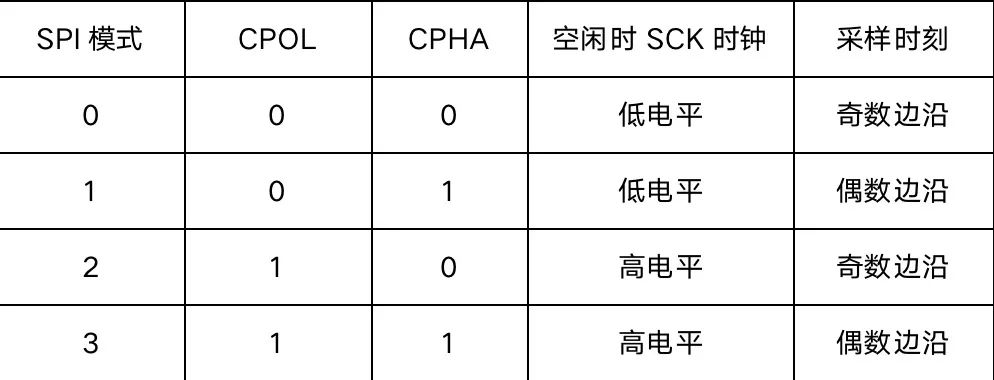

(a)DAC_Trigger

該成員用于DAC的觸發(fā)模式配置,由上文DAC通道框圖可知,共有三種觸發(fā)模式,分別是定時(shí)器觸發(fā)(DAC_Trigger_T2/4/5/6/7/8_TRGO)、軟件觸發(fā)(DAC_Trigger_Software)和EXTI_9觸發(fā)方式(DAC_Trigger_Ext_IT9)。

(b)DAC_WaveGeneration

該成員可配置輸出偽噪聲和三角波輸出(DAC_WaveGeneration_Noise/Triangle),若使用自定義輸出,應(yīng)配置為DAC_WaveGeneration_None。

(c)DAC_OutputBuffer

該成員用于控制是否使能DAC的輸出緩沖(DAC_OutputBu?er_Enable/Disable)。若需要直接驅(qū)動(dòng)外部負(fù)載,可以使能該成員以減小輸出阻抗。

(d)DAC_LFSRUnmask_TriangleAmplitude

該成員通過控制DAC_CR的MAMP2位設(shè)置LFSR寄存器位的數(shù)據(jù),即當(dāng)使用偽噪聲或三角波輸出時(shí)要疊加到DHRx的值。若使用偽噪聲輸出時(shí)LFSR=0xAAA,這時(shí)該結(jié)構(gòu)體成員可賦值為DAC_LFSRUnmask_Bit0~DAC_LFSRUnmask_Bit11_0;若使用三角波輸出時(shí),這時(shí)該結(jié)構(gòu)體成員可賦值為DAC_TriangleAmplitude_1~DAC_TriangleAmplitude_4096,可用于設(shè)置三角波的最大幅值。

本例中,將DAC通道1配置成定時(shí)器TIM2觸發(fā),不使用波形發(fā)生器和不使用輸出緩存,不使用輸出緩存是因?yàn)镃KS32的DAC無需外部運(yùn)放就可以直接驅(qū)動(dòng)負(fù)載,三角波振幅一項(xiàng)雖然本案例沒有用到,可以配置成任意,但此項(xiàng)不可缺,最后調(diào)用DAC_Cmd、DAC_DMACmd函數(shù)使能DAC通道1和DMA的請求。

(3)定時(shí)器配置

該部分是配置觸發(fā)DAC的定時(shí)器TIM2,通過設(shè)定觸發(fā)的間隔,從而間接控制正弦波周期,TIM2的工作決定DMA與DAC的工作頻率,代碼如下:

voidTIM2_Init(void) { TIM_TimeBaseInitTypeDefTIM_TimeBaseStructure; /*EnableTimer2clock.*/ RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM2,ENABLE);/*ConfigureTimer2--ClockFrequencyis84MHz*/ TIM_TimeBaseStructure.TIM_Period=83;TIM_TimeBaseStructure.TIM_Prescaler=0x0; TIM_TimeBaseStructure.TIM_ClockDivision=0x0; TIM_TimeBaseStructure.TIM_CounterMode=TIM_CounterMode_Up; TIM_TimeBaseInit(TIM2, TIM_TimeBaseStructure);/*ConfigurethetriggersourceforTimer2.*/TIM_SelectOutputTrigger(TIM2,TIM_TRGOSource_Update); TIM_Cmd(TIM2,ENABLE);//EnableTimer2. }

前文的DAC已選用TIM2當(dāng)觸發(fā)源,此處TIM2的定時(shí)周期被配置為83,向上計(jì)數(shù),不分頻。CKS32F4xx系列的主頻是168MHz,TIM2的時(shí)鐘是84MHz,所以TIM2的更新頻率是84M/(TIM_Period+1)/(TIM_Prescaler+1),即TIM2每隔1us觸發(fā)一次DAC事件,不需要設(shè)置中斷,當(dāng)定時(shí)器向上計(jì)數(shù)至指定值時(shí),產(chǎn)生Update事件,同時(shí)觸發(fā)DAC把DHRx寄存器的數(shù)據(jù)轉(zhuǎn)移到DORx,開始進(jìn)行轉(zhuǎn)換。由于正弦波數(shù)組是100個(gè)采樣點(diǎn),可得正弦波的輸出頻率為:

(4)DMA配置

該部分主要完成數(shù)據(jù)的傳輸,代碼如下:

voidDMA_InitForDAC(void) { DMA_InitTypeDefDMA_InitStructure; /*EnableDMA1clock.*/RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_DMA1,ENABLE);/*ConfigureDMA1Stream5Channel_7ForDAC1*/ DMA_InitStructure.DMA_Channel=DMA_Channel_7;DMA_InitStructure.DMA_PeripheralBaseAdDMA_InitStructure.DMA_Memory0BaseAddr=(uint32_t)Sine12bit;DMA_InitStructure.DMA_DIR=DMA_DIR_MemoryToPeripheral; DMA_InitStructure.DMA_BufferSize=100; DMA_InitStructure.DMA_PeripheralInc=DMA_PeripheralInc_Disable; DMA_InitStructure.DMA_MemoryInc=DMA_MemoryInc_Enable;DMA_InitStructure.DMA_PeripheralDataSize=DMA_PeripheralDataSize_HalfWord;DMA_InitStructure.DMA_MemoryDataSize=DMA_MemoryDataSize_HalfWord; DMA_InitStructure.DMA_Mode=DMA_Mode_Circular; DMA_InitStructure.DMA_Priority=DMA_Priority_High;DMA_InitStructure.DMA_FIFOMode=DMA_FIFOMode_Disable;DMA_InitStructure.DMA_FIFOThreshold=DMA_FIFOThreshold_HalfFull;DMA_InitStructure.DMA_MemoryBurst=DMA_MemoryBurst_Single;DMA_InitStructure.DMA_PeripheralBurst=DMA_PeripheralBurst_Single;DMA_Init(DMA1_Stream5, DMA_InitStructure);DMA_Cmd(DMA1_Stream5,ENABLE);//EnableDMA1Stream5. }

需要注意的是,DAC->DHR12R1對(duì)應(yīng)數(shù)據(jù)寄存器的地址,正弦波數(shù)組Sine12bit對(duì)應(yīng)數(shù)據(jù)輸入地址,DMA緩存的個(gè)數(shù)是單個(gè)正弦波周期對(duì)應(yīng)的點(diǎn)數(shù),DMA需工作在循環(huán)模式,由于正弦波數(shù)組Sine12bit定義為16位,那么涉及數(shù)據(jù)傳輸?shù)淖兞慷家渲贸砂胱?6位。經(jīng)過上述的配置后,定時(shí)器TIM2每隔1us就會(huì)觸發(fā)DMA搬運(yùn)正弦波數(shù)組的一個(gè)數(shù)據(jù)到DAC通道1寄存器進(jìn)行轉(zhuǎn)換,每搬運(yùn)100個(gè)數(shù)據(jù)即一個(gè)完整周期后,DMA開始循環(huán),最終循環(huán)輸出正弦波。

(5)主函數(shù)配置

本例程主函數(shù)主要對(duì)前文所述函數(shù)依次調(diào)用,程序編譯下載至開發(fā)板,使用示波器測量PA4引腳即可查看輸出10kHz的正弦波形,代碼如下:

intmain(void)

{

DAC1_GPIO_Init();

TIM2_Init();

DMA_InitForDAC();

while(1);

}

來源:中科芯MCU

-

寄存器

+關(guān)注

關(guān)注

31文章

5423瀏覽量

123431 -

dac

+關(guān)注

關(guān)注

43文章

2379瀏覽量

193068 -

定時(shí)器

+關(guān)注

關(guān)注

23文章

3288瀏覽量

117270 -

dma

+關(guān)注

關(guān)注

3文章

572瀏覽量

102364

發(fā)布評(píng)論請先 登錄

MCU微課堂|CKS32F4xx系列產(chǎn)品時(shí)鐘配置

CKS32F4xx系列DSP功能介紹

CKS32F4xx系列產(chǎn)品串口DMA傳輸

CKS32F4xx系列RNG功能設(shè)置

CKS32F4xx系列FSMC功能簡介

CKS32F4xx系列DAC功能

CKS32F4xx系列DAC功能

評(píng)論