隨著SoC芯片逐漸復(fù)雜化,其DFT(Design for Test)架構(gòu)也由單層向多層網(wǎng)絡(luò)發(fā)展。IEEE 1687是DFT多層網(wǎng)絡(luò)結(jié)構(gòu)的通用標(biāo)準(zhǔn),其核心內(nèi)容包括Heirachical Architecture,模塊連接語言ICL(Instrument Connectivity Language)和過程描述語言PDL(Procedural Description Language)。

其中,ICL是一種硬件架構(gòu)描述語言,用于描述設(shè)計中IEEE 1687的網(wǎng)絡(luò)結(jié)構(gòu)(又稱IJTAG網(wǎng)絡(luò)結(jié)構(gòu)),即不同類型嵌入式模塊之間的層級連接,使得硬件的可擴(kuò)展性和訪問的靈活性得到極大地加強(qiáng)。

一、ICL的組成

ICL是描述模塊間連接的語言,它不包括設(shè)備內(nèi)部具體操作的細(xì)節(jié)。因此可以概括地說,ICL是由Instruments 及其Connection描述組成的。

1、Instrument

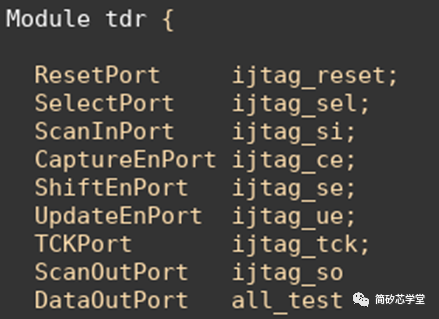

ICL中的Instrument包含TAP、SIB、TDR及DFT IPs(EDT,OCC,MBIST…),它們是構(gòu)成1687網(wǎng)絡(luò)的關(guān)鍵節(jié)點(diǎn),每一個Instrument都在Module中定義,如圖定義的TDR。

2、Connection

ICL中的Connection是對Instrument的Keywords 、Attribute、Scan_Cell、Interface以及PortsToPorts連接等的描述。

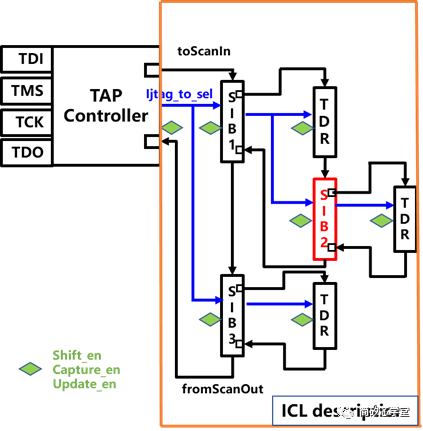

如圖是ICL描述的網(wǎng)絡(luò)結(jié)構(gòu)的部分示意圖,SIB和TDR為Instruments,不同顏色的連線即ICL描述的Connection。以SIB_2為例,其ICL描述語言如下:

Instance sib_* Of sib_2 {

InputPort ijtag_reset = ijtag_reset;

InputPort ijtag_sel = ijtag_sel;

InputPort ijtag_si = sib1.ijtag_so;

InputPort ijtag_ce = ijtag_ce;

InputPort ijtag_se = ijtag_se;

InputPort ijtag_ue = ijtag_ue;

InputPort ijtag_tck = ijtag_tck;

InputPort ijtag_from_so = tdr.ijtag_so;

Attribute tessent_design_instance = "sib_*";

}

二、ICL的Bottom Up

IEEE 1687的多層網(wǎng)絡(luò)結(jié)構(gòu)決定了ICL是以Bottom Up的方式逐步實現(xiàn)對Core層、Subsys層及Chip層的描述。

1、Core層的描述

Core層的ICL會對Modified Core內(nèi)部的Module逐一按照如下步驟描述:

首先,ICL會整理出該Module的IJTAG網(wǎng)絡(luò)端口及Interface,可能包括ClkPort、ToClkPort、SelectPort、CaptureEnPort、ShiftEnPort、ScanInPort、ScanOutPort、UpdataEnPort、DataOutPort等,并且會source這些端口的來源,描述它們的屬性,比如Clock_Domain、Connection_Rule等;

接下來,ICL逐一將module內(nèi)部實例化的DFT IP的Client/Host端口與其他實例連接,具體到端口對端口,形成DFT網(wǎng)絡(luò);

最后,Core內(nèi)部Module的ICL集成得到整個Core的ICL。

2、Subsys層的描述及與Core層ICL的銜接

Subsys層ICL的描述步驟與Core一致。如果Subsys內(nèi)含有上述已經(jīng)存在ICL的Core,那么首先,該Subsys會將內(nèi)部Core當(dāng)成一個Box,抓取Core_Top層的IJTAG端口加入到Subsys層的描述,從而將Subsys層的IJTAG網(wǎng)絡(luò)與Core層的IJTAG網(wǎng)絡(luò)進(jìn)行組合。

而后,Core內(nèi)部的關(guān)于Module和Instance的ICL描述都會復(fù)述到Subsys的ICL中,使得Subsys與Core在ICL文件中形成一個完整的DFT網(wǎng)絡(luò)。

Chip層的描述及其與Subsys層的銜接

Chip層的ICL描述步驟與Subsys一致,對于內(nèi)部已存在ICL的Module的處理方式也與Subsys一致。

將分層的ICL集成,會得到整個Chip的完整ICL網(wǎng)絡(luò)。

三、總結(jié)

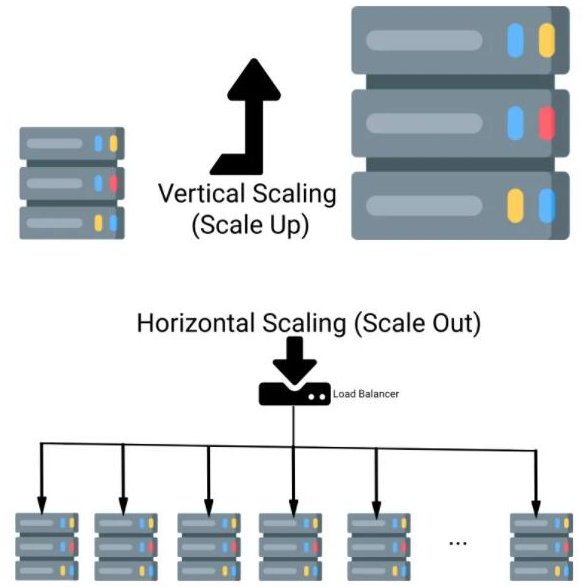

基于ICL的可擴(kuò)展性和靈活性,它可以抽取設(shè)計中的IEEE 1687結(jié)構(gòu),方便用戶從高層次的角度去配置相應(yīng)的寄存器。ICL語言還可以幫助用戶了解和配置復(fù)雜的IEEE 1687網(wǎng)絡(luò),解決了在配置寄存器時網(wǎng)絡(luò)復(fù)雜、難以確定輸入數(shù)據(jù)長度和值的問題。

-

處理器

+關(guān)注

關(guān)注

68文章

19775瀏覽量

233225 -

寄存器

+關(guān)注

關(guān)注

31文章

5410瀏覽量

123085 -

SoC芯片

+關(guān)注

關(guān)注

1文章

630瀏覽量

35604 -

TDR

+關(guān)注

關(guān)注

1文章

70瀏覽量

20204 -

DFT算法

+關(guān)注

關(guān)注

0文章

27瀏覽量

7673

發(fā)布評論請先 登錄

什么是云計算的可擴(kuò)展性?

請問工業(yè)以太網(wǎng)如何使網(wǎng)絡(luò)更具可擴(kuò)展性?

視頻監(jiān)控系統(tǒng)新結(jié)構(gòu)必須具備可擴(kuò)展性

基于軟件定義網(wǎng)絡(luò)控制可擴(kuò)展性研究

Beyond 100G標(biāo)準(zhǔn)的靈活性和可擴(kuò)展性

如何解決區(qū)塊鏈的可擴(kuò)展性問題

區(qū)塊鏈可擴(kuò)展性的要點(diǎn)分別是什么

影響軟件高可擴(kuò)展性的六大因素

AIoT開放平臺可實現(xiàn)靈活且可擴(kuò)展的開發(fā)

接入 5G:NVIDIA CloudXR 4.0 現(xiàn)已發(fā)布,優(yōu)化 XR 部署的靈活性和可擴(kuò)展性

什么是可擴(kuò)展性,為什么它很重要

西部數(shù)據(jù)推出全新產(chǎn)品助力數(shù)據(jù)中心提升靈活性和可擴(kuò)展性

基于ICL的可擴(kuò)展性和靈活性可以抽取設(shè)計中的IEEE 1687結(jié)構(gòu)

基于ICL的可擴(kuò)展性和靈活性可以抽取設(shè)計中的IEEE 1687結(jié)構(gòu)

評論