電源抑制比是什么意思?電源抑制比怎么提高?

一、電源抑制比的概念

電源抑制比(PSRR)又稱電源噪聲抑制比,是指在電路中,當電源發生噪聲時,電路輸出端對電源噪聲的抑制程度,一般使用分貝(dB)單位表示。電源噪聲多數來自于電源線路中的電感、電容、功率管等組件,在電路工作過程中,電源信號可能發生抖動,從而產生對電路各個部分的影響,導致電路輸出端的干擾和誤差。

二、電源抑制比的意義

在很多應用中,大部分精度和帶寬實際上都由電源噪聲抑制比所決定,因為電源噪聲抑制比高,就能保證電路輸出端的干擾和誤差較小,成為保證電路穩定可靠工作的重要因素。例如在高性能模擬轉換器中,需要對輸入信號進行高精度轉換,而轉換器的輸出端即為整個系統的響應,如果電源噪聲抑制比太低,將會引入電源噪聲干擾,從而導致系統精度下降。因此,提高電源噪聲抑制比是提高系統性能和輸出信號質量的重要手段。

三、電源抑制比的影響因素

1、電源噪聲的頻率范圍:在電源噪聲的頻率范圍內,電源抑制比會逐漸降低或變化。在工作頻率范圍內,電路對電源噪聲的抑制能力會不斷增加,但超出該范圍,抑制能力會降低或失效。

2、電源線路的阻抗匹配:當電源線路的阻抗與負載端的阻抗不匹配時,會導致電源噪聲抑制比下降。電源線路應該采用合適的電源濾波器,使得電源輸出端的阻抗和負載端的阻抗匹配,以提高電源噪聲抑制比。

3、電源線路的穩定性:電源線路的穩定性也會影響電源噪聲抑制比。如果電源線路內部存在電流過大、功率管損壞等情況,將導致電源抑制比下降或失效。

四、電源抑制比的提高方法

1、使用低噪聲線性穩壓電源

線性穩壓電源比開關穩壓電源更具有穩定性,能夠提供更加穩定、低噪聲的電源,從而提高電路的穩定性和電源抑制比。

2、使用合適的電源濾波器

電源濾波器主要是利用電感和電容的濾波特性,將電源信號中的高頻噪聲濾除。在設計電源濾波器時,需要根據工作頻率和所需抑制比進行參數選擇,消除電源噪聲的影響,提高電路的穩定性和輸出信號質量。

3、合理布線

在抑制電源噪聲方面,合理的布線設計也非常重要。關鍵信號線路需要設備地面共模抑制(CMRR)和差分模式噪聲抑制(DMRR)電路的支持。同時,還要注意降低電源線路的電阻和電抗,以減少電源噪聲的穿透和影響。

總之,提高電源抑制比可以有效消除電源噪聲對電路的干擾和影響,提高系統的性能和精度,因此需要在設計和選型方面,重視電源噪聲抑制比的影響,采取相應的措施提高電源噪聲抑制比。

-

DMR

+關注

關注

1文章

33瀏覽量

13805 -

電源抑制比

+關注

關注

0文章

78瀏覽量

13891 -

PSRR

+關注

關注

0文章

216瀏覽量

39945 -

線性穩壓電源

+關注

關注

3文章

57瀏覽量

12583 -

電源濾波器

+關注

關注

6文章

457瀏覽量

25414

發布評論請先 登錄

什么是共模抑制比?

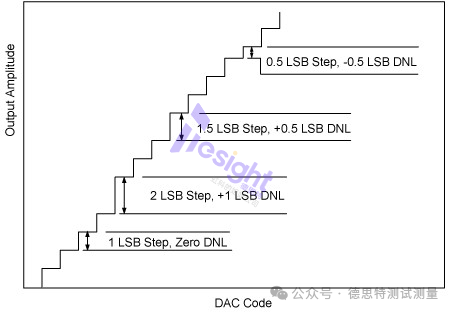

從偏移誤差到電源抑制比,DAC核心術語全解析

海洋儀器電源抑制比測試方案26800元起

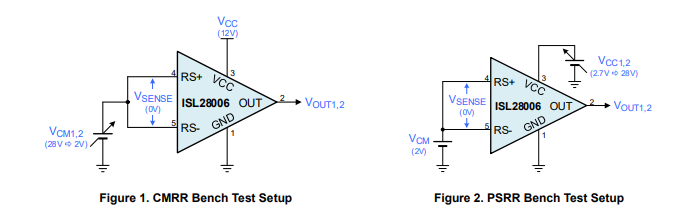

ISL28006:測量共模和電源抑制比

怎么測ADS1299芯片的共模抑制比?

詳解LDO電路的電源抑制比

如何準確計算電源引起的運放輸出失調電壓?1200字搞定運放電路選型之電源抑制比PSRR

電源抑制比是什么意思?電源抑制比怎么提高?

電源抑制比是什么意思?電源抑制比怎么提高?

評論