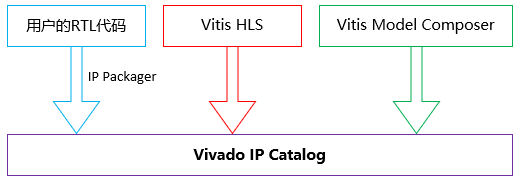

Vivado以IP為核心的設計理念的一個重要支撐就是IP Integrator(簡稱IPI,IP集成器)。用戶可以很便捷地把VivadoIP Catalog中的IP拖到IPI中形成Block Design(.bd文件)。

同時,對于用戶自己的RTL代碼,可以借助IP Packager先封裝成IP,再導入到IP Catalog中,然后在IPI中使用。

此外,Vitis HLS、Vitis Model Composer都可以將用戶設計以IP形式輸出供用戶導入到IP Catalog中調用。

盡管如此,不得不說借助IP Packager封裝IP的過程還是有些繁瑣的。當然,我們也要看到封裝IP帶來的好處就是便于不同設計團隊開發使用。IPI的功能仍在不斷增強。

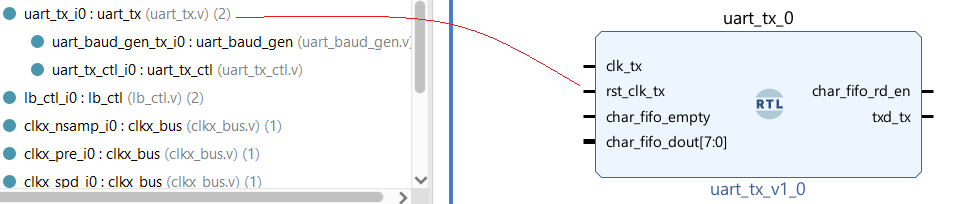

一個顯著的功能是用戶可以直接將RTL代碼拖到IPI中構成BD,如下圖所示。要求RTL設計的頂層如這里的uart_tx必須是Verilog或VHDL描述。SystemVerilog/VHDL-2008不支持此功能。

此功能被稱為模塊引用(Module Reference)。

關于模塊引用,我們可能會碰到以下問題。

問題1:待引用的頂層采用的是SystemVerilog或VHDL-2008描述的。

因為模塊引用不支持SystemVerilog也不支持VHDL-2008,在這種情況下,可以用Verilog或VHDL先對該模塊封裝以下,這樣就可以將封裝后的.v或.vhd模塊添加到IPI中。

問題2:若待引用的頂層其子模塊包含IP Catalog中的IP(以.xci形式存在),那么是否支持此功能?

模塊引用功能允許待引用的頂層其子模塊包含.xci IP,但并不是所有的IP都支持。可通過如下命令獲取不支持此功能的IP。可以看到NoC、CIPS和PS是不支持的。換言之,目前的Vivado版本(2023.1)只能在IPI中直接使用這些IP。

審核編輯:劉清

-

VHDL語言

+關注

關注

1文章

113瀏覽量

18692 -

RTL

+關注

關注

1文章

389瀏覽量

61122 -

Vivado

+關注

關注

19文章

835瀏覽量

68778 -

HLS

+關注

關注

1文章

133瀏覽量

24869

原文標題:如何把子模塊包含網表的RTL代碼添加到BD中

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

xilinx EDF已經綜合過的網表文件怎樣添加到Vivado工程中?

可以將塊設計添加到庫中嗎?

有什么方法能將以太網功能添加到PSoC設計中去?

將新庫添加到Petalinux rootfs的最簡單方法是什么

如何在arduino IDE上將SPI模塊作為庫添加到nodemcu代碼中?

Yocto S32G添加新層,如何添加到圖像?

如何將Crosswalk添加到Cordova應用程序中

將RTL模塊添加到Block Design的步驟

把子模塊包含網表的RTL代碼添加到BD中的方法分享

把子模塊包含網表的RTL代碼添加到BD中的方法分享

評論