01 導言和概述

導言和概述

本數據表描述了臺積電40nm ULP工藝中的TetraMem ADC IP。它的特點是:

占地面積小,適用于低速和多通道應用

異步架構,不需要外接高速時鐘

可根據要求提供帶隙

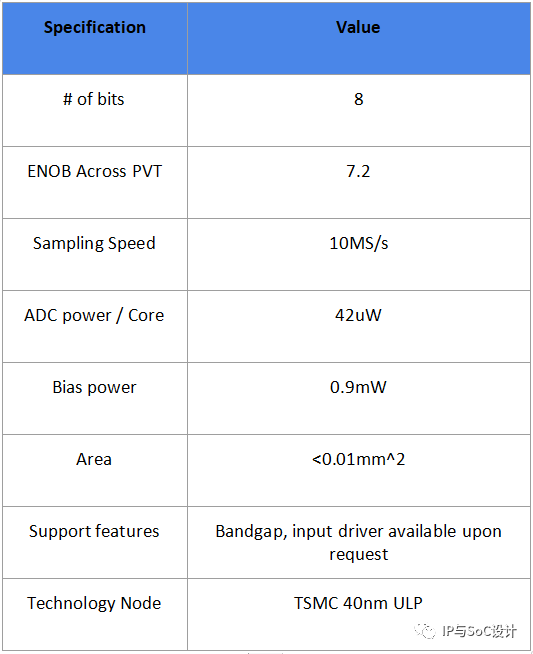

以下是主要規格表:

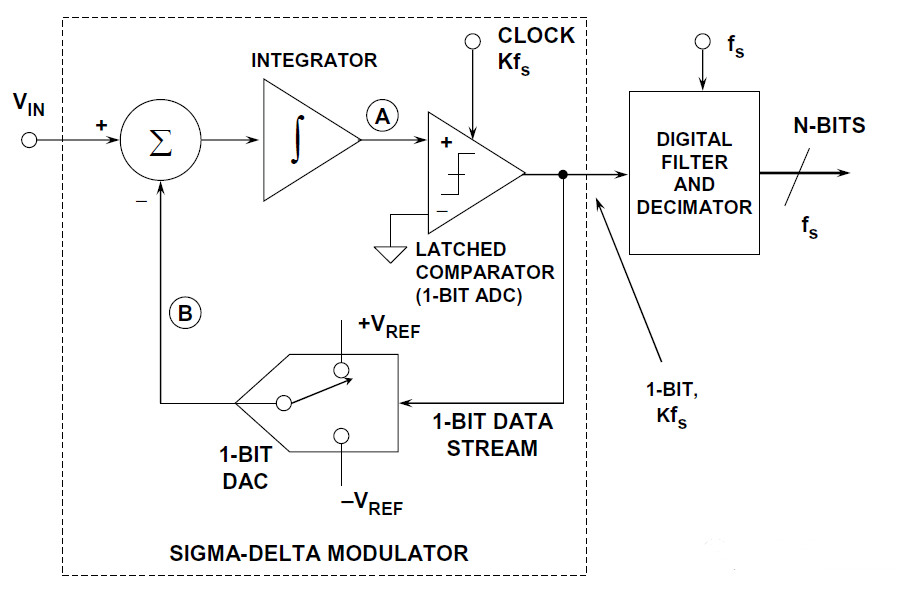

02ADC方框圖

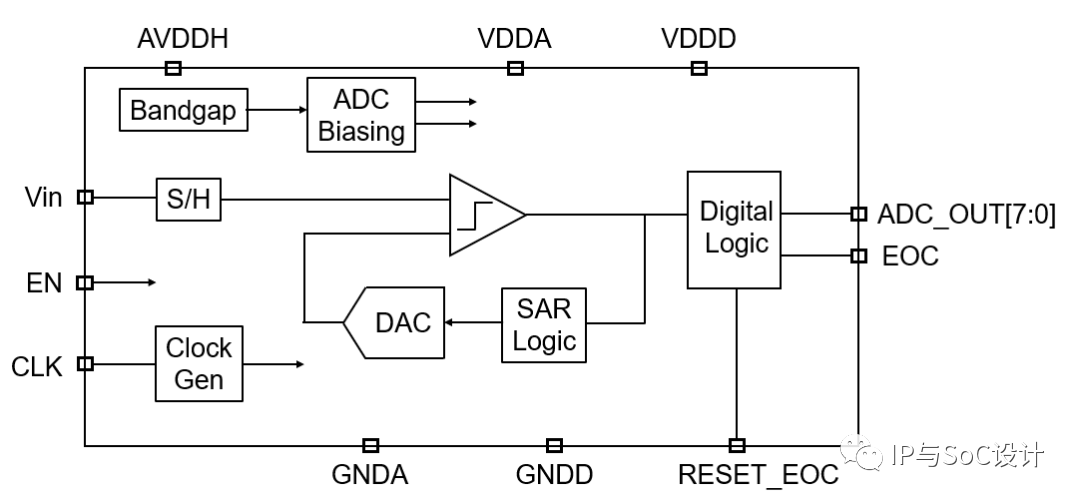

該IP的主要目標市場是物聯網、模擬人工智能或溫度傳感器的低面積、低功耗和低速應用。以下是IP的框圖:

我們設計了一個定制電容DAC(CDAC)陣列,其單位面積是業界最小的,可顯著減少IP面積和開關能耗。此外,我們仔細調整性能敏感的電路,如比較器,基準驅動器等,以達到最佳的PPA組合。最后,我們使用了一個專有的帶隙,以實現穩定的工作條件下,整個PVT的角落。

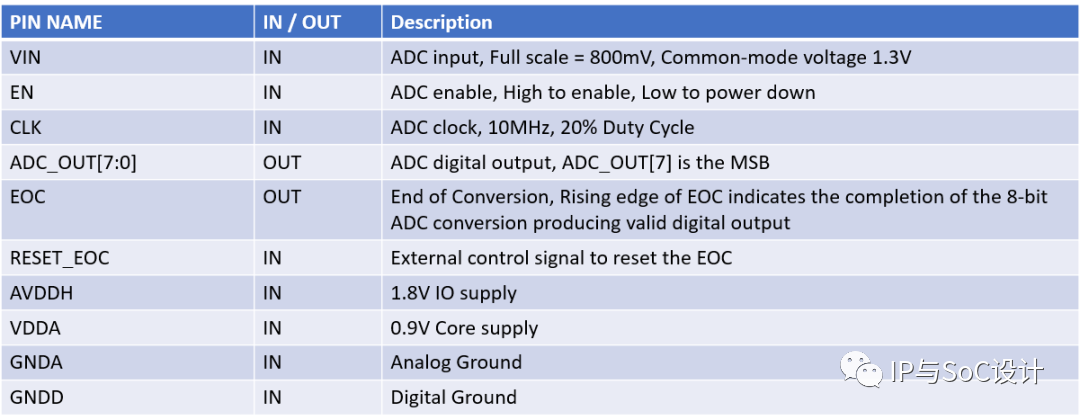

03ADC PIN描述

04ADC功率性能區

總功率:52uW

VDDA : 18uA x 0.9=16.2uW

AVDDH : 19uA x 1.8= 36uW

跨PVT角落的ENOB:7.3位

面積:7.76um x 120um = 931um2

Walden FoM = P /( fs x2 ^ ENOB )= 52u / (10M x 2 ^7.3)= 34FJ/凸步

05硅表征結果

2023年第三季度上市

06晶體管/金屬使用

核心晶體管:LVT、ULVT

高壓晶體管:1.8V晶體管

電容器:定制MOM和鑄造PDK MOM

金屬化:1P6M

電源:0.9V(鐵芯),1.8V(高壓)

審核編輯:湯梓紅

-

傳感器

+關注

關注

2562文章

52504瀏覽量

763266 -

臺積電

+關注

關注

44文章

5738瀏覽量

168856 -

adc

+關注

關注

99文章

6628瀏覽量

548161 -

時鐘

+關注

關注

11文章

1878瀏覽量

132807

原文標題:IP推薦:40nm ADC

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

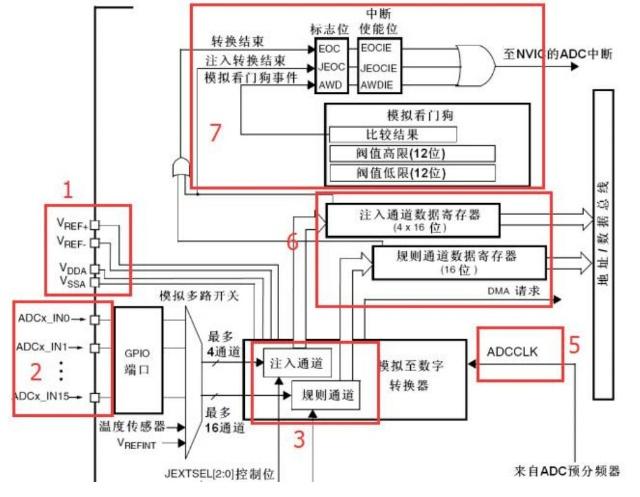

STM32F1 ADC主要特性和結構框圖解析

時鐘系統框圖解讀

STM32 ADC框圖講解

基于STM32單片機模塊練習——ADC功能框圖

STM32電源框圖解析(VDD、VSS、VDDA、VSSA、VREF+、VREF-、VBAT等的區別)

ADC框圖解析

ADC框圖解析

評論