幾年前FPGA時鐘只需要連接一個單端輸入的晶振,非常容易。現在不同了,差分時鐘輸入,差分信號又分為LVDS和LVPECL,時鐘芯片輸出后還要經過直流或交流耦合才能接入FPGA,有點暈了,今天仔細研究一下。

FPGA輸入時鐘要求

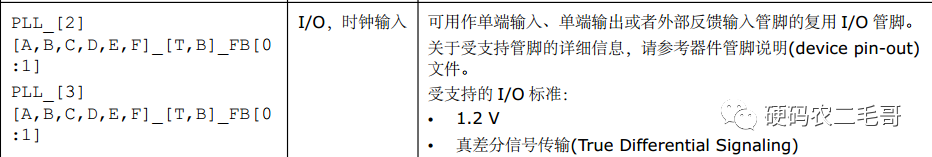

FPGA手冊中對時鐘輸入的描述:

差分I/O電平標準:

真差分信號電壓不能超過VICM(max) + VID(max)/2 。

直流耦合與交流耦合

時鐘的發送端和接收端都有各自的電平接口類型,它們有可能不相同也可能是相同的。 這個時候通常就會有兩種連接方式,即AC耦合以及DC耦合。 其實說簡單也很簡單, AC耦合就是中間用電容把發送接收端的共模電平隔開,而DC耦合就是不加電容 。交流耦合(AC Coupling)就是通過隔直電容耦合,去掉了直流分量。直流耦合(DC Coupling)就是直通,交流直流一起過,并不是去掉了交流分量。

LVDS與LVPECL

時鐘芯片輸出時鐘信號通常有LVDS和LVPECL。

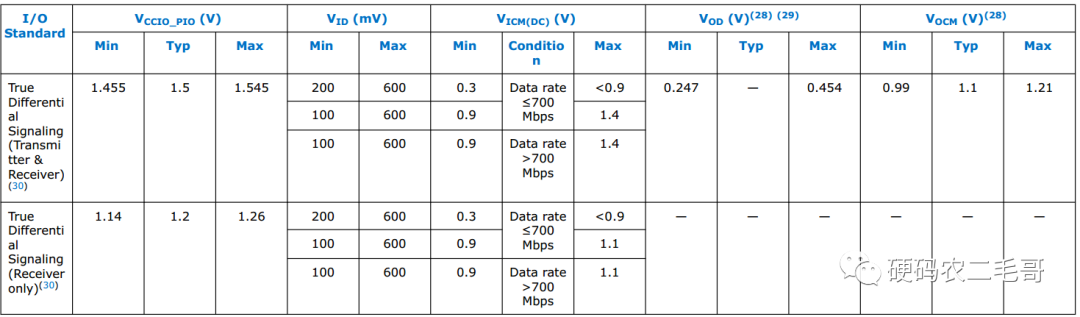

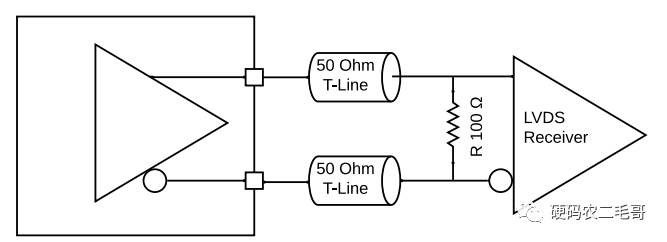

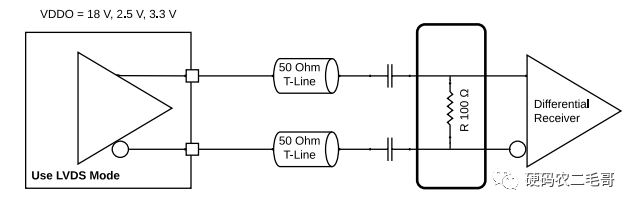

當時時鐘芯片輸出LVDS信號時

DC耦合

兩種AC耦合方式。

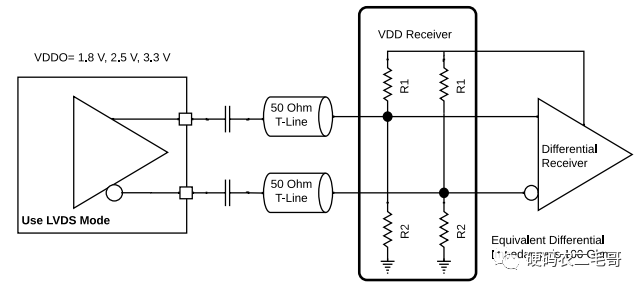

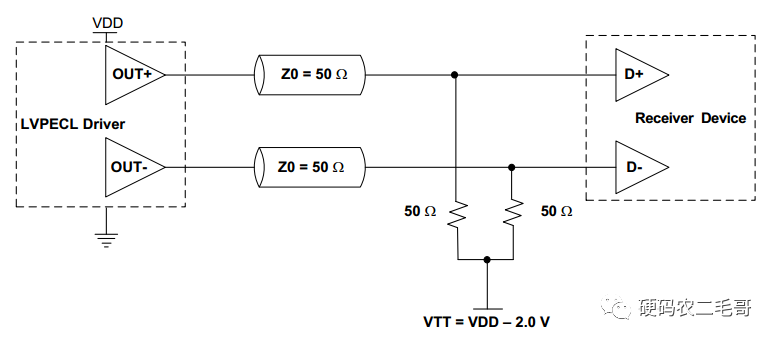

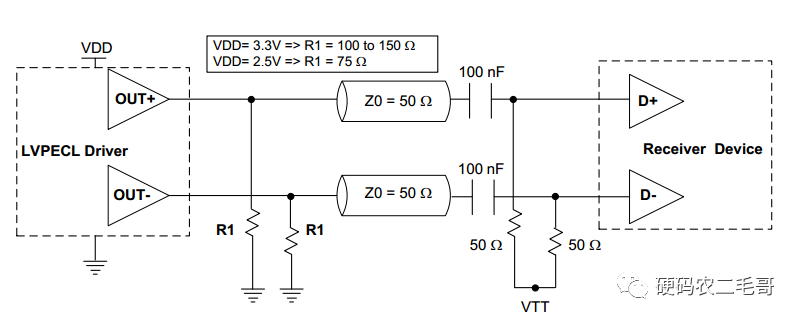

當時鐘信號輸出LVPECL信號時

-

FPGA

+關注

關注

1643文章

21952瀏覽量

613796 -

lvds

+關注

關注

2文章

1108瀏覽量

67036 -

時鐘芯片

+關注

關注

2文章

262瀏覽量

40560 -

差分信號

+關注

關注

4文章

387瀏覽量

28099 -

LVPECL

+關注

關注

2文章

40瀏覽量

18241

發布評論請先 登錄

可否直接使用LVPECL輸出的有源晶振交流耦合至AD的時鐘引腳?

LMK00725是否支持LVDS或者LVPECL的差分交流耦合輸入呢?

ADS5404可以使用LVDS或LVPECL的時鐘源頭嗎?

請問高速AD差分時鐘驅動能使用LVPECL輸出的有源晶振交流耦合至AD的時鐘引腳嗎?

請問FPGA管腳是否具有電平判決功能將輸入的模擬時鐘信號判決為數字時鐘信號?

ADCLK946是否可以直接給AD9739作為時鐘驅動LVDS

如何使用BLVDS或其他驅動Kintex LVPECL輸入的方法的信息?

CDCLVP111-SP具有可選輸入時鐘驅動器的低電壓1:10 LVPECL數據表

CDCLVP111低壓1:10 LVPECL,內置可選輸入時鐘驅動器數據表

淺談FPGA輸入時鐘要求 LVDS與LVPECL講解

淺談FPGA輸入時鐘要求 LVDS與LVPECL講解

評論