USB是通用串行總線的英文縮寫,是連接外部裝置的一個串口總線標準,也是一種輸入輸出接口的技術規范,被廣泛地應用于個人電腦和移動設備等信息通迅產品,并擴展到攝影器材,數字電視(機頂盒)、游戲機等其它相關領域。

USB2.0接口具有高達480Mbps的傳輸速率,USB3.0的最大傳輸帶寬高達5Gbps,USB3.0引入全雙工數據傳輸。USB的布局和布線有其對應的設計要求。

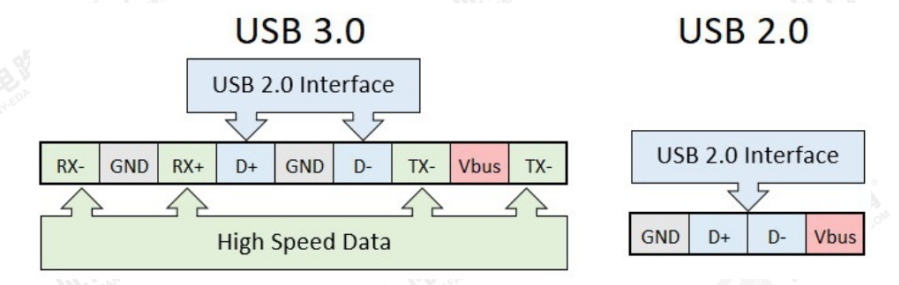

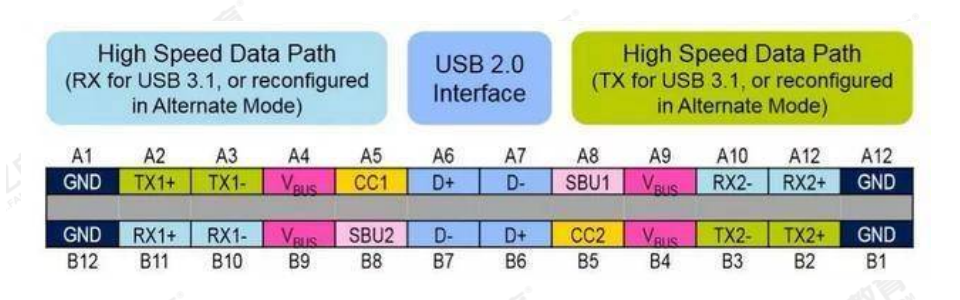

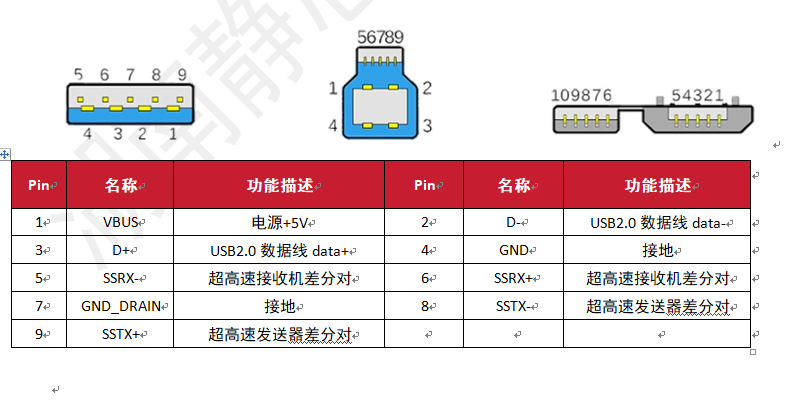

USB2.0及USB3.0接口管腳定義如圖1所示。

圖1 USB 2.0與USB 3.0管腳定義

一、USB接口的PCB布局要求

1、USB應該接口靠近板邊或結構定位放置,伸出板邊一定位置(直插除外),方便插拔;

2、ESD、共模電感器件靠近USB接口,放置的順序是ESD-共模電感-阻容;

3、注意ESD和USB的距離,留有一定的的間距,考慮后焊的情況。

4、在布局時,盡量使差分線路最短,以縮短差分線距離。

二、USB接口的PCB布線要求

1、USB要走差分,阻抗控制為90歐姆,并包地處理,總長度最好不要超過1800mil.

2、盡可能縮短走線長度,優先考慮對高速USB差分(RX、TX差分)的布線,USB差分走線在走線的時候,盡可以有的減少換層過孔,從而可以更好的做到阻抗的控制,避免信號的反射;

3、過孔會造成線路阻抗的不連續,在每次打孔換層的地方加一對回流地過孔,用于信號回流換層。

4、若USB兩邊定位柱接的是保護地,分割時保證與GND的距離是2MM,并在保護地區域多打孔,保證充分連接,如圖2所示。

圖2 外殼GND和信號GND的隔離

5、由于管腳分布、過孔、以及走線空間等因素存在使得差分線長易不匹配,布線長一旦不匹配,時序會發生偏差,還會引起共模干擾,降低信號質量。所以,相應的要對差分對不匹配的情況作出補償,使其線長匹配,長度差通常控制在5mil以內,補償按照差分等長規范來進行。

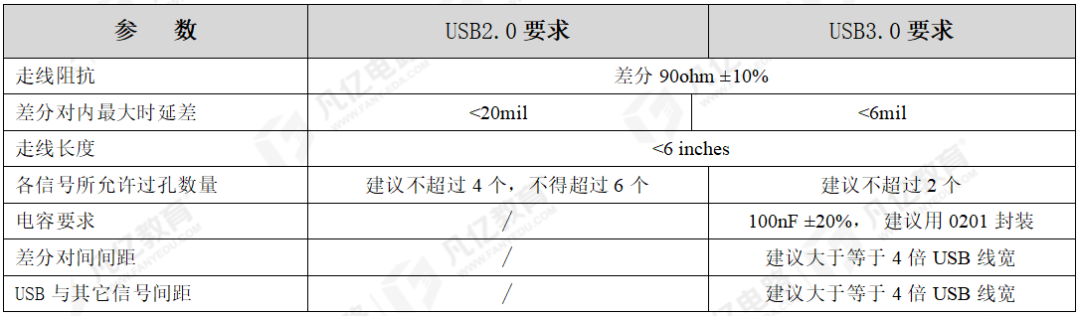

USB2.0與3.0的PCB布線要求對比如下表1所示:

表1 USB2.0與USB 3.0的PCB布線要求

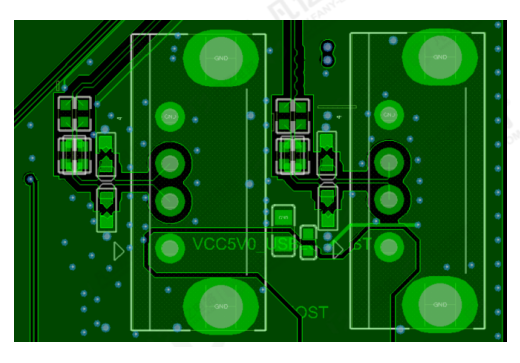

圖3 USB 2.0的布局與布線

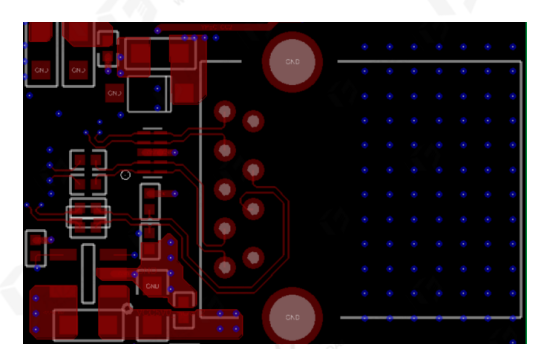

圖4 USB 3.0的布局與布線

三、Type C接口的PCB設計

USB Type C,又稱為USB-C。需要注意的是Type-C只是一種接口,和USB的版本沒有任何關系。該接口的亮點在于更加纖薄的設計、更快的傳輸速度(最高10Gbps以及更強悍的電力傳輸(最高100W)。Type-C雙面可插接口最大的特點的支持USB接口雙面插入,主要面向更輕薄、更纖細的設備。以下如圖7-23所示,為Type-C接口的管腳定義。

圖7-23 Type C接口的管腳定義

Type C接口的PCB設計要求:

1、ESD、共模電感器件靠近Type C接口,放置的順序是ESD→共模電感→阻容;同樣也要注意ESD 和Type C的距離,留有一定的間距,考慮后焊情況。

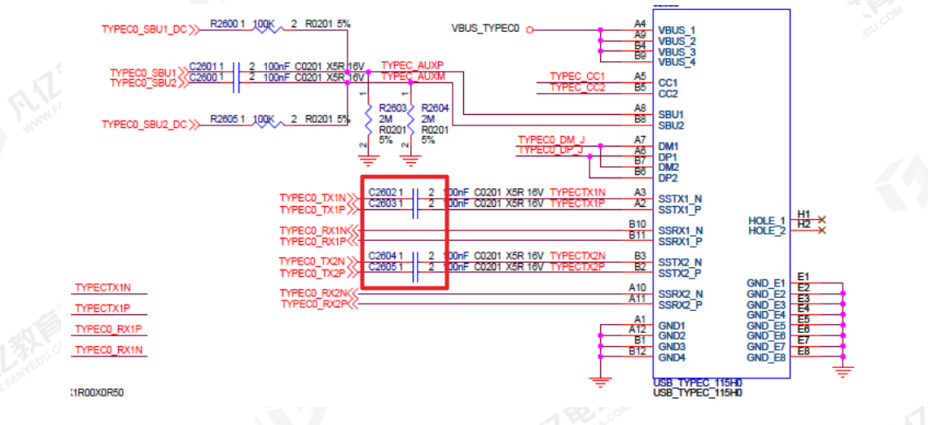

2、TX信號線的耦合電容應靠近接口放置,RX信號線的耦合電容由設備端提供,如圖7-24所示;

圖7-24 TX信號線的耦合電容

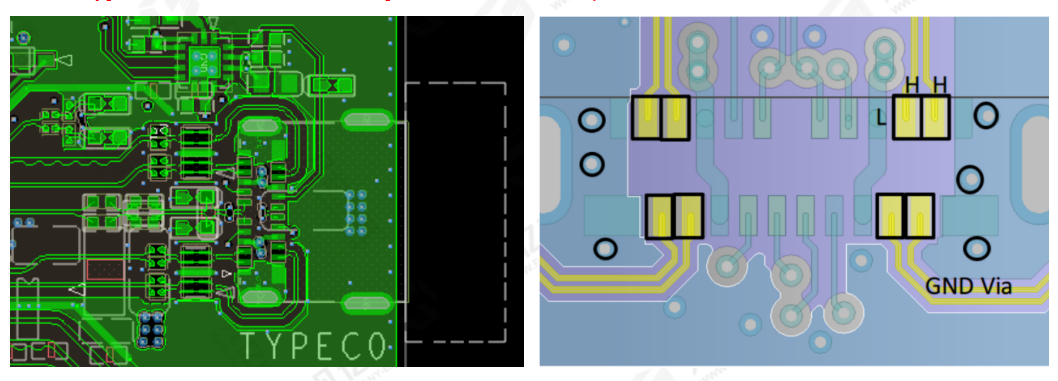

2、Type C差分走線阻抗控制90ohm±10%,為了保證阻抗的連續性,應該有良好的參考平面和不跨分割,信號打孔換層時數量不超過2個。

3、Type-C有RX/TX1-2四組差分信號,兩組D+/D-差分信號 ,一共六對差分線,差分信號線要求至少緊鄰一個地平面,兩側都緊鄰地平面最好,走線盡量短,走線最長不要超過6inchs。

4、保證Type C差分線長匹配,對內等長誤差<6mil,等長按照差分等長規范。

5、保證Type C差分對于對間或者差分對于其他信號的影響,對內間距建議是大于等于4倍Type C線寬。與其他信號之間的間距保持盡量大于等于4倍Type C線寬;

6、CC1/CC2是兩個關鍵引腳,作用很多:探測連接,區分正反面,區分DFP和UFP,也就是主從配置Vbus,走線時面要加粗處理。

注意:Type-C連接器工作速率≥8Gbps時,請按照第五章5.6節的連接器優化建議進行設計處理

圖7-25 Type-C連接器布線示意

-

pcb

+關注

關注

4349文章

23403瀏覽量

406415 -

USB3.0

+關注

關注

1文章

268瀏覽量

80575 -

連接器

+關注

關注

99文章

15201瀏覽量

139202 -

usb

+關注

關注

60文章

8134瀏覽量

270546 -

USB2.0

+關注

關注

2文章

188瀏覽量

46652 -

PCB設計

+關注

關注

396文章

4775瀏覽量

89073 -

PCB布線

+關注

關注

21文章

467瀏覽量

42492 -

PCB布局

+關注

關注

9文章

189瀏覽量

28166 -

type-c

+關注

關注

553文章

1886瀏覽量

270684

原文標題:USB2.0與USB3.0接口的PCB布局布線要求

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

用外在部件將其從USB3.0強制到USB2.0后如何高效重新打開設備?

調試CX3 USB3.0兼容USB2.0出圖的問題求解

在automaster和autoslave項目中如何配置參數來滿足usb3.0和usb2.0的數據傳輸?

是否可以與USB2.0集線器 (CYUSB2302) 共享USB2通道SS線路直接到USB3.0端口?

CYUSB3014無法識別為USB3.0設備怎么解決?

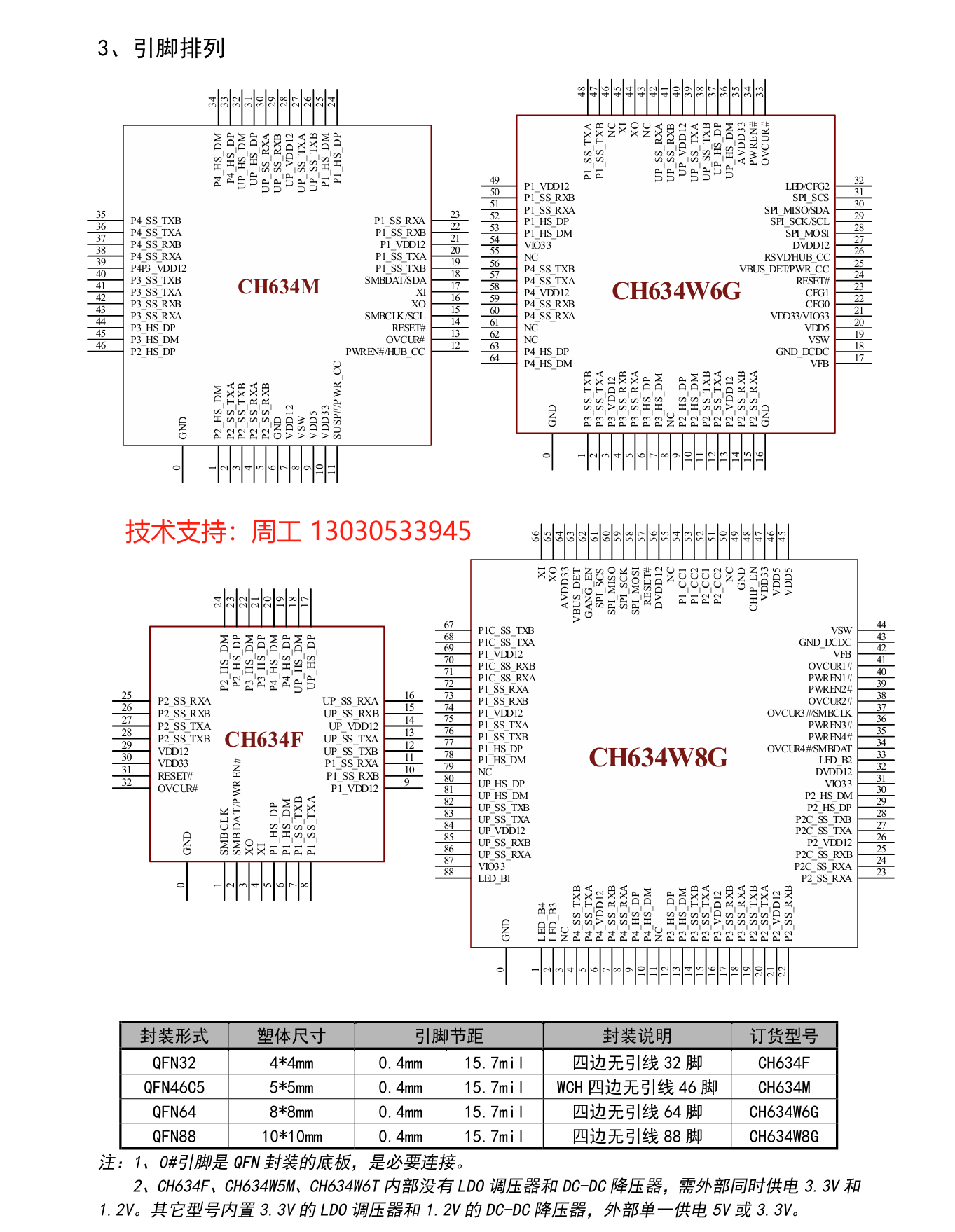

CH634USB3.0HUB控制芯片USB3.0國產控制芯片

TUSB8041是否支持將USB2.0通道的數據編碼到USB3.0通道去?

有沒有ASM3354 USB2.0口轉SATA的bridge?

USB3.0的識別問題

CYUSB3014是否會自動調整工作模式USB3.0還是USB2.0?

USB3.0/3.1靜電放電防護方案

Fcx3 usb2.0攝像頭分辨率問題求解

矽力杰USB2.0接口ESD保護方案

USB2.0與USB3.0接口的PCB布局布線要求

USB2.0與USB3.0接口的PCB布局布線要求

評論