串聯電阻R與半導體ESD 電路布線中,哪個應放置靠近被保護IC?

在信號線防浪涌保護中,信號線時常會串一顆小阻值的電阻作為保護器件來抑制浪涌電流,起到限流的作用。但對于更大的電流和電壓防護,還需搭配一顆TVS或ESD ,對后級芯片起到更高的防浪涌保護。

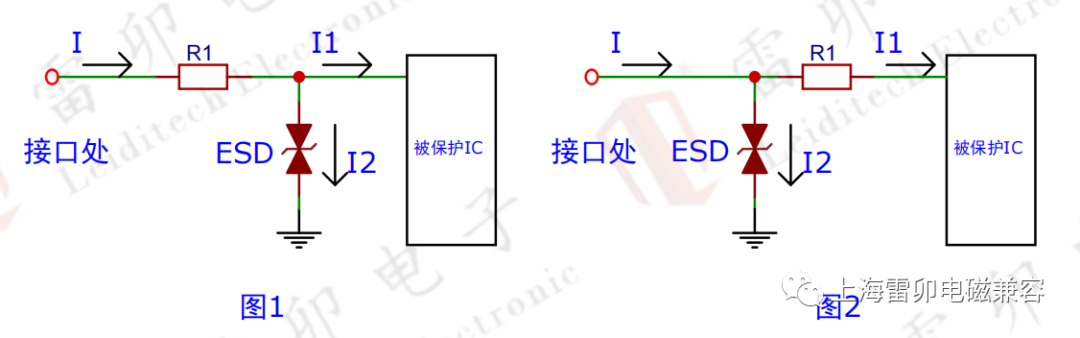

串聯電阻R和ESD怎么放呢?是串聯電阻靠近被保護芯片放,ESD靠近接口放;還是ESD靠近芯片放,串聯電阻靠近接口放。上海雷卯工程師發現其實放置不同,防浪涌等級是不同的。

2.理論分析

在如圖1所示的情況下, ESD動作時, I=I1+I2, I>I1, 在R1上會流過比ESD中更大的電流。雖然在這種情況下被保護電路在一定程度上得到保護,但電阻R1,卻經不起大電流的考驗而損壞,結果造成接口故障、系統故障。

在如圖2所示的情況下, ESD動作保護有效時, ESD的阻抗很低, 大部分電流從ESD中流過,即I2, 而在R1中流過的電流I1遠遠小于I2,那就更小于I。雖然在這種情況下ESD要經受比如圖1所示的情況更大的電流, 但是ESD與電阻相比更能經受得起大電流,因此芯片的防浪涌等級實際升高了。

實際試驗中圖1信號接口的抗浪涌電壓能力比圖2接口要差很多。上海雷卯電子工程師常發現圖1接口失效是由于串聯在接口電路上的電阻損壞造成的,而ESD沒有損壞;圖2接口失效是由于ESD被擊穿短路造成的,電阻沒有損壞。由此上海雷卯工程師得出結論:電阻靠近被芯片放置,而ESD靠近接口放置這種搭配時防護能力更強。

需要注意的是,在設計防浪涌保護電路時,應根據具體應用的需求來選擇合適的串聯電阻和TVS。阻值的選擇通常在幾十至幾百歐姆之間,應考慮平衡信號質量和保護效果。TVS的額定電壓應大于預期的過電壓水平。

3.上海雷卯接口電路防護電路推薦

1)RS485接口浪涌防護電路

? ?

? ?

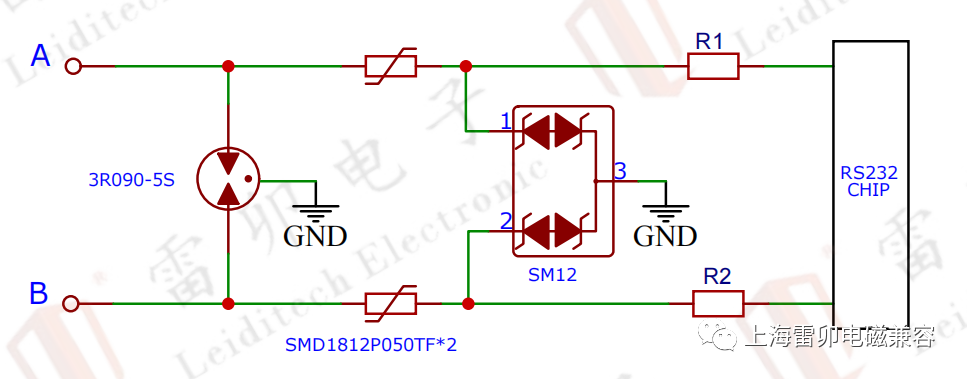

2)RS232接口浪涌防護電路 ??

??

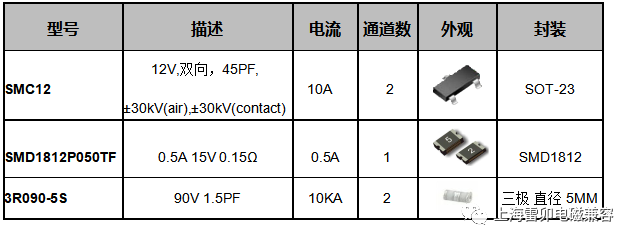

3)RS485接口浪涌防護元件列表

4)RS232接口浪涌防護元件列表

審核編輯:劉清

-

串聯電阻

+關注

關注

1文章

234瀏覽量

15223 -

ESD

+關注

關注

50文章

2289瀏覽量

175671 -

TVS管

+關注

關注

1文章

284瀏覽量

20893 -

浪涌電壓

+關注

關注

1文章

54瀏覽量

14196 -

RS485接口

+關注

關注

2文章

62瀏覽量

14557

原文標題:串聯電阻R與半導體ESD電路布線與防浪涌關系

文章出處:【微信號:上海雷卯電磁兼容,微信公眾號:上海雷卯電磁兼容】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

串聯電阻R與半導體ESD電路布線中,哪個應放置靠近被保護IC?

串聯電阻R與半導體ESD電路布線中,哪個應放置靠近被保護IC?

評論