如果你曾看過VexRSICV的設(shè)計(jì),對于從事邏輯設(shè)計(jì)的你會(huì)驚訝從未想過邏輯設(shè)計(jì)還能這么來做。針對VexRSICV所衍生出的pipeline Lib,該系列會(huì)對pipeline進(jìn)行一次梳理。誠如之前一篇博客曾講,這是“勇者的游戲”。

雖然并未從事CPU設(shè)計(jì),但這里pipeline的庫讀完還是當(dāng)浮一大白~

》傳統(tǒng)的設(shè)計(jì)思路

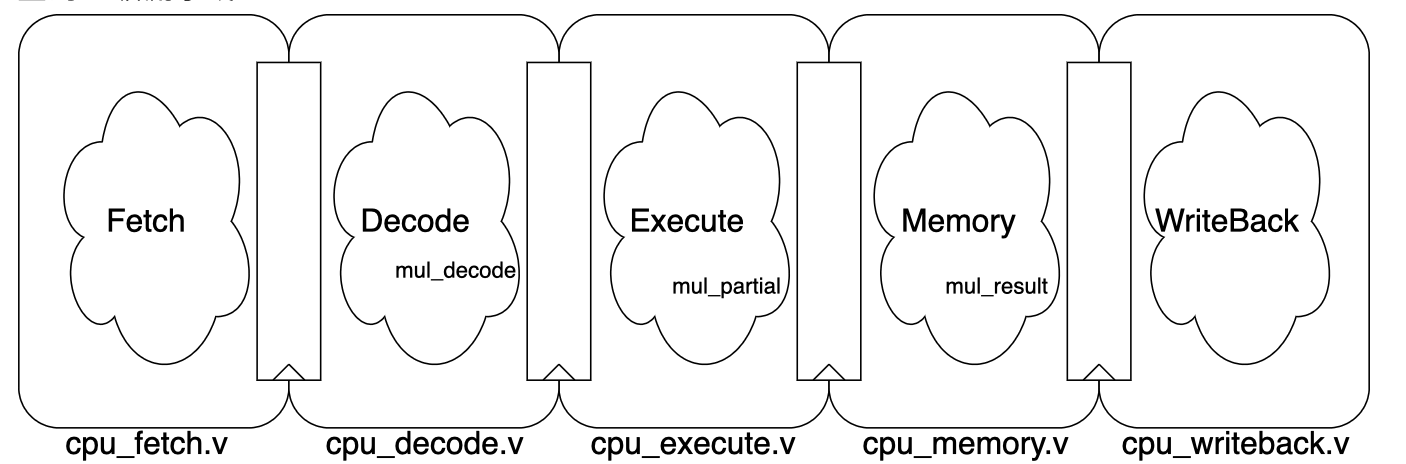

借用博客《The VexRiscV CPU - A New Way to Design》中的觀點(diǎn),在CPU設(shè)計(jì)里,一條典型的五級流水線:

在傳統(tǒng)的流水線設(shè)計(jì)里,一條指令切分到不同的Stage中,每增加一條指令,我們可能就需要對各個(gè)Stage進(jìn)行修改,牽一發(fā)而動(dòng)全身。如果對于流水線每個(gè)階段都了然于胸,那么自不是問題,否則那就是噩夢級別的難度了~。

那么,是否有新的方式來做一次流水線設(shè)計(jì)的創(chuàng)新呢?

來看看SpinalHDL里pipeline的設(shè)計(jì)思路。

》高端操作

本篇為開篇系列,先從整體架構(gòu)上看SpinalHDL中pipeline的設(shè)計(jì)整體框架,暫不牽涉具體的設(shè)計(jì)細(xì)節(jié)。

我們先來看一個(gè)非常簡單的“pipeline”:

從A到B經(jīng)歷三級流水線,每經(jīng)一級加一輸出至下一級。

回到電路設(shè)計(jì)的本質(zhì)。在FPGA里面,除了RAM、DSP這些資源,邏輯實(shí)現(xiàn)的核心只有LUT喝Reg。LUT負(fù)責(zé)實(shí)現(xiàn)邏輯實(shí)現(xiàn),Reg負(fù)責(zé)狀態(tài)保存。在上面的三級流水里,我們要思索的無非兩個(gè)問題:

- 每一級流水線都做了什么

- 流水線各級是如何進(jìn)行連接的

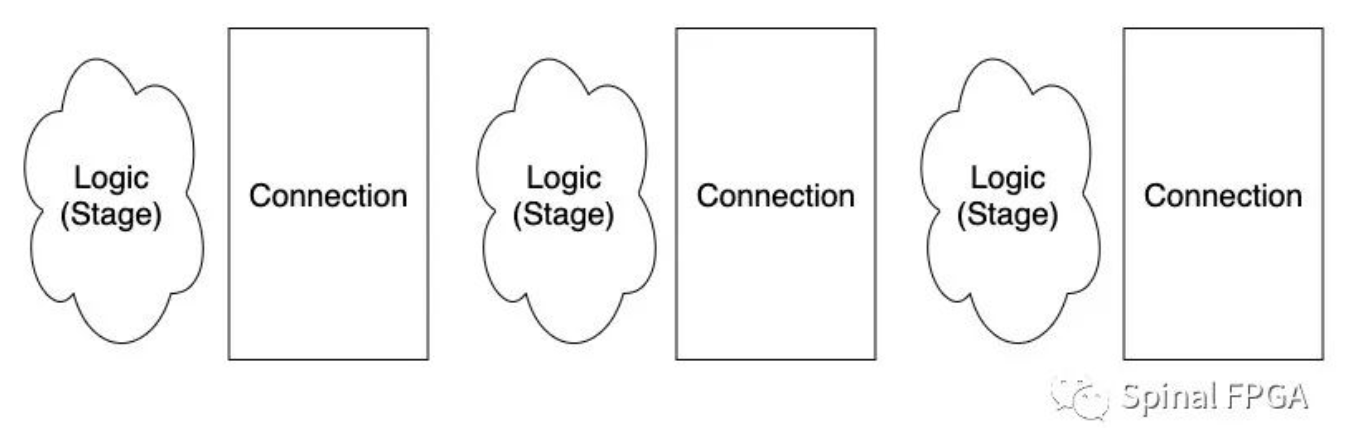

那么在看看上面的電路。每級流水線里面都是一個(gè)加法器和一個(gè)寄存器輸出。加法器這些功能性的實(shí)現(xiàn)才是每一級Stage的功能。而寄存器則用于連接本級Stage與下一級Stage。也就意味著,每一級流水線都是邏輯電路負(fù)責(zé)實(shí)現(xiàn)功能,時(shí)序電路寄存器用于Stage連接。為此,對于pipeline我們可以抽象為下面的要素:

Stage:僅考慮具體的功能實(shí)現(xiàn),它包含了輸入、輸出以及具體的邏輯實(shí)現(xiàn)。

Connection:僅用于實(shí)現(xiàn)各級Stage的連接。

在邏輯電路設(shè)計(jì)里,不要總是想著把功能實(shí)現(xiàn)和時(shí)序設(shè)計(jì)給拼到一塊兒。將上面的概念與最上面的三級流水對照,那么加法器就是對應(yīng)的Stage的功能,一個(gè)組合電路。而寄存器就對應(yīng)Connection的功能。

SpinalHDL是基于Scala而設(shè)計(jì),其能夠幫助我們自動(dòng)實(shí)現(xiàn)很多功能。比如兩級Stage之間都有哪些信號是要通過Connection進(jìn)行連接,對應(yīng)的流水線功能如flush、halt能功能如何在各級Stage之間進(jìn)行傳播等功能。我們所需要做的,就是通過一定的規(guī)則告訴pipeline如何去做這些事情。

接下來,先針對pipeline所涉及的Pipeline、Stage、Connection、Stageable、StageableKey進(jìn)行一個(gè)初步整體了解。

-

時(shí)序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

21869 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30595 -

Pipeline

+關(guān)注

關(guān)注

0文章

29瀏覽量

9614 -

FPGA開發(fā)板

+關(guān)注

關(guān)注

10文章

124瀏覽量

31865 -

HDL語言

+關(guān)注

關(guān)注

0文章

48瀏覽量

9096

發(fā)布評論請先 登錄

SpinalHDL里pipeline的設(shè)計(jì)思路

怎樣使用SpinalHDL Pipeline組件里的resulting及overloaded?

SpinalHDL里pipeline的設(shè)計(jì)思路

SpinalHDL里pipeline的設(shè)計(jì)思路

評論