差分信號的概念

差分信號,英文名稱為differential Signal,是現在很常見的傳輸方式,在PCB板子上很容易見到。

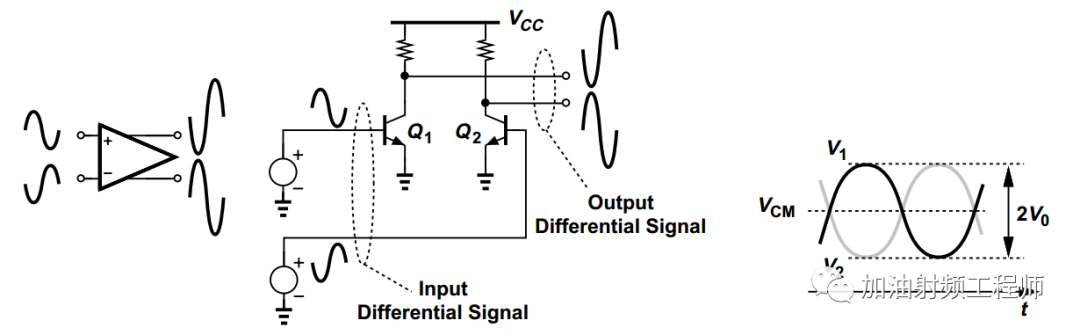

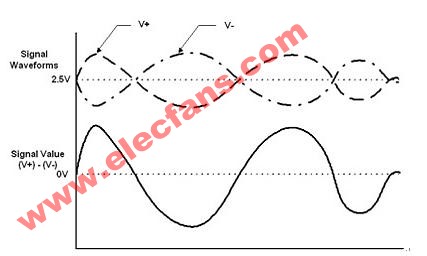

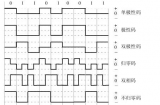

它使用兩條傳輸線路,傳輸變化幅度相等,相位反相的兩路信號,兩路信號通常還會有一個相等的直流電平。

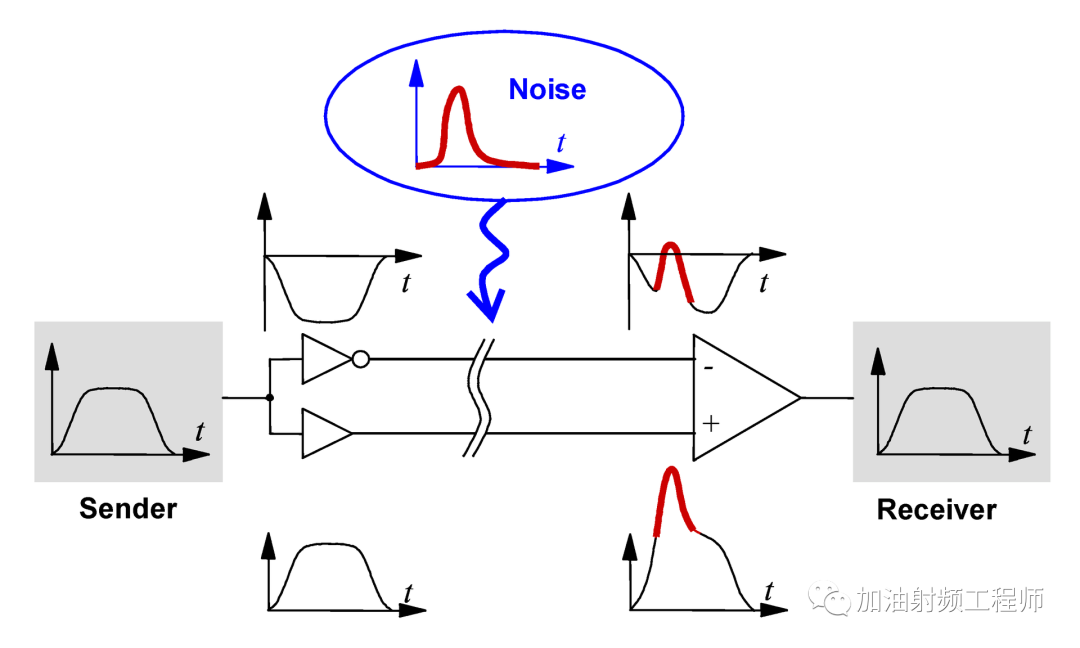

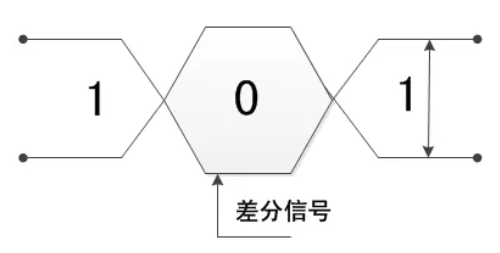

和單端信號相比,差分信號可以大幅度提高信號傳輸過程中的抗干擾能力。因為環境噪聲或者干擾信號會同時影響到兩路差分信號,而因為在接收端,響應的是兩路信號的差值,對共模噪聲有抑制作用,所以這些噪聲或者干擾在接收端會抵消。如下圖所示。

差分信號的優缺點

差分信號具有以下優點:

(1) 抗干擾能力強。

這點上面也有提及,即共模噪聲或者干擾信號,都會同時施加到兩根信號線上,其差值為0。差分系統的接收端只對信號之間的差值響應,所以噪聲不會對差分信號產生影響。

(2) 減少對外界的干擾。

因為兩路差分線靠的很近,且信號幅值相等,相位相反,所以兩者產生的電磁場有一部分會相互抵消,減少對外界的干擾。

(3) 時序定位準確。

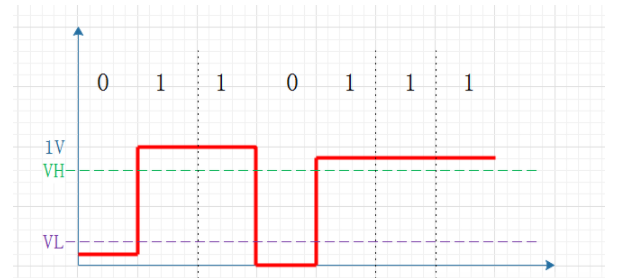

差分信號是以兩路信號幅值之差發生正負跳變的點作為判別依據的,而單端信號是以閾值電壓作為判別依據的。所以差分信號適合低幅度的傳輸。

比如,常用到差分接口信號LVDS,其信號幅度范圍為250mV~400mV,常用到的LVCMOS接口信號,一般幅度為1.8V或者3.3V。

差分信號也有如下缺點:

(1) 差分信號與單端信號相比,要多走一根線,增加了PCB的面積。

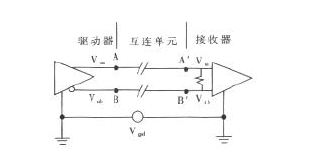

(2) 布線的時候,對兩根線的對稱性要求很高,否則會降低噪聲抑制的效果。

(3) 測試的時候,也要比單端信號的測試繁瑣。

差分信號的實現

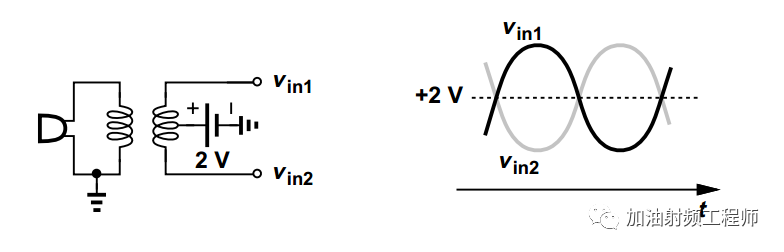

那怎樣把單端信號變成差分信號呢,最簡單的方法,就是用變壓器,如下圖所示。這也是ADC前端經常用到的電路拓撲結構。

審核編輯:湯梓紅

-

pcb

+關注

關注

4347文章

23391瀏覽量

406063 -

lvds

+關注

關注

2文章

1096瀏覽量

67012 -

共模噪聲

+關注

關注

1文章

56瀏覽量

10975 -

差分信號

+關注

關注

4文章

387瀏覽量

28086

原文標題:簡單說說差分信號

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

差分信號線的原理和優缺點分析

差分信號的優缺點以及布線要求

差分信號的優缺點及布線要求

差分信號的概念和優缺點

差分信號的概念和優缺點

評論